книги / Надежность и диагностика компонентов инфокоммуникационных и информационно-управляющих систем

..pdf

ТЕМА 13. СИНХРОННОЕ МОДЕЛИРОВАНИЕ ЦИФРОВЫХ УСТРОЙСТВ

Данная тема посвящена решению прямой задачи диагноза – определению выходов схемы по значениям входов. В качестве модели объекта будем использовать структурно-логическую модель, в качестве модели дефекта – константную модель.

Синхронное моделирование используется, когда необходимо установить влияние задержек при распространении сигнала по различным ветвям схемы. Синхронное моделирование является частным случаем асинхронного моделирования при допущении, что задержки всех элементов автомата одинаковы, а задержки связей нулевые. При асинхронном моделировании эти ограничения снимаются, т.е. допускается произвольный разброс задержек. Для простоты изложения мы рассматриваем только синхронное моделирование автоматов.

На рис. 13.1 представлена схема И, оба входа которой меняются, первый с 0 на 1, второй с 1 на 0 соответственно. Обычно при моделировании время переключения входов не учитывается, поэтому выход схемы не изменится и будет равен 0. Однако если на первом входе изменение с 0 на 1 произойдет раньше, чем изменение с 1 на 0 на втором входе, то на выходе элемента И появится кратковременный импульс – 0/1/0.

Синхронное тактирование помогает избежать нарушений в работе схемы. Однако неисправности, искажая связи между элементами в схемах с памятью, могут привести в подобных случаях к непредусмотренным срабатываниям элементов памяти (если автомат рассматривать как асинхронный с непрерывным временем). Следовательно, при моделировании неисправностей необходимы дополнительные усилия по выявлению таких ситуаций.

101

Допустим, что задержки всех вентилей схемы одинаковы и равны одному временному шагу моделирования. В этом случае говорят о синхронном моделировании. В случае синхронного моделирования вычисление значений сигналов выполняется простой итерацией. Каждой линии схемы поставим в соответствие две переменные. Первая представляет значение сигнала в текущий момент, а вторая – в следующий. Значение выхода каждого элемента вычисляется на основании значений его входных сигналов в текущий момент, а результат фиксируется в переменной следующего момента времени. На следующем шаге итерации значение второй переменной сначала переносится в первую, а потом пересчитывается заново. Процесс моделирования заканчивается, когда значения выходов перестают изменяться либо когда схема войдет в режим генератора.

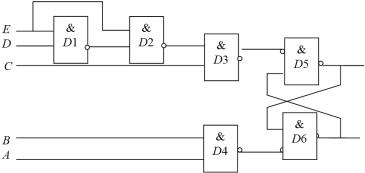

Пример 1. На рис. 13.2 приведен пример синхронного моделирования. В каждой клетке табл. 13.1 axi /bxi t означает состояние ли-

нии схемы (см. рис. 13.2) в настоящий / следующий моменты времени. Состояние входа Е меняется с 0 на 1. Схема с памятью, поэтому обязательно приводится начальное состояние.

Рис. 13.2. Пример синхронного моделирования

Рассмотрим процесс моделирования. Для каждой очередной итерации в левую колонку переписываются значения, полученные на предыдущем шаге итерации. Именно они и берутся для

102

расчета значения элемента в следующий момент времени. В правую колонку записываются результаты расчета. В первой итерации в левую колонку переписываются начальные значения, однако входы меняются сразу, поскольку, согласно модели, на линиях задержка отсутствует, что мы и видим на входе Е.

Таблица 13.1

Таблица моделирования

Начальное |

|

|

|

|

|

|

состояние |

1 |

2 |

3 |

4 |

5 |

|

E |

0 |

1/1 |

1/1 |

1/1 |

1/1 |

1/1 |

D |

1 |

1/1 |

1/1 |

1/1 |

1/1 |

1/1 |

C |

1 |

1/1 |

1/1 |

1/1 |

1/1 |

1/1 |

B |

0 |

0/0 |

0/0 |

0/0 |

0/0 |

0/0 |

A |

1 |

1/1 |

1/1 |

1/1 |

1/1 |

1/1 |

D1 |

1 |

1/0 |

0/0 |

0/0 |

0/0 |

0/0 |

D2 |

1 |

1/0 |

0/1 |

1/1 |

1/1 |

1/1 |

D3 |

0 |

0/0 |

0/1 |

1/0 |

0/0 |

0/0 |

D4 |

1 |

1/1 |

1/1 |

1/1 |

1/1 |

1/1 |

D5 |

0 |

0/0 |

0/0 |

0/1 |

1/0 |

0/0 |

D6 |

1 |

1/1 |

1/1 |

1/1 |

1/1 |

1/1 |

Элемент D1 меняет свое состояние, поскольку теперь на его входы подаются две единицы, и мы записываем этот ноль в правую колонку. Элемент D2 своего значения не меняет, поскольку изменение значения элемента D1 в первой итерации на нем не отразится из-за задержки в элементе D1 на один такт. На остальных элементах изменение выхода элемента D1 также не отразится.

Для второй итерации в левую колонку переписывается правая колонка первой итерации, и процесс повторяется.

Процесс моделирования заканчивается на пятой итерации, поскольку значения в текущий момент стали равны значению в следующий момент (т.е. левая колонка стала равна правой) для всех элементов. Из табл. 13. 1 мы видим, что на третьем элементе появилась кратковременная единица (на втором и третьем шаге итерации), в результате чего на RS-триггере D5–D6 появилась запрещен-

103

ная комбинация – единицы по обоим входам. Но элемент 4 все время находился в 1, поэтому кратковременная 1 на третьем элементе не привела в незапланированному переключению триггера.

Пример 2. Промоделируем схему рис. 13.2, считая, что на линии, связывающей элементы 4 и 6, имеется дефект типа константы 0, т.е. выход элемента D4 при любом значении его входов будет равен 0. Получим табл. 13.2.

Таблица 13.2

Пример синхронного моделирования с дефектом

Начальное |

|

|

|

|

|

|

состояние |

1 |

2 |

3 |

4 |

5 |

|

E |

0 |

1/1 |

1/1 |

1/1 |

1/1 |

1/1 |

D |

1 |

1/1 |

1/1 |

1/1 |

1/1 |

1/1 |

C |

1 |

1/1 |

1/1 |

1/1 |

1/1 |

1/1 |

B |

0 |

0/0 |

0/0 |

0/0 |

0/0 |

0/0 |

A |

1 |

1/1 |

1/1 |

1/1 |

1/1 |

1/1 |

D1 |

1 |

1/0 |

0/0 |

0/0 |

0/0 |

0/0 |

D2 |

1 |

1/0 |

0/1 |

1/1 |

1/1 |

1/1 |

D3 |

0 |

0/0 |

0/1 |

1/0 |

0/0 |

0/0 |

D4 |

1 |

0/0 |

0/0 |

0/0 |

0/0 |

0/0 |

D5 |

0 |

0/0 |

0/0 |

0/1 |

1/0 |

0/1 |

D6 |

1 |

1/1 |

1/1 |

1/1 |

1/0 |

0/1 |

Процесс моделирования окончился на пятой итерации, поскольку схема вошла в режим генератора (на D5 и D6 попеременно появляются единицы и нули). Напомним, что технология синхронного моделирования считает все задержки одинаковыми. В реальной схеме это обычно не так, и при асинхронном моделировании, когда задержки разные, RS-триггер переключился бы в противоположное состояние.

Тем не менее синхронное моделирование позволило определить, что при заданной неисправности схема ведет себя не так, как при отсутствии неисправностей.

104

Варианты заданий для самостоятельных и расчетных работ

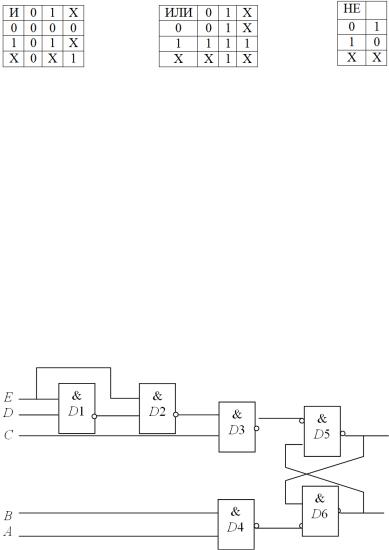

Задание: промоделировать схему рис. 13.3–13.6 при отсутствии неисправности и при наличии заданной неисправности. Просмотреть таблицу моделирования, отметить наличие или отсутствие незапланированных кратковременных импульсов и сделать вывод о том, к каким результатам это приводит.

Рис. 13.3. Схема с памятью, вариант 1

Рис. 13.4. Схема с памятью, вариант 2

105

Рис. 13.5. Схема с памятью, вариант 3

Рис. 13.6. Схема с памятью, вариант 4

1.Рис. 13.3. Константа 1 на линии между входом А и элементом D1.

2.Рис. 13.4. Константа 0 на линии между входом А и элементом D1.

3.Рис. 13.5. Константа 1 на линии между входом C и элементом D3.

4.Рис. 13.6. Константа 0 на линии между входом C и элементом D3.

5.Рис. 13.3. Константа 1 на линии между входом E и элементом D5.

106

6.Рис. 13.4. Константа 0 на линии между входом E и элементом D5.

7.Рис. 13.5. Константа 1 на линии между входом А и элементом D2.

8.Рис. 13.6. Константа 0 на линии между входом А и элементом D2.

9.Рис. 13.3. Константа 1 на линии между входом C и элементом D4.

10.Рис. 13.4. Константа 0 на линии между входом C и элементом D4.

11.Рис. 13.5. Константа 1 на линии между входом E и элементом D6.

12.Рис. 13.6. Константа 0 на линии между входом E и элементом D6.

13.Рис. 13.3. Константа 0 на линии между входом B и элементом D1.

14.Рис. 13.4. Константа 0 на линии между входом D и элементом D3.

15.Рис. 13.5. Константа 0 на линии между входом F и элементом D5.

16.Рис. 13.6. Константа 1 на линии между элементами D1 и D2.

17.Рис. 13.3. Константа 0 на линии между элементами D1 и D2.

18.Рис. 13.4. Константа 1 на линии между элементами D3 и D4.

19.Рис. 13.5. Константа 0 на линии между элементами D3 и D4.

20.Рис. 13.6. Константа 1 на линии между элементами D5 и D6.

21.Рис. 13.3. Константа 0 на линии между элементами D5 и D6.

22.Рис. 13.4. Константа 1 на линии между элементами D2 и D7.

23.Рис. 13.5. Константа 0 на линии между элементами D2 и D7.

24.Рис. 13.6. Константа 1 на линии между элементами D4 и D7.

В данной теме рассматривалось синхронное моделирование исправной схемы, а также синхронное моделирование схем с неисправностью. Схема задается на структурно-логическом уровне, модель дефекта – константная неисправность.

107

ТЕМА 14. СИНХРОННОЕ МОДЕЛИРОВАНИЕ ДЛЯ ОПРЕДЕЛЕНИЯ КРИТИЧЕСКИХ СОСТЯЗАНИЙ

Данная тема продолжает предыдущую. Мы видели на простейшем примере, как из-за произвольного распределения задержек на входе комбинационного элемента И на выходе этого элемента могут появиться непредусмотренные кратковременные импульсы. Эти импульсы могут повлиять на поведение схемы, а могут и не повлиять. Критическими состязаниями называется такое распределение задержек в схеме, которое может повлиять на поведение схемы и вызвать неверную реакцию автомата.

Как мы видели, синхронное моделирование не может работать с произвольным распределением задержек, так как предполагает, что задержки во всех элементах совершенно одинаковые. Это приводит иногда к нелогичным результатам. Так, RS-триггер

впримере 2 предыдущей темы при подаче на входы запрещенного набора (двух единиц), а потом сохраняющего набора (двух нулей) повел себя как генератор.

Существует методика троичного моделирования, которая для выявления критических состязаний использует расширенный алфавит моделирования.

Под алфавитом моделирования будем понимать множество значений, принимаемых сигналами в модели схемы. Символами «0» и «1» будем обозначать установившиеся значения сигналов логической схемы, а символом «Х» – неопределенное значение сигнала. Неопределенным может быть начальное состояние схемы или неопределенным может оказаться внутреннее состояние в результате непредсказуемого перехода автомата. Рассмотренный троичный алфавит и правила троичного моделирования впервые были предложены Эйхельбергером, американским специалистом

вобласти технической диагностики дискретных устройств.

При троичном моделировании таблицы истинности основных логических функций выглядят следующим образом:

108

Техника моделирования та же, что и в предыдущем случае, однако при изменении сигнала на каком-либо входе в середину добавляется Х – 0/Х/1 либо 1/Х/0, что и позволяет учесть разброс во временных параметрах входных сигналов. Если после окончания моделирования на выходах элементов не остается ни одного неопределенного состояния, значит, критические состязания в данном случае невозможны, и наоборот.

Пример 1. На рис. 14.1 приведен пример моделирования исправной схемы для обнаружения критических состязаний. В результате моделирования получаем табл. 14.1.

Моделирование заканчивается на пятом такте итерации, когда состояния элементов перестают изменяться. По окончании моделирования на выходах всех элементов значения определены, значит, критические состязания в данной ситуации невозможны.

Рис. 14.1. Пример троичного синхронного моделирования асинхронного автомата, не содержащего константных дефектов, для обнаружения критических состязаний сигналов из-за неблагоприятного разброса задержек

109

|

|

|

|

|

|

|

|

Таблица 14.1 |

|

|

|

Таблица моделирования |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

Начальное |

|

|

|

|

|

|

|

|

|

состояние |

|

1 |

2 |

3 |

|

4 |

5 |

|

|

E |

0 |

|

Х/1 |

1/1 |

1/1 |

|

1/1 |

1/1 |

|

D |

1 |

|

1/1 |

1/1 |

1/1 |

|

1/1 |

1/1 |

|

C |

1 |

|

1/1 |

1/1 |

1/1 |

|

1/1 |

1/1 |

|

B |

0 |

|

0/0 |

0/0 |

0/0 |

|

0/0 |

0/0 |

|

A |

1 |

|

1/1 |

1/1 |

1/1 |

|

1/1 |

1/1 |

|

D1 |

1 |

|

1/Х |

Х/0 |

0/0 |

|

0/0 |

0/0 |

|

D2 |

1 |

|

1/Х |

Х/Х |

Х/1 |

|

1/1 |

1/1 |

|

D3 |

0 |

|

0/0 |

0/Х |

Х/Х |

|

Х/0 |

0/0 |

|

D4 |

1 |

|

1/1 |

1/1 |

1/1 |

|

1/1 |

1/1 |

|

D5 |

0 |

|

0/0 |

0/0 |

0/Х |

|

Х/Х |

Х/0 |

|

D6 |

1 |

|

1/1 |

1/1 |

1/1 |

|

1/1 |

1/1 |

|

Пример 1. Промоделируем схему рис. 14.1, считая, что на линии, связывающей элементы 4 и 6, имеется дефект типа константа 0, т.е. выход элемента D4 при любом значении его входов будет равен 0.

Таблица 14.2

Пример моделирования схемы с неисправностями для обнаружения критических состязаний

Начальное |

|

|

|

|

|

|

состояние |

1 |

2 |

3 |

4 |

5 |

|

E |

0 |

Х/1 |

1/1 |

1/1 |

1/1 |

1/1 |

D |

1 |

1/1 |

1/1 |

1/1 |

1/1 |

1/1 |

C |

1 |

1/1 |

1/1 |

1/1 |

1/1 |

1/1 |

B |

0 |

0/0 |

0/0 |

0/0 |

0/0 |

0/0 |

A |

1 |

1/1 |

1/1 |

1/1 |

1/1 |

1/1 |

D1 |

1 |

1/Х |

Х/0 |

0/0 |

0/0 |

0/0 |

D2 |

1 |

1/Х |

Х/Х |

Х/1 |

1/1 |

1/1 |

D3 |

0 |

0/0 |

0/Х |

Х/Х |

Х/0 |

0/0 |

D4 |

1 |

0/0 |

0/0 |

0/0 |

0/0 |

0/0 |

D5 |

0 |

0/0 |

0/0 |

0/Х |

Х/Х |

Х/Х |

D6 |

1 |

1/1 |

1/1 |

1/1 |

1/Х |

Х/Х |

110