- •Структура и функционирование процессоров PowerPC

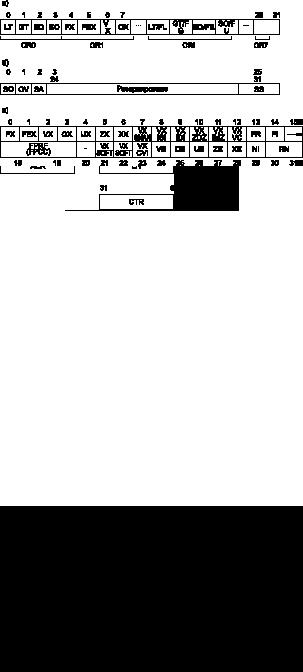

- •Рис. 1. Структура процессоров семейства PowerPC

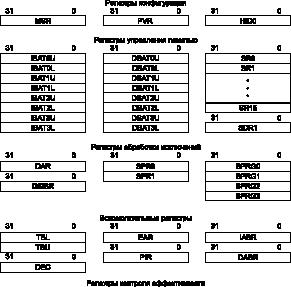

- •Рис. 2. Регистровая модель пользователя процессоров PowerPC

- •Рис. 3. Форматы содержимого регистров CR, XER, FPSCR

- •Таблица 1. Виды и относительные адреса векторов исключений

- •Способы адресации и система команд

- •Номенклатура и применение процессоров PowerPC

И. Шагурин

RISC-процессоры PowerPC

RISC-архитектура широко используется во многих современных микропроцессорах и микроконтроллерах, выпускаемых различными компаниями. Первые RISC-процессоры, разработанные в Стенфордском и Калифорнийском университетах США в начале 80-х годов, выполняли относительно небольшой набор команд — 50–100 вместо 100–200, выполняемых обычными CISC (Complex Instruction Set computer — компьютер со сложным набором команд) процессорами. Эта особенность определила название данного класса процессоров — RISC (Reduced Insruction Set Computer — компьютер с сокращённым набором команд). Однако в последующих разработках RISC-процессоров набор команд значительно расширен, включая команды обработки чисел с плавающей точкой. В настоящее время определились следующие характерные особенности современных RISCпроцессоров:

расширенный объём регистровой памяти: от 32 до нескольких сотен регистров общего назначения, входящих в состав микропроцессора; использование в командах обработки данных только регистровой адресации (обращение к

памяти используется в командах загрузки и сохранения содержимого регистров, а также в командах управления программой); отказ от аппаратной реализации сложных способов адресации (с постинкрементом или

предекрементом, косвенная адресация и др.); фиксированный формат команд (обычно 4 байт) вместо переменного формата (от 1 до 15 байт), характерного для CISC-процессоров;

исключение из набора команд, реализующих редко используемые операции, а также команд, не вписывающихся в принятый формат.

Преимущественное использование регистровой адресации значительно повышает производительность микропроцессоров. Фиксированный формат команд, отказ от сложных и редко используемых команд и способов адресации существенно упрощает устройство управления, сокращает объём микропрограммной памяти, что позволяет уменьшить размер кристалла RISCпроцессоров, снизить их стоимость и повысить тактовую частоту. Введение фиксированного формата команд обеспечивает также более эффективную работу исполнительного конвейера, уменьшает число тактов простоя и ожидания, что даёт дополнительный рост производительности.

Перечисленные достоинства RISC-процессоров определили значительный интерес к этим изделиям. В настоящее время данный вид СБИС выпускают практически все ведущие производители микропроцессорной техники — Motorola, Intel, Hewlett-Packard, IBM и другие, а также ряд компаний, специализирующихся в этой области: Sun Microsystems, MIPS.

В последние годы широкую популярность получили RISC-процессоры и RISC-контроллеры семейства PowerPC. Начало созданию этого семейства было положено в октябре 1991 года, когда компании IBM, Motorola и Apple Computers объявили об организации консорциума для совместной разработки и внедрения RISC-микропроцессоров новой архитектуры. Их прототипом был выбран процессор Power, используемый в широко распространённой рабочей станции RS/6000, которая выпускалась компанией IBM. Для решения этой задачи были сделаны крупные инвестиции (около 1 миллиарда долларов) и построен новый центр проектирования в г. Остин (Техас), открытый в мае 1992 года. Штат центра составили 300 ведущих специалистов из компаний IBM и Motorola, в результате работы которых уже в октябре 1992 года были получены первые образцы 32-разрядных RISCмикропроцесоров типа PowerPC 601, а с апреля 1993 года начался их серийный выпуск. В ноябре 1993 года началось производство следующей модели — PowerPC 603, предназначенной для использования в портативных компьютерах. В апреле 1994 года была выпущена более производительная модель PowerPC 604. В настоящее время серийно выпускаются модификации моделей PowerPC 603, 604 с тактовой частотой до 350 МГц. Разработана новая ветвь этого семейства — PowerPC 7xx, выпуск которой начат в 1997 году. В её состав входят модели MPC740,750 с тактовой частотой до 400 МГц.

На базе микропроцессоров семейства PowerPC реализованы десятки типов компьютеров, серверов и других цифровых систем различного назначения. Эти микропроцессоры послужили основой для создания новых семейств микроконтроллеров MPC5xxx и коммуникационных контроллеров MPC8xx.

Все процессоры семейства PowerPC имеют суперскалярную структуру, которая содержит от 4 до 6 параллельно работающих исполнительных устройств, обеспечивающих одновременное выполнение нескольких команд. В данной статье описывается архитектура и функционирование процессоров PowerPC на примере наиболее производительной 32-разрядной модели MPC604e и даётся обзор основных характеристик других моделей этого семейства.

Структура и функционирование процессоров PowerPC

Процессор имеет суперскалярную структуру (рис. 1), которая содержит шесть параллельно работающих исполнительных устройств: блок предсказания ветвлений BPU, два устройства для выполнения простых целочисленных операций SIU1 и SIU2, одно устройство для выполнения сложных целочисленных операций MIU, устройство обработки чисел с плавающей точкой FPU и блок обращения к внешней памяти LSU. При этом обеспечивается одновременное выполнение четырёх команд. Все операции обработки данных выполняются с регистровой адресацией. При этом для хранения целочисленных операндов используются тридцать два 32-разрядных регистра GPR0-31, а для хранения операндов с плавающей точкой — тридцать два 64-разрядных регистра FPR0-31. Выборка данных из памяти производится только командами пересылки, которые выполняются блоком LSU и осуществляют загрузку данных в регистры GPR и FPR или запись их содержимого в память.

Рис. 1. Структура процессоров семейства PowerPC

При параллельной работе исполнительных устройств возможно их одновременное обращение к одним регистрам. Чтобы избежать ошибок, возникающих при этом в случае записи нового содержимого до того, как другим устройством будет считано предыдущее, введены буферные регистры — 12 для GPR, 8 для FPR. Эти регистры служат для промежуточного хранения операндов, дублируя регистры GPR, FPR и используемые при выполнении текущих операций. После завершения операций производится перезапись полученных результатов в GPR, FPR (обратная запись).

Конвейер выполнения команд имеет шесть основных каскадов: выборка команды (1) и её дешифрация (2), распределение команд по исполнительным устройствам (3), выполнение команд (4), запись результатов в буфер (5) и обратная запись результатов в регистры SPR или FPR (6). Устройство управления одновременно выбирает из кэша и декодирует четыре команды, которые распределяются в соответствующие исполнительные устройства. Большинство команд выполняется за один такт. Эти команды реализуются с помощью SIU1 и SIU2, которые осуществляют сложение, вычитание, сравнение, сдвиги и логические операции. Выполнение ряда команд требует нескольких тактов. Например, целочисленное умножение осуществляется за 3–4 такта, деление — за 20 тактов. Эти операции производятся MIU. Большинство операций с плавающей точкой (кроме деления) выполняется за 3 такта, поэтому во внутренней структуре FPU реализовано три исполнительных каскада. Блок завершения обеспечивает получение правильной по-следовательности результатов выполняемых операций. Он содержит буферную память типа очереди, в которую по мере поступления записываются результаты, получаемые от исполнительных устройств. Обратная запись результатов из буфера в регистры GPR и FPR производится в соответствии с порядком поступления команд, выбираемых устройством управления, то есть восстанавливается необходимая последовательность результатов.

Блок обработки ветвлений BPU предсказывает направление ветвления программы при поступлении соответствующих команд. В процессорах семейства PowerPC реализуются два механизма предсказания: статическое, которое даётся программистом и содержится в тексте выполняемой

программы, и динамическое, которое выполняется BPU по результатам предыдущих ветвлений. Блок BPU использует для предсказания кэш-адресов ветвлений BTAC и таблицу истории ветвлений BHT. Кэш BTAC хранит 64 адреса ветвлений, выполнявшихся предыдущими командами. Если поступившая команда ветвления содержит адрес, совпадающий с одним из имеющихся в BTAC, то процессор предсказывает ветвление по этому адресу и выбирает команды из соответствующей ветви в конвейер (ветвление выполняется). Если адрес ветвления не содержится в BTAC, то выбирается следующая команда программы (ветвление отсутствует).

При поступлении команд условных ветвлений BPU анализирует таблицу BHT, которая представляет собой кэш-память, где содержатся 512 адресов предыдущих условных ветвлений. Для каждого адреса в таблице имеются два бита, определяющие вероятность ветвления по данному адресу: “00” — практически не выполняется, “01” — выполняется редко, “10” — выполняется часто, “11” — выполняется очень часто. Значения этих битов меняются после каждой операции ветвления: если производится ветвление по данному адресу, то вероятность увеличивается на 1 (максимальное значение “11”), если данный адрес не использован, то вероятность уменьшается на 1 (минимальное значение “00”). Новые адреса вводятся в BHT вместо адресов с нулевой вероятностью. Ветвление по имеющемуся в таблице адресу предсказывается, если его вероятность больше “01”. Правильность предсказания проверяется после определения соответствующих признаков в регистре условий CR. Если условия не выполняются (неправильное предсказание), то процессор освобождает конвейер от команд из неправильно выбранной ветви, и загружает новые команды из другой ветви. Таким образом, при неправильных предсказаниях требуется перезагрузка конвейера, что снижает производительность процессора.

Так как одновременно могут выполняться несколько команд, изменяющих значения признаков в регистре CR, то в BPU имеются восемь буферных регистров, дубли-рующих содержимое CR. Эти регистры используются различными исполнительными устройствами, а после завершения операций их содержимое переносится в основной регистр условий CR (обратная запись), обеспечивая правильный порядок выполнения условных команд.

Процессор осуществляет раздельную выборку команд и данных с помощью двух устройств управления памятью IMMU и DMMU, которые могут выполнять сегментную, страничную и блочную адресацию. Внутренние кэши команд IC и данных DC имеют ёмкость по 16 Кбайт.

Контроллер шины BIU обеспечивает интерфейс процессора с внешними устройствами. Системная шина передает 32-разрядный адрес A0-31 и 64-разрядные данные. Для каждого байта адреса и данных передаются и принимаются биты чётности, с помощью которых осуществляется контроль ошибок при обращении к шине. Увеличенная разрядность шины данных позволяет быстрее производить загрузку строк кэш-памяти, которые содержат по 32 байта. При кэш-промахе производится пакетная передача данных, которая обеспечивает пересылку строки за 4 последовательных цикла. Контроллер BIU реализует выдачу и приём необходимых сигналов для управления обменом, выполнения прерываний, захвата шин, снупинга (обращения внешнего устройства к внутреннему кэшу данных), установки начального состояния (Reset).

Процессор содержит специализированный последовательный тест-порт TAP для выполнения тестирования по стандарту JTAG (IEEE 1149.1).

Для питания процессора используется напряжение 3,3 В для схем ввода/вывода, принимающих и выдающих внешние сигналы, и 2,5 В для схем внутренней структуры. При тактовой частоте Ft = 350 МГц типовое значение потребляемой мощности для процессора MPC604e составляет 8 Вт. Пониженное энергопотребление (400 МВт) обеспечивается при останове процессора, который осуществляется программно путём установки в регистре MSR значения бита POW=1. В этом случае прекраща-ется выполнение команд, продолжают работать только базовый таймер TB, регистр декремента DEC и блок обслуживания запросов прерывания. Процессор устанавливает выходной сигнал HALTED=1, информируя о своём останове внешние устройства. Выход из этого состояния происходит при запросе периодического прерывания от регистра DEC, при поступлении внешних сигналов прерывания INT#, MCP#, SMI# или начальной установки RESET#.

В процессорах PowerPC реализован принцип выделения отдельных ресурсов для решения задач пользователя и супервизора (операционной системы). В соответствии с этим принципом архитектура PowerPC содержит регистры, входящие в модели пользователя или супервизора, а также имеет ряд привилегированных команд, выполняемых только в режиме супервизора.

Рис. 2. Регистровая модель пользователя процессоров PowerPC

В регистровую модель пользователя (рис. 2), которая является общей для всего семейства

PowerPC, входят:

тридцать два 32-разрядных регистра общего назначения GPR31-0 для хранения целочисленных операндов;

тридцать два 64-разрядных регистра FPR31-0 для хранения операндов с плавающей точкой; 32-разрядные регистры условий (признаков) CR и состояния при обработке чисел с плавающей точкой FPSR;

32-разрядные регистры XER, LR, CTR, используемые при обработке исключений.

Эта регистровая модель не содержит программного счётчика PC и указателя стека SP. Отсутствие в модели PC связано с тем, что процессоры PowerPC не выполняют команд записи или чтения программного счётчика. Эти процессоры не выполняют также операций со стеком (в случае необходимости стек реализуется программно), поэтому не содержат SP.

Рис. 3. Форматы содержимого регистров CR, XER, FPSCR

Регистр условий CR (рис. 3а) состоит из восьми 4-бит полей CR7-0. Младшее поле CR0 содержит признаки, формируемые при выполнении целочисленных операций:

LT = 1 при отрицательном результате;

GT = 1 при положительном ненулевом результате; EQ = 1 при нулевом результате;

SO — принимает значение аналогичного бита, устанавливаемое в регистре XER.

Поле CR1 содержит признаки FX, FEX, VX, OX, устанавливаемые при операциях над числами с плавающей точкой, которые принимают значения аналогичных битов в регистре FPSCR (рис. 3б). Содержимое остальных полей CR7-2 устанавливается по результату операций сравнения целых или вещественных (с плавающей точкой) чисел. При сравнении целых чисел формируются признаки LT (меньше), GT (больше), EQ (равно) и SO, назначение которых указано выше. При сравнении вещественных чисел устанавливаются аналогичные признаки FL (меньше), FG (больше), FE (равно), а также признак FU, принимающий значение FU = 1, если хотя бы один из сравниваемых операндов

является Не-числом (NAN). Наличие различных полей для признаков позволяет сохранять несколько результатов сравнения, используемых по мере необходимости.

Следует отметить, что в процессорах PowerPC принята нумерация разрядов, начиная со старшего. При этом биты A0 и D0 содержат старшие разряды, а биты A31 и D31 — младшие разряды 32разрядного слова адреса или данных. Соответственно, и содержимое регистров микропроцессора представляется в формате, начальный бит которого имеет номер “0”.

Регистр XER (рис. 3б) содержит признаки переноса CA, переполнения OV, устанавливаемые в результате выполнения арифметических целочисленных операций и признак общего переполнения SO, который сохраняет установленное при переполнении значение SO=1 до выполнения команд загрузки в регистр нового содержимого. Значение SO переносится в соответствующие биты регистра CR после каждой операции. Таким образом, признак SO=1 указывает на возникновение переполнения в ранее выполненных командах программы. Поле SS определяет число байтов (длину строк символов), пересылаемых соответствующими командами пересылки строк (см. следующий раздел).

Регистр связи LR служит для хранения адреса команды, к которой осуществляется условный или безусловный переход. При вызове подпрограммы в этот же регистр заносится адрес команды возврата. В регистр-счётчик CTR заносится число циклов, которое используется для организации программных циклов. При этом содержимое CTR уменьшается на 1 после завершения очередного цикла. Имеются также специальные команды условного ветвления, использующие содержимое CTR в качестве адреса перехода. Регистр FPSCR определяет состояние и режим работы блока обработки чисел с плавающей точкой. Отдельные биты его содержимого (рис. 3в) имеют следующее функциональное назначение:

FX — признак общего исключения FPU, принимает значение FX=1, если в регистре FPSCR установлен в “1” какой-либо из признаков исключения VX, OX, UX, ZX, XX;

FEX — признак разрешённого общего исключения FPU, принимает значение FEX=1, если хотя бы один из установленных признаков исключения разрешён для обслуживания битами VE, OE, UE, ZE, XE;

VX — общий признак исключения при выполнении неправильной операции FPU, принимает значение VX=1, если в FPSCR установлен в “1” какой-либо из признаков неправильной операции (эти признаки отмечены начальными символами VX);

OX — признак переполнения принимает значение OX=1, если результат превышает максимальную допустимую величину max;

UX — признак антипереполнения принимает значение UX=1, если результат меньше минимальной допустимой величины min;

ZX — признак деления на 0 принимает значение ZX=1 при нулевом делителе;

XX — признак неточного результата принимает значение XX=1, если произошла потеря точности при округлении (XX копирует признак FI);

VXSNAN, VXISI, VXIDI, VXZDZ, VXIMZ, VXVC, VXSOFT, VXSQRT, VXCVI — признаки неправильной операции FPU при использовании в качестве операнда Нечисла (VXSNAN=1), при вычитании или делении бесконечностей (VXISI=1 или VXIDI=1), при делении нуля на нуль (VXZDZ=1) или умножении нуля на бесконечность (VXIMZ=1), при программном вызове исключения неправильного кода команды (установка VXSOFT=1 с помощью специальных команд), попытке извлечения квадратного корня из отрицательного числа (VXSQRT=1) или неопределённом результате сравнения (VXCVI=1);

FR — признак округления принимает значение FR=1, если при выполнении команды производится округление результата;

FI — признак потери точности принимает значение FI=1, если округление вызывает потерю точности (признак FI копируется в XX);

FPRF или FPCC — поле, определяющее результат выполняемых FPU арифметических операций, округления или сравнения;

VE, OE, UE, ZE, XE — биты разрешения обслуживания исключений при выполнении неправильной операции (VE=1), переполнении (OE=1), антипереполнении (UE=1), делении на нуль (ZE=1), неточном результате (XE=1);

NI — переводит FPU при NI=1 в режим выполнения некоторых операций, не предусмотренных стандартом IEEE 754;

RN — определяет вид выполняемого округления: к ближайшему числу (RN=00), к нулю (RN=01), к ”+бесконечность” (RN=10) или к “-бесконечность” (RN=11).

При выполнении команд FPU, вызывающих изменение содержимого регистра условий CR, содержимое четырёх младших разрядов FPSCR (признаки FX, FEX, VX, OX) копируется в поле CR1 регистра CR (рис. 3а).

Признаки FX, OX, UX, ZX, XX, VXSNAN, VXISI, VXIDI, VXZDZ, VXIMZ, VXVC, VXSOFT, VXSQRT, VXCVI сохраняют установленное значение “1”, пока оно не будет изменено с помощью специальных команд. Таким образом, эти признаки хранят информацию о причинах возникших исключений, которая в дальнейшем может быть использована подпрограммой их обслуживания.

Значения битов 15–19 в регистре FPSCR (поле FPRF или FPCC) зависят от типа выполняемой команды. При арифметических операциях и операциях округления значения битов FPRF устанавливаются в соответствии с полученным результатом. При выполнении команд сравнения биты 16–19 (поле FPCC) принимают такие же значения, как признаки FL (меньше), FG (больше), FE (равно), FU (не сравнимо) в поле CRi регистра условий CR, номер которого i задается в команде.

Регистровая модель супервизора (рис. 4) включает в себя регистровую модель пользователя, а также содержит несколько групп служебных регистров, часть из которых являются общими для всего семейства PowerPC, а часть — специфичными для модели PowerPC 604e.

Рис. 4. Регистровая модель супервизора микропроцессора MPC604

В группе регистров конфигурации основным является регистр управления MSR, определяющий режим функционирования процессора. Биты его содержимого имеют следующее назначение (рис. 5):

POW — переводит при значении POW=1 процессор в режим отключения с пониженным потреблением мощности;

ILE — определяет порядок адресации байтов в слове при обработке исключений: начиная со старшего байта (big-endian) при ILE=0, начиная с младшего байта (little-endian) при ILE=1; EE — разрешает при EE=1 обслуживание внешних запросов прерывания и периодических прерываний от регистра декремента DEC;

PR — задаёт режим работы процессора: при PR=0 — режим супервизора, при PR=1 — пользователя;

FP — разрешает при FP=1 выполнение операций над числами с плавающей точкой;

ME, SE, BE — разрешают обслуживание внешнего запроса прерывания MCP# (при ME=1), выполнение пошаговой трассировки (при SE=1) и трассировки после команд переходов (при

BE=1);

FE0, FE1 — запрещают при FE0=FE1=0 обслуживание исключений при обработке чисел с плавающей точкой, при других значениях FE0, FE1 обеспечивают различные варианты их обслуживания;

EP — определяет базовый адрес размещения векторов исключений: $00000000 при EP=0, $FFF00000 при EP=1;

IT, DT — разрешают трансляцию адресов команд (при IT=1) и данных (при DT=1) с помощью устройств управления памятью IMMU, DMMU;

PM — задаёт режим процессора, при котором осуществляется контроль эффективности его работы;

RE — обеспечивает при RE=1 возврат к выполнению прерванной программы после повторного запуска (RESET) или обслуживания внешнего запроса прерывания MCP#;

LE — определяет порядок адресации байтов в слове: начиная со старшего байта (big-endian) при LE=0 или начиная с младшего разряда (little-endian); при переходе к обслуживанию исключений LE принимает значение ELE.

Регистр HID0 содержит биты Hi, определяющие функ-ционирование отдельных устройств процессора: разрешают или запрещают обслуживание некоторых видов прерываний, задают режим функционирования внутренней кэш-памяти, управляют работой блока предсказания ветвлений, задавая статический или динамический способ предсказания дальнейшего хода программы, запрещают параллельную работу исполнительных устройств в суперскалярной структуре процессора, обеспечивая последовательное выполнение поступающих команд.

Регистр PVR содержит код, указывающий тип процессора, который записывается в процессе изготовления и затем может только считываться.

Отдельная группа регистров используется в процессе обслуживания исключений. В эту группу входят регистры: DAR, хранящий адрес операнда, выборка которого вызвала исключение; DSISR, содержащий код команды, вызвавшей исключение; SRR0, SRR1, в которые заносятся адрес следующей команды и текущее содержимое регистра MSR для возврата к основной программе после обслуживания исключения. Процессор имеет также четыре регистра SPRG0-3, которые служат для хранения адресов, используемых подпрограммой обработки исключения.

К группе вспомогательных регистров относятся регистры декремента DEC, базового времени TB, адресов останова в контрольной точке IABR, DABR, идентификации PIR, а также регистр EAR, используемый для обращения к внешним устройствам с помощью специальных команд. Регистр DEC работает как вычитающий счётчик с частотой, равной 1/4 тактовой частоты Ft. Когда его содержимое становится равным 0, формируется запрос исключения. Таким образом, можно использовать этот регистр для реализации периодических прерываний. Регистр PIR содержит 4-разрядный код, определяющий номер процессора в мультипроцессорных системах. Таймер базового времени TB представляет собой 64-разрядный счётчик, переключающийся с частотой Ft. Его содержимое может записываться и считываться в режиме супервизора, а в режиме пользователя регистр доступен только для чтения. Регистр IABR содержит адрес команды, а регистр DABR — адрес операнда, при обращении к которым реализуется останов в контрольной точке.

В состав модели супервизора входят также регистры, которые используются для контроля эффективности работы процессора. В зависимости от значения битов PM, PR в MSR и содержимого регистра управления MMCR0, в регистры PMC1, PMC2 при работе процессора заносятся такие показатели, как число выполненных циклов, число команд, завершившихся в данном цикле, общее количество выполненных ветвлений, количество неправильно предсказанных ветвлений, число кэшпромахов и другие параметры. Общее число контролируемых параметров составляет 46. Эти данные позволяют программисту оценить эффективность программного обеспечения и оптимизировать его в процессе отладки.

Процессор обеспечивает обслуживание прерываний и исключений, виды которых указаны в табл. 1. При возникновении исключений их вектора (начальные адреса подпрограмм обслуживания) выбираются из таблицы, базовый адрес которой определяется значением бита EP в регистре MSR (рис. 5). Относительные адреса соответствующих векторов приведены в табл. 1. Отдельные виды исключений маскируются путем установки в 0 битов EE, SE, BE, ME в регистре MSR. При реализации большинства исключений в регистр SRR0 заносится адрес следующей команды программы, обеспечивающий возврат к её выполнению после обслуживания исключения, а в регистр SRR1 — текущее содержимое MSR. По-сле выполнения подпрограммы обслуживания команда возврата из исключения производит восстановление содержимого программного счётчика и регистра состояния

MSR из SRR0, SRR1.