- •Содержание

- •Задание

- •Разработка архитектуры внешних выводов

- •Выбор форматов данных

- •Определение модели памяти и структуры регистровой памяти

- •Выбор форматов команд

- •Разработка системы команд

- •Внутренняя организация

- •Структурно-функциональная схема процессора

- •Основные алгоритмы функционирования

- •Алгоритмы выполнения отдельных операций

- •Разработка алгоритмов выполнения основных операций на шине

- •Список использованной литературы

Министерство образования и науки Российской Федерации

Санкт-Петербургский государственный электротехнический университет «ЛЭТИ»

им. В.И. Ульянова (Ленина)

Факультет компьютерных технологий и информатики

Кафедра вычислительной техники

Пояснительная записка к курсовому проекту

по дисциплине «Архитектура ЭВМ»

тема: «Разработка архитектуры однокристального RISC-процессора»

Выполнил: Липанов П.В.

Проверил: Казак А.Ф.

Санкт-Петербург, 2008г.

Содержание

Содержание 2

Задание 3

Разработка архитектуры внешних выводов 5

Выбор форматов данных 7

Определение модели памяти и структуры регистровой памяти 9

Выбор форматов команд 14

Разработка системы команд 15

Внутренняя организация 19

Структурно-функциональная схема процессора 20

Основные алгоритмы функционирования 22

Алгоритмы выполнения отдельных операций 25

Разработка алгоритмов выполнения основных операций на шине 26

Выводы 28

Список использованной литературы 29

Задание

Необходимо разработать архитектуру однокристального RISC-процессора общего назначения, предназначенного для использования в качестве центрального процессора (ЦП) рабочей станции, ориентированной на работу в многопользовательском режиме. Необходимо предусмотреть механизмы работы с виртуальной памятью, а также работу в многозадачном режиме. Процессор ориентирован на работу с ОСUNIX.

Перечень аппаратно поддерживаемых типов данных:

8-разрядные числа со знаком и без знака;

16-разрядные числа со знаком и без знака;

64-разрядные числа со знаком и без знака;

64-разрядные числа в формате с плавающей точкой.

Адресность операционных команд: 3.

Способы адресации: непосредственная, относительная, прямая.

Основные характеристики регистровой памяти:

Количество регистров – 8;

Тип регистров – функционально ориентированный;

Разрядность регистров – 64 бита.

Тип локальной шины – совмещенная.

Наличие сопроцессора – есть.

Характеристики основной памяти:

Объем – 1024 Мбайт;

Разрядность шины данных – определяется разрядностью памяти – 32.

Способ организации ввода-вывода – изолированный.

Поддержка графики – нет.

Уточнение структуры системы

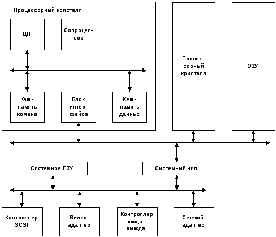

Разрабатываемый процессор предназначен для использования в качестве процессора (ЦП) рабочей станции. Обобщенная структура рабочей станции показана на рис.1

Рис.1

В состав станции входят:

Несколько процессорных кристаллов, составляющих предмет разработки;

ОЗУ;

Системный чип;

Контроллеры внешних устройств;

Видеоадаптер.

Имеются 2 шины – быстрая системная шина и шина ввода-вывода, разделенные системным чипом. В качестве шины ввода-вывода обычно используются стандартная шина, например PCI. Системный чип (чипы) содержит внешнюю логику (таймеры, часы реального времени, контроллеры ПДП и т.п.).

Разработка архитектуры внешних выводов

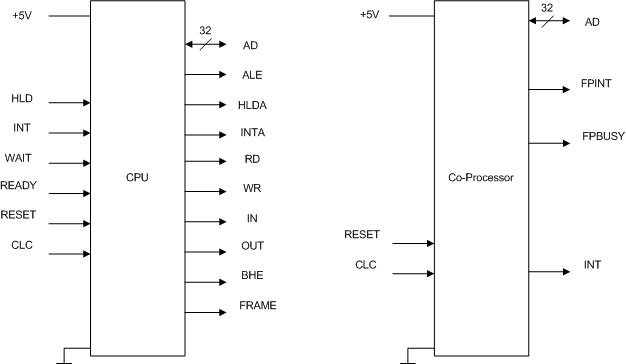

По нашему заданию необходимо использовать сопроцессор, поэтому необходимо разработать архитектуру внешних выводов ЦП и сопроцессора.

|

Рис.2 |

Рис.3 |

Процессор (рис.2) имеет совмещенную шину адреса и данных (AD). СигналALEиспользуется для фиксации адреса на внешнем регистре-защелке, а пара сигналовHLDиHLDA– для реализации механизма захвата шины. СигналыINTиINTAявляются сигналами запроса и подтверждения прерывания.

Линии RD(чтение),WR(запись),IN(ввод),OUT(вывод),BHE(разрешение записи старшего байта) задают выполняемую на шине операцию. ЛинияFRAMEиспользуется для организации режима пакетного обмена между ОЗУ и внутренними кэшами. Появление данного сигнала на шине означает начало транзакции, а снятие – указывает на то, что следующий цикл передачи данных на шине является последним.

Сигнал WAITиспользуется для организации взаимодействия с внешним математическим сопроцессором. На контактWAITпоступает сигнал от сопроцессора об окончании вычислений. КонтактREADY(готовность) служит для приема сигнала готовности от медленных внешних устройств. Назначение выводов питания,RESETиCLC(синхронизация) очевидны.

На рис.3 показан вариант архитектуры внешних выводов сопроцессора. На вывод FPBUSYподается единичный сигнал, указывающий на то, что сопроцессор занят. По линииFPINTвыдается сигнал прерывания в случае возникновения ошибочной ситуации (типа попытки деления на нуль). Назначение прочих выводов такое же, как и одноименных выводов ЦП.

ЦП и сопроцессор взаимодействуют следующим образом. ЦП декодирует поток команд. Если появляется команда обработки с плавающей точкой, то ЦП переписывает её на регистр команды сопроцессора (в качестве которого может выступать в частном случае порт ввода-вывода), а затем продолжает работу. При необходимости работы с памятью адреса вычисляются в ЦП. Для проверки доступности ЦП может использоваться, например специальная команда WAIT.

Для реализации был выбран процессор в стандартном корпусе на 132 контакта. Все «лишние» выводы решено использовать для дублирования контактов GND(«земля»), +5V(напряжение питания), а также возможно увеличение уровней прерывания.