Вторая часть Д. В. Пузанкову / арх часть 2

.docxФЕДЕРАЛЬНОЕ

АГЕНСТВО ПО ОБРАЗОВАНИЮ.

Государственное образовательное учреждение высшего профессионального образования.

«Санкт-Петербургский государственный электротехнический университет «ЛЭТИ» имени В.И. Ульянова (Ленина)»

(СПБГЭТУ)

Кафедра ВТ

ПОЯСНИТЕЛЬНАЯ ЗАПИСКА К КУРСОВОМУ ПРОЕКТУ

по дисциплине «Архитектура ЭВМ»

« Разработка программной модели однокристального RISC- процессора»

Выполнил студент группы 9306 Строев И. А.

Руководитель

Оценка:

Санкт-Петербург

2012 г.

1. Техническое задание

1.1. Предмет проектирования

Разработка программной модели однокристального RISC-процессора.

Проектируется процессор для встроенных применений (контроллер).

1.2. Общие требования к разрабатываемому процессору

Система команд должна удовлетворять следующим требованиям.

1. Операции обращения к памяти отделены от операций, связанных с обработкой данных.

2. Операции, связанные с преобразованием данных, выполняются по принципу регистр-регистр.

3. В общем случае аппаратно поддерживаются операции над целыми числами со знаком и без знака.

4. Система команд должна быть функционально полной и включать команды общего назначения и привилегированные команды.

5. Процессор должен иметь векторную систему прерываний.

6. Процессоры должны иметь встроенную кэш-память.

Программная модель представляет собой симулятор, который должен удовлетворять следующим требованиям:

1. Отображать содержимое регистров общего назначения, системных регистров и регистров, используемых для хранения чисел с плавающей точкой.

- 2. Симулятор должен позволять выполнять покомандное выполнение программы.

3. Выполняемая программа хранится в отдельном файле и представляет собой псевдоассемблерный код.

4. В зависимости от варианта задания симулятор пишется на Java.

1.3. Исходные данные для курсового проектирования

Гaрвардская архитектура

Вариант 15

|

Но-мер вари-анта |

Формат данных |

Адрес-ность |

Способ адресации |

Регистровая память |

||||||||||

|

|

8 |

16 |

32 |

|

Н |

О |

П |

К |

Коли- чество |

Тип |

Разряд-ность |

|||

|

15 |

+ |

+ |

- |

3 |

+ |

+ |

+ |

- |

64 |

ФО |

16 |

|||

|

Но-мер варианта |

Шина адрес-данные |

Память данных |

Память команд |

Ввод-вывод |

||||||

|

С |

Р |

Объем, Кбайт |

ШД

|

Объем, Кбайт |

ШК |

И |

П |

|||

|

15 |

+ |

- |

128 |

16 |

16 |

64 |

- |

+ |

||

Исходные данные для проектирования:

Поддерживаются следующие форматы данных:

- 8-разрядные числа со знаком и без знака;

- 16-разрядные числа со знаком и без знака;

64 функционально ориентированных регистра, 16-разрядные.

В процессоре используется совмещенная шина адреса и данных (С).

Объем оперативной памяти равен 128Кбайт. Разрядность шины данных (16-разрядная) определяется разрядностью памяти.

Ввод-вывод по аналогии с обращением к ячейкам памяти (П). Организация ввода-вывода по аналогии с обращением к ячейкам оперативной памяти (ОП) предполагает использование единого адресного пространства для ячеек памяти и портов ввода-вывода. В этом случае адресное пространство делится между ячейками ОП и регистрами внешних устройств. Данный подход позволяет по коду адреса определить, идет ли обращение к ячейке ОП или к регистру ВУ, не требует введения специальных команд ввода-вывода и дает возможность использовать различные способы адресации при обращении к регистрам ВУ (однако в этом случае возникают дополнительные проблемы при работе кэша и использовании виртуальной памяти).

Требуется разработать систему прерываний; при этом требуется реализовать векторную систему прерываний. (Таблица векторов может находиться по произвольным адресам). Предлагается использовать внешний контроллер прерываний.

Нет поддержки графики

Отличительной особенностью гарвардской архитектуры является наличие отдельной памяти команд. Принимается, что память команд размещается внутри кристалла, кроме того, возможно подключение дополнительной внешней памяти команд.

Раздельная реализация памяти команд и памяти данных упрощает организацию конвейера по выборке команд из памяти и по размещению их в очередь для дальнейшего исполнения. Такая организация позволяет избежать конфликтов при обращении к памяти, которые имеют место при использовании традиционной архитектуры, однако не снимает проблем, связанных с реализацией команд переходов.

2.2. Разработка архитектуры ЦП

2.2.1. Уточнение структуры системы

Разрабатываемый процессор предназначен для использования в качестве встроенного процессора.

Обобщенная структура процессора, соответствующая гарвардской архитектуре, приведена на рис. 1. Она представляет собой одноплатную ЭВМ, предназначенную для встроенных применений. На плате размещаются: ЦП, память данных, счетчик-таймер, адаптер интерфейса. Кроме того, на плате могут размещаться вспомогательные схемы и интерфейсные схемы для подключения внешних устройств (на рис. 1 эти схемы не показаны).

Разрабатываемая плата не имеет собственной дисковой памяти, дисплея и клавиатур. Предполагается, что разработка и отладка программного обеспепечения осуществляются на инструментальной машине с использованием кросс-систем программирования. В качестве инструментальной машины может использоваться, например рабочая станция, имеющая в своем составе дисплей, клавиатуру, дисковую память и т. п.

Рис.1

2.2.2. Архитектура внешних выводов

AD

64

+5V

ALE

Reset

HLD

CLC

HLDA

CPU

INT

INTA

RD

OUT

BHE

Frame

WR

Рис. 2

AD – совмещенная 64-разрядная шина адрес/данные;

ALE – сигнал для фиксации адреса на внешнем регистре-защелке;

HLD – сигнал запроса на захват шины;

HLDA – сигнал подтверждения запроса на захват шины;

INT – сигнал запроса на прерывание;

INTA – сигнал подтверждения запроса на прерывание;

RD – сигнал, означающий чтение данных с шины;

WR – сигнал, означающий запись данных (выставление данных на шину);

BHE – разрешение записи старшего байта, задают выполняемую на шине операцию;

IN – сигнал чтения из порта;

OUT – сигнал записи в порт;

FRAME – сигнал режима пакетного обмена данными между ОП и кэшем, появление данного сигнала на шине означает начало транзакции, а снятие – указывает на то, что следующий цикл передачи данных на шине является последним.

+5V – питание (но по идее 3,3В);

RESET – сброс;

CLC – тактовый сигнал.

2.2.3. Выбор форматов данных

основные используемые типы данных (см. рис. 3).

6

0

Байт

7

14

0

Слово

15

Рис. 3

Адреса представляются в виде целых чисел без знака.

Целые числа

Целые числа могут занимать байт, слово или двойное слово. Они могут быть знаковыми и беззнаковыми. В знаковых целых самый старший бит байта, слова или двойного слова, занимаемого числом, отводится для индикации знака числа. Нуль соответствует плюсу, 1 — минусу. Таким образом, возможный диапазон представляемых значений для знаковых целых составляет: от –128 до 127 для байта, от –231 до 231 для слов, от –263 до 263 для двойных слов. Беззнаковые целые могут принимать значения: от 0 до 255 для байт, от 0 до 232-1 для слов, от 0 до 264-1 для двойных слов.

2.2.5. Выбор форматов команд

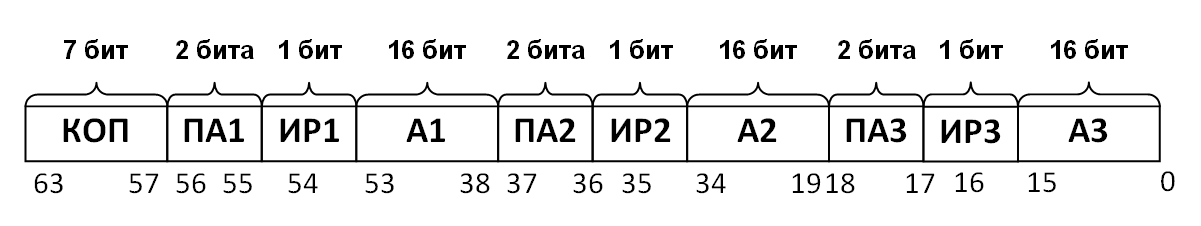

Все команды имеют единый формат. В соответствии с техническим заданием, команды должны быть трёхадресными.

В каждом цикле работы, процессор считывает из памяти команд 64-х разрядную команду, т.к. разрядность шины команд - 64 бита.

В битах 63 – 57 (КОП) хранится код операции. Всего 128 возможных команд.

Двухразрядное поле ПА1, ПА2, ПА3 указывает способ адресации для соответствующих полей А:

ПА1, ПА2, ПА3 = 0 – непосредственная адресация;

ПА1, ПА2, ПА3 = 1 – прямая адресация;

ПА1, ПА2, ПА3 = 2 – относительная адресация.

Адресные поля А1, А2 и А3 используются для хранения 1-го, 2-го операндов и результата. Поля ИР1, ИР2, ИР3 служат для указания номера индексного регистра, используемого при относительной адресации.

Непосредственная адресация

Значение, записываемое в регистр, задаётся непосредственно в команде. Например write DEAD,50. (16-тиричное число DEAD записывается в регистр с номером 50)

Прямая адресация

Прямой адрес – номер ячейки памяти, в которой хранится операнд.

Исполнительный адрес AИСП=A.

Относительная адресация

Исполнительный адрес формируется следующим образом:

AИСП=A+X, где

A – базовый адрес, указываемый в адресном поле команды;

X – относительный адрес (индекс), указывающий положение данного, относительно базового адреса A.