Обновление по АрхВС / avs_part11

.pdf

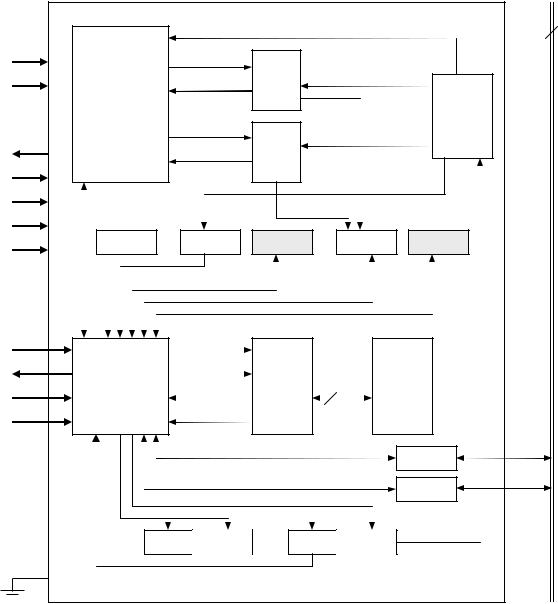

2.9 Структурно-функциональная схема процессора |

|||||

|

|

|

|

|

AD 32 |

|

|

|

|

|

данные |

WAIT |

|

|

|

|

|

|

|

операнды |

УУС |

|

|

READY |

РОН |

|

|

КОП |

|

|

результат |

|

|

||

|

|

|

DC |

||

|

|

|

|

|

|

|

|

операнды |

|

|

КОП |

INTA |

|

|

АЛУ |

|

|

|

|

|

|

||

|

|

результат |

|

|

|

INT |

|

|

|

|

|

+5 V |

|

|

|

|

|

RESET |

|

|

|

|

|

CLC |

CS |

PC |

PCI |

F |

FI |

|

|

|

|

|

|

|

адрес команды |

|

|

|

|

HLD |

|

к/д |

|

|

|

|

|

|

|

|

|

HLDA |

|

обновление |

|

|

|

|

ПП |

КЭШ |

|

ПК |

|

FRAME |

|

|

|||

|

данные |

|

ШК 16 |

|

|

|

|

|

|

||

ALE |

|

нет в кэше |

|

|

|

|

|

|

|

|

|

|

|

|

данные |

|

MD |

|

|

|

адрес |

|

MA |

|

|

|

|

|

|

|

NIA |

NI |

CIA |

CI |

текущая команда |

|

|

|

|

|

|

|

cравнение адреса с PC |

|

|

||

|

|

Рисунок 2.9.1 |

|

|

|

Условные обозначения: |

|

АЛУ – арифметико-логическое устройство; |

РОН – регистры общего назначения; |

КЭШ – общий кэш памяти данных и |

УУС – устройство управлением |

команд; |

сопроцессора; |

К/Д – сигнал кэша: команды или данные; |

ШК 16 – 16-битная шина команд; |

О – непосредственный операнд; |

AD 32 – 32-битная совмещённая шина |

ПД – память данных; |

адрес-данные; |

ПК – память команд; |

DC – дешифратор команд; |

ПП – процессор памяти; |

|

12

Регистры:

CS – адрес начала загруженной программы;

CI – текущая команда;

CIA – адрес текущей команды; F – регистр флажков;

FI – регистр для сохранения значения F при прерывании;

MD – буфер данных;

MR – буфер адреса;

NI – следующая команда;

NIA – адрес следующей команды; P – программный счётчик

PI – регистр для сохранения значения P при прерывании;

На данной схеме присутствуют все регистры из раздела «структура регистровой памяти», а также АЛУ, дешифратор команд, кэш-память, устройство управления исполнительным процессором и процессором памяти. Краткие пояснения связей даны на схеме; необходимо пояснить отдельные моменты.

Устройство управления исполнительным процессором координирует работу всех устройств исполнительной части процессора, выставляя необходимые управляющие сигналы на входы устройств.

Устройство управления процессором памяти управляет процессами записи в память и чтения из нее, содержит схемы для работы с кэш-памятью, выставляет разрешающие и запрещающие сигналы для записи адреса, данных и команд в соответствующие регистры.

Процессор не содержит коммутирующие устройства, часто использующихся в подобных решениях, так как команды работы с АЛУ не содержат непосредственной адресации.

Сравнение адресов на данной схеме реализовано внутри процессора управления памятью.

Память данных по условию реализована вне корпуса процессора.

В процессоре реализован двухступенчатый конвейер из двух операций: выборка команды и выполнение. Команды хранятся в очереди из двух мест. Параллельно с выполнением текущей команды происходит чтение команды из кэш-памяти и сохранение ее в последнем месте очереди. По выполнении команды очередь сдвигается и процесс повторяется.

13