C52 / C52

.pdf10

В задании определяется объем оперативной памяти, к которому необходимо обеспечить доступ, в режиме прямоадресуемой памяти. Разрядность шины данных определяется разрядностью памяти.

Ввод-вывод может быть организован либо изолированным (И), т. е. с использованием специальных команд ввода-вывода, либо по аналогии с обращением к ячейкам памяти (П). Изолированный ввод-вывод подразумевает использование специальных команд ввода-вывода. Идентификация обращения к регистрам внешних устройств осуществляется по коду операции. Организация ввода-вывода по аналогии с обращением к ячейкам оперативной памяти (ОП) предполагает использование единого адресного пространства для ячеек памяти и портов ввода-вывода. В этом случае адресное пространство делится между ячейками ОП и регистрами внешних устройств. Данный подход позволяет по коду адреса определить, идет ли обращение к ячейке ОП или к регистру ВУ, не требует введения специальных команд ввода-вывода и дает возможность использовать различные способы адресации при обращении к регистрам ВУ (однако в этом случае возникают дополнительные проблемы при работе кэша и использовании виртуальной памяти).

Для всех вариантов требуется разработать систему прерываний; при этом требуется реализовать векторную систему прерываний. (Таблица векторов может находиться по произвольным адресам). Предлагается использовать внешний контроллер прерываний.

Отличительной особенностью гарвардской архитектуры является наличие отдельной памяти команд (см. табл. 4). Принимается, что память команд размещается внутри кристалла, кроме того, возможно подключение дополнительной внешней памяти команд.

Раздельная реализация памяти команд и памяти данных упрощает организацию конвейера по выборке команд из памяти и по размещению их в очередь для дальнейшего исполнения. Такая организация позволяет избежать конфликтов при обращении к памяти, которые имеют место при использовании традиционной архитектуры, однако не снимает проблем, связаннных с реализацией команд переходов.

Наличие поддержки виртуальной памяти для процессоров с традиционной архитектурой подразумевает решение следующих задач:

-разработки формата и способа хранения таблицы виртуальных и физических страниц;

-выбора способа преобразования виртуального адреса в физический

иего аппаратную поддержку;

11

-выбора варианта удаления страницы из ОЗУ и его алгоритмическую проработку;

-разработки алгоритма обмена страницами между ОЗУ и внешней памятью.

Наличие кэш-памяти данных для процессоров с гарвардской архитектурой подразумевает решение следующих задач:

-разработки основных алгоритмов работы кэш-памяти;

-проработки вопросов структурной организации кэш-памяти;

-разработки стратегии и алгоритма замены строк.

1.4. Средства реализации модели

В качестве языка реализации используются языки С++ и Java. Способы реализации модели приведены в табл. 5

Таблица 5

Средства реализации модели

NN вариантов |

Язык реализации |

|

|

1-10 |

Java (приложение) |

|

|

11-20 |

Java (апплет) |

|

|

21-30 |

С++ (Linux) |

|

|

1.5. Результаты проект ирования

Впроцессе выполнения курсового проекта разрабатываются: - архитектура ЦП; - приложение (программный эмулятор).

Впроцессе разработки архитектуры определяются:

1.Форматы команд и данных.

2.Регистровая модель процессора (включая пользовательские и системные регистры).

3.Структура выводов кристалла.

4.Система команд (включая семантику их выполнения и установку флажков).

5.Обобщенный алгоритм функционирования процессора (включая алгоритмы выполнения основных команд).

6.Алгоритмы выполнения основных операций на шине (чтение, запись, ввод, вывод, захват шины, прерывание). Необходимо предусмотреть пакетный режим обмена между ОП и кэш-памятью.

12 7. Внутренняя организация (до структурного уровня) (включая меха-

низмы виртуальной памяти, механизмы защиты памяти и механизмы работы с кэш-памятью).

В процессе разработки модели создаются:

UML диаграммы, описывающие функционирование модели;

-собственно приложение;

-комплект документации на программную систему.

Должны быть разработаны, как минимум, следуюшие UML диаграммы:

-диаграммы вариантов использования (use case diagrams);

-диаграмма классов (class diagram).

Всостав документации на созданное приложение входят:

-руководство оператора;

-руководство системного программиста;

-программа и методика испытания.

Документация оформляется в соответствии с действующими ГОСТ.

2. Последовательность выполнения курсового проекта

2.1. Общая последовательность

Выполнение проекта осуществляется в следующем порядке:

1.Разработка архитектуры ЦП.

2.Разработка программной модели.

3.Разработка документации на программный проект.

4.Оформление отчета.

2.2.Разработка архитектуры ЦП

2.2.1. Уточнение структуры системы

Разрабатываемый процессор предназначен для использования в качестве центрального процессора (ЦП) рабочей станции (варианты с традиционной архитектурой) либо в качестве встроенного процессора.

Обобщенная структура рабочей станции показана на рис. 1.

В состав станции входят: несколько процессорных кристаллов, составляющих предмет разработки; ОЗУ; системный чип; контроллеры внешних устройств; видеоадаптер. Имеются две шины – быстрая системная шина и шина ввода-вывода, разделенные системным чипом. В качестве шины ввода-вывода обычно используется стандартная шина, например PCI. Системный чип (чипы) содержит внешнюю логику (таймеры, часы реального времени, контроллеры ПДП и т. п.).

13

Рис. 1

14

Рис. 2

Обобщенная структура процессора, соответствующая гарвардской архитектуре, приведена на рис. 2. Она представляет собой одноплатную ЭВМ, предназначенную для встроенных применений. На плате размещаются: ЦП, память данных, счетчик-таймер, адаптер интерфейса. Кроме того, на плате могут размещаться вспомогательные схемы и интерфейсные схемы для подключения внешних устройств (на рис. 2 эти схемы не показаны).

Разрабатываемая плата не имеет собственной дисковой памяти, дисплея и клавиатур. Предполагается, что разработка и отладка программного обеспепечения осуществляются на инструментальной машине с использованием кросс-систем программирования. В качестве инструментальной машины может использоваться, например рабочая станция, имеющая в своем составе дисплей, клавиатуру, дисковую память и т. п.

Основной задачей данного этапа проектирования является уточнение структуры и разрядности внутренней шины.

2.2.2. Разработка архитектуры внешних выводов

Для вариантов, не требующих использования сопроцессора, разрабатывается архитектура внешних выводов только ЦП. Для вариантов, тре-

15

бующих наличие сопроцессора, разрабатывается архитектура внешних выводов ЦП и сопроцессора.

Рис. 3 Рис. 4 При разработке архитектуры внешних выводов следует ориентиро-

ваться на использование стандартных корпусов, имеющих, соответственно, 40, 68, 132, 144, 168, 172 выводов. В случае, если остаются “лишние” выводы, они могут быть использованы для следующих целей:

-дублирования контактов “Земля” и “Питание”;

-увеличения разрядности шины адреса;

-введения нескольких уровней прерывания.

Обобщенная архитектура внешних выводов кристалла ЦП показана на рис. 3, а сопроцессора – на рис. 4.

Процессор (рис. 3) имеет совмещенную шину адреса и данных (AD). Сигнал ALE используется для фиксации адреса на внешнем регистрезащелке, а пара сигналов HLD и HLDA – для реализации механизма захвата шины. Сигналы INT и INTA являются сигналами запроса и подтверждения прерывания. Если на корпусе имеется достаточное число свободных выводов, то целесообразно ввести несколько уровней запроса на прерывание.

Линии RD (Чтение), WR (Запись), IN (Ввод), OUT (Вывод), BHE (Разрешение записи старшего байта) задают выполняемую на шине операцию. Линия FRAME используется для организации режима пакетного обмена между ОЗУ и внутренними кэшами. Появление данного сигнала на шине озна-

16

чает начало транзакции, а снятие – указывает на то, что следующий цикл передачи данных на шине является последним.

Сигнал WAIT используется для организации взаимодействия с внешним математическим сопроцессором. На контакт WAIT поступает сигнал от сопроцессора об окончании вычислений. Контакт READY (Готовность) служит для приема сигнала готовности от медленных внешних устройств. Назначение выводов питания, RESET и CLC (Синхронизация) очевидны.

На рис. 4 показан вариант архитектуры внешних выводов сопроцессора. На вывод FPBUSY подается единичный сигнал, указывающий на то, что сопроцессор занят. По линии FPINT выдается сигнал прерывания в случае возникновения ошибочной ситуации (типа попытки деления на нуль). Назначение прочих выводов такое же, как и одноименных выводов ЦП.

ЦП и сопроцессор взаимодействуют следующим образом. ЦП декодирует поток команд; если появляется команда обработки с ПТ, то ЦП переписывает ее на регистр команды сопроцессора (в качестве которого может в частном случае выступать порт ввода-вывода), а затем продолжает работу. При необходимости работы с памятью адреса вычисляются в ЦП. Для проверки доступности ЦП может использоваться, например специальная команда WAIT.

2.2.3. Выбор форматов данных

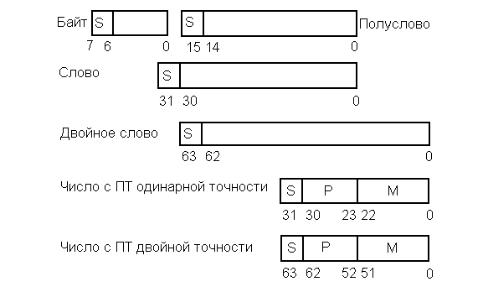

На рис. 5 показаны основные используемые типы данных.

Рис. 5 Целые числа представляют собой числа со знаком или без знака. Це-

лые числа со знаком представляются в дополнительных кодах. Целые числа без знака используются также и для представления адресов. Для представления чисел с ПТ рекомендуется учитывать требования стандарта

17

(ANSI/IEEE Standart 754). При этом следует дать подробное описание представления особых ситуаций (нуль, переполнение, NAN).

2.2.4.Определение модели памяти и структуры регистровой памяти

Для гарвардской архитектуры разработка модели памяти не вызывает проблем.

Для традиционной архитектуры модель памяти должна удовлетворять требованиям, предъявляемым многопользовательской многозадачной ОС типа UNIX (LINUX).

При разработке модели памяти (рис. 6) необходимо обеспечить размещение невыгружаемого ядра ОС в фиксированных ячейках памяти. Кроме того, при использовании совмещенного ввода-вывода необходимо запрещать кэширование соответствующих страниц памяти. Одно из возможных решений – обеспечение доступа к одним и тем же физическим адресам по разным виртуальным адресам.

Рис. 6

В режиме пользователя программе доступны 2 Гбайт виртуальной памяти. В режиме ядра программа получает доступ ко всей памяти объемом 4 Гбайт, причем первые 2 Гбайт – пользовательская память, оставшиеся 2 Гбайт – системная. Системная память делится на три сегмента объемами 0.5, 0.5 и 1 Гбайт. При обращении к адресам, принадлежащим сегменту 1, используется кэш, но не используется переадресация через буфер TLB, т. е. обращение идет к первым 512 Мбайт физической памяти. При работе с сегментом 2 не используются ни кэш, ни TLB – обращение идет к первым 512

18

Мбайт физической памяти. При работе с сегментом 3 используются и кэширование, и переадресация. Подобная модель памяти позволяет работать с ячейками как с портами (сегмент 2) либо обращаться к памяти по абсолютным адресам при работе со структурами данных ядра. Сегмент 3 можно использовать для работы с загружаемыми модулями.

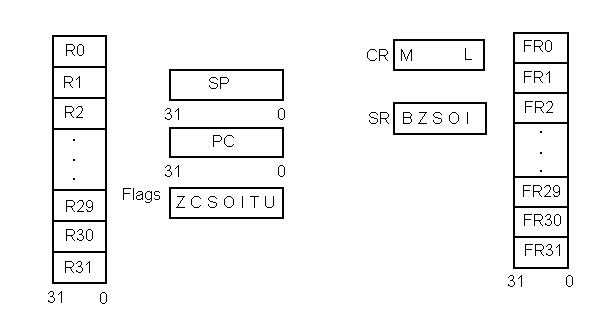

Процессор в общем случае содержит две группы регистров – пользовательские и системные. (Системные регистры доступны только при работе в режиме ядра.)

На этапе определения структуры регистровой памяти выбираются:

-число регистров различных типов и их разрядность;

-состав и структура регистра флажков.

Пользовательские регистры, в свою очередь, подразделяются на адресные, целочисленные и регистры с ПТ. Часто одни и те же регистры используются как в качестве адресных, так и в качестве целочисленных (РОН). Кроме того, обычно имеется некоторое количество управляющих регистров.

В состав системных регистров могут входить и такие регистры:

-регистр физического адреса таблицы векторов прерывания;

-регистр физического адреса таблицы переадресации;

-регистр для записи адреса страничной ошибки, куда записывается адрес страницы, отсутствующей в памяти.

Один из возможных вариантов организации пользовательской регистровой памяти ЦП для вариантов с использованием внешнего сопроцессора показан на рис. 7.

Рис. 7 |

Рис. 8 |

19

В структуре, приведенной на рис. 7, регистровая память включает тридцать два 32-разрядных РОН и 32-разрядный счетчик команд. Регистр флажков содержит семь флажков, которые используются следующим образом:

Z |

– |

признак нулевого результата; |

С – |

признак переноса из старшего разряда; |

|

S |

– |

знак результата; |

O – признак переполнения результата; |

||

I |

– |

разрешение прерывания; |

T– пошаговый режим;

U– режим супервизор-пользователь.

Возможный вариант организации регистровой памяти сопроцессора показан на рис. 8.

Необходимо отметить, что в RISC-процессорах аппаратный стек не используется, а адрес возврата запоминается в одном из РОН.

2.2.5. Выбор форматов команд

При выборе форматов следует исходить из принципов RISC-об- работки, в соответствии с которыми используется минимальное число форматов команд. Наиболее желательным является использоване одного (32-разрядного) формата. Приемлемым можно также считать и вариант, когда команды имеют разную длину.

Рис. 9

На рис. 9 и 10 приведены возможные форматы команд. На рис. 9 показаны форматы команд, соответствующие второму случаю. Операционные команды (рис. 9, а) имеют длину 16 разрядов и содержат четыре поля: 7- разрядное поле кода операции (OP) и три 3-разрядных поля для задания регистров источников и приемника. Типичная двухместная операция типа сложения выполняется по схеме R1 ← <R2> * <R3>. Команды обращения к