Требования к курсовику / Консультация 1

.doc1

1.5. Результаты проектирования

В процессе выполнения курсового проекта разрабатываются:

- архитектура ЦП;

- приложение (программный эмулятор).

В процессе разработки архитектуры определяются:

1. Форматы команд и данных.

2. Регистровая модель процессора (включая пользовательские и системные регистры).

3. Структура выводов кристалла.

4. Система команд (включая семантику их выполнения и установку флажков).

5. Обобщенный алгоритм функционирования процессора (включая алгоритмы выполнения основных команд).

6. Алгоритмы выполнения основных операций на шине (чтение, запись, ввод, вывод, захват шины, прерывание). Необходимо предусмотреть пакетный режим обмена между ОП и кэш-памятью.

7. Внутренняя организация (до структурного уровня) (включая механизмы виртуальной памяти, механизмы защиты памяти и механизмы работы с кэш-памятью).

2 2.2.4

Процессор в общем случае содержит две группы регистров – пользовательские и системные. (Системные регистры доступны только при работе в режиме ядра.)

На этапе определения структуры регистровой памяти выбираются:

- число регистров различных типов и их разрядность;

- состав и структура регистра флажков.

Пользовательские регистры, в свою очередь, подразделяются на адресные, целочисленные и регистры с ПТ. Часто одни и те же регистры используются как в качестве адресных, так и в качестве целочисленных (РОН). Кроме того, обычно имеется некоторое количество управляющих регистров.

В состав системных регистров могут входить и такие регистры:

- регистр физического адреса таблицы векторов прерывания;

- регистр физического адреса таблицы переадресации;

- регистр для записи адреса страничной ошибки, куда записывается адрес страницы, отсутствующей в памяти.

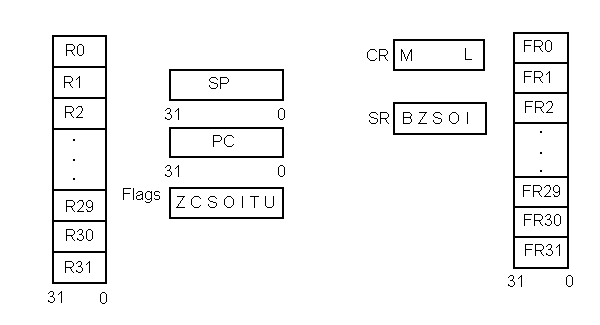

Один из возможных вариантов организации пользовательской регистровой памяти ЦП для вариантов с использованием внешнего сопроцессора показан на рис. 7.

Рис. 7 Рис. 8

В структуре, приведенной на рис. 7, регистровая память включает тридцать два 32-разрядных РОН и 32-разрядный счетчик команд. Регистр флажков содержит семь флажков, которые используются следующим образом:

Z – признак нулевого результата;

С – признак переноса из старшего разряда;

S – знак результата;

O – признак переполнения результата;

I – разрешение прерывания;

T – пошаговый режим;

U – режим супервизор-пользователь.

Возможный вариант организации регистровой памяти сопроцессора показан на рис. 8.

Необходимо отметить, что в RISC-процессорах аппаратный стек не используется, а адрес возврата запоминается в одном из РОН.

3 2.2.6

Система команд должна быть функционально полной и включать как минимум следующие команды:

1) обращения к памяти по чтению и записи;

2) целочисленные арифметические для чисел со знаком и без знака (сложение, вычитание, умножение, деление, сравнение);

3) арифметические с ПТ (сложение, вычитание, умножение, деление, сравнение);

4) логические (поразрядное “И”, “ИЛИ” и “Исключающее ИЛИ”);

5) сдвигов на произвольное число тактов;

6) условных и безусловных переходов;

7) работы с подпрограммами;

8) загрузки в регистры непосредственных операндов;

9) ввода-вывода;

10) управления вычислительным процессом.

4

2.2.7. Внутренняя организация

При разработке структуры процессора следует исходить из следующих положений.

В процессоре реализуется конвейерный принцип обработки информации. Используется либо духуступенчатый, либо трехступенчатый конвейеры.

Два возможных варианта структурной организации процессора показаны на рис. 11 и 12.

Р ис.

11

ис.

11

Для двухступенчатого конвейера (рис. 2.11) выделяются фаза выборки команды и фаза выполнения команды. Параллельно и асинхронно могут работать два процессора: процессор памяти и исполнительный процессор. Процессор памяти обеспечивает работу с памятью команд и памятью данных, а также с кэш-памятью. На исполнительный процессор возлагаются функции, связанные с дешифрацией и выполнением команд.

5 2.2.7

Регистровая память реализуется на регистровых файлах, допускающих в одном такте выборку двух операндов и запись одного операнда. Данные при этом выбираются из регистровых файлов по переднему фронту импульса синхронизации и записываются по заднему фронту. Операционные устройства, как целочисленные, так и с ПТ, представляют собой комбинационную схему. Все целочисленные операции выполняются за один такт, а с ПТ – за фиксированное число тактов. Например, сложение с ПТ и умножение с ПТ выполняются за два такта, а деление с ПТ – за пять тактов. Арифметические операции с ПТ выполняются либо в сопроцессоре, либо в отдельном арифметико-логическом устройстве (АЛУ).

Р ис.

13

ис.

13

Обобщенная структура исполнительной подсистемы показана на рис. 13. Основными элементами исполнительной подсистемы являются регистровый файл и АЛУ. По переднему фронту синхроимпульса из регистрового файла одновременно выбираются два операнда, соответствующие адресам R2 и R3. В течение времени длительности тактового импульса сигналы распространяются через комбинационные схемы АЛУ. При этом выполняемая операция определяется подаваемым на вход АЛУ кодом операции (OPC). Если на управляющий вход регистрового файла подается сигнал разрешения записи WR, то по заднему фронту в регистровом файле по адресу R1 запоминается результат выполнения операции.

6 2.2.7

В случае если заданием предусмотрено поддержание механизма работы с виртуальной памятью, то в состав адресного процессора необходимо ввести регистры переадресации (TLB), в которых хранятся отдельные строки таблицы переадресации. Число TLB может находиться в пределах от 16 до 256. В системе команд необходимо предусмотреть команды работы с данными регистрами и позаботиться о том, чтобы эти команды были отнесены к привилегированным. Кроме собственно регистров TLB необходимо предусмотреть наличие необходимых управляющих регистров. Как минимум необходимо иметь регистр, в котором хранится абсолютный адрес таблицы страниц. Кроме того, может быть полезен регистр, в котором хранится, например случайный адрес буфера TLB. Необходимо предусмотреть команду очистки буфера TLB. Очищать буфер необходимо при переключении задачи, поскольку каждая задача имеет собственную таблицу страниц.

7

2.2.10. Разработка алгоритмов выполнения основных операций на шине

Требуется разработать алгоритмы выполнения основных операций на шине:

- чтение данных;

- запись данных;

- прерывание;

- ввод, вывод;

- захват шины.

При работе с кэш-памятью обмен данными между ней и основной памятью осуществляется в режиме передачи блоков данных.

В пояснительной записке следует привести временные диаграммы работы шины.

8

Что нужно сделать:

-

Представить более подробные (по тактам) алгоритмы выполнения основных команд по разработанной или иной (если понадобится – более детальной) схеме (в соответствии с п.5 и разделом 2.2.9 метод указаний). Например, одной арифметической, одной – условной передачи управления, одной – обращения к памяти. Так, чтобы иллюстрировались разные способы адресации.

На защите быть готовым описывать потактовую реализацию этих алгоритмов по схеме, указывая шины, по которым передается информация (данные, адреса, другие поля команды, признаки).

-

Представить алгоритмы выполнения и временные диаграммы операций на шине (в соответствии с п.6 и разделом 2.2.10 метод указаний).

-

Раздел 2.2.7 предписывает использование конвейерного принципа обработки информации. Должен быть раздел с описанием, как это реализуется в разработанном процессоре.

-

Описание функционирования должно быть сделано на уровне, соответствующем представленной структурной схеме процессора.

Рекомендации по уровню представления структурной схемы:

- конкретизировать связи АЛУ и блока регистров. Сравните разработанную Вами схему и схему на рис.13 в метод указаниях (R1, R2, R3 – 3 входные шины адреса регистров операндов и результата, связанные с соответствующими формату команды группами разрядов РК);

- показать разрядность шин и/или указать, какая информация по ним передается. Например, на разработанной схеме КЭШ связан шинами с другими устройствами. Какая информация по ним передается и куда/откуда?

- показать системные регистры, их основные связи;

- предусмотреть на структурной схеме возможность формирования адреса для различны способов адресации.