ІКТА / КБ-24 / Архітектура Мельник, Нємкова / Лаби готові / Архітектура №3

.docxМІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАЇНИ

НАЦІОНАЛЬНИЙ УНІВЕРСИТЕТ “ЛЬВІВСЬКА ПОЛІТЕХНІКА”

ІКТА

Кафедра ___

ЗВІТ

ДО ЛАБОРАТОРНОЇ РОБОТИ № 1

З КУРСУ:

“ Архітектура комп’ютерних систем”

НА ТЕМУ:

“ Програма просте число ”

Підготував:

Ст.гр.КБ-24

Войтович О.О.

Прийня__:

___________________

Львів 2019

Базова частна

Метою виконання базової частини кожної лабораторної роботи є опанування студентом технологій обробки потоку інструкцій конвеєром універсальних процесорів (на прикладі обробки програм певних типів) та отримання навичок з кількісного оцінювання ефективності мікроархітектур цих процесорів.

Звіт з роботи

Завдання

1. Завантажити базисну версію програми до симулятора. Спланувати використання комірок головної пам’яті та записати до них вихідні дані.

2. Виконати програму у кроковому режимі. Перевірити виконнання програми.

3. Пояснити подані вікнами(циклове вікно, вікно статистик) симулятора протоколи вионання програми. 4. Зробити висновки за результатами симуляції виконання програми.

Базисна версія програми

; WINDLX Exp.2: Generate prime number table

; (c) 1991 Guenther Raidl

; Modified 1992 Maziar Khosravipour

; Program begins at symbol main

; generates a table with the first 'Count' prime numbers from 'Table'

;---

.data

;--- size of table

.global Count

Count: .word 10

.global Table

Table: .space Count*4

.text

.global main

main:

;--- Initialization

addi r1,r0,0 ;Index in Table

addi r2,r0,2 ;Current value

;--- Determine, if R2 can be divided by a value in table

NextValue: addi r3,r0,0 ;Helpindex in Table

Loop: seq r4,r1,r3 ;End of Table?

bnez r4,IsPrim ;R2 is a prime number

lw r5,Table(R3)

divu r6,r2,r5

multu r7,r6,r5

subu r8,r2,r7

beqz r8,IsNoPrim

addi r3,r3,4

j Loop

IsPrim: ;--- Write value into Table and increment index

sw Table(r1),r2

addi r1,r1,4

;--- 'Count' reached?

lw r9,Count

srli r10,r1,2

sge r11,r10,r9

bnez r11,Finish

IsNoPrim: ;--- Check next value

addi r2,r2,1 ;increment R2

j NextValue

Finish: ;--- end

trap 0

Clock Cycle Diagram

![]()

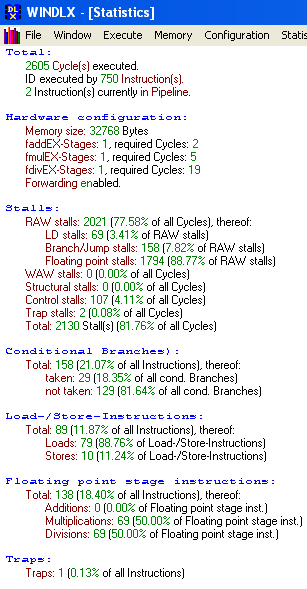

Виходячи з даного скріншоту видно, що для викнання інструкцій 5, 10 та 17 було витрачено зайву кількість циклів замість запланованих, за рахунок того що в процесі виконання цих інструкцій виникає RAW-залежність між даними, також можна побачити, що виконання інструкцій множення і ділення викликає величезну затримку в конвеєрі команд і є основною причиною затримок типу R-stall

На рисунку чітко видно причину затримки у виконанні 5, 10 та 17 інструкцій – це червона стрілка від 4, 9 та 16 інструкцій. Червоні стріли позначають необхідність пригальмування конвеєра (stall).

На виконання програми було використано 2605 циклів з яких 2021 викликані затримкою R-stall.

Експереминтальна частина

Метою виконання експериментальної частини відповідної лабораторної роботи є прищеплення студентам навичок з самостійного планування експерименту та розв'язування інженерних задач, що при цьому виникають, з подальшим оцінюванням ефективності запропонованих та втілених ними пропозицій за обраними студентами критеріями.

Завдання

1. Запропонувати заходи з прощення ефективності використання апаратних засобів процесора та скласти відповідну експереминтальну версію базової пограми.

2. Виконати експериментальну у кроковому режимі. Перевірити результат виконання програми.

3.Пояснити подані вікнами(циклове вікно, вікно статистик) симулятора протоколи виконання програми.

4. Подати кількісні значення тих характеристик, які доводять зростання ефективностіроботи апаратних засобів.

5. Зробити висновки за результатами виконання експеременту.

Модифікована програма на асемблерній мові

; WINDLX Exp.2: Generate prime number table

; (c) 1991 Guenther Raidl

; Modified 1992 Maziar Khosravipour

; Program begins at symbol main

; generates a table with the first 'Count' prime numbers from 'Table'

;---

.data

;--- size of table

.global Count

Count: .word 10

.global Table

Table: .space Count*4

.text

.global main

main:

;--- Initialization

addi r1,r0,0 ;Index in Table

addi r2,r0,2 ;Current value

lw r9,Count

;--- Determine, if R2 can be divided by a value in table

NextValue: addi r3,r0,0 ;Helpindex in Table

Loop: seq r4,r1,r3 ;End of Table?

lw r5,Table(R3)

bnez r4,IsPrim ;R2 is a prime number

divu r6,r2,r5

multu r7,r6,r5

subu r8,r2,r7

addi r3,r3,4

beqz r8,IsNoPrim

j Loop

IsPrim: ;--- Write value into Table and increment index

sw Table(r1),r2

addi r1,r1,4

;--- 'Count' reached?

srli r10,r1,2

sge r11,r10,r9

bnez r11,Finish

IsNoPrim: ;--- Check next value

addi r2,r2,1 ;increment R2

j NextValue

Finish: ;--- end

trap 0

Clock Cycle Diagram

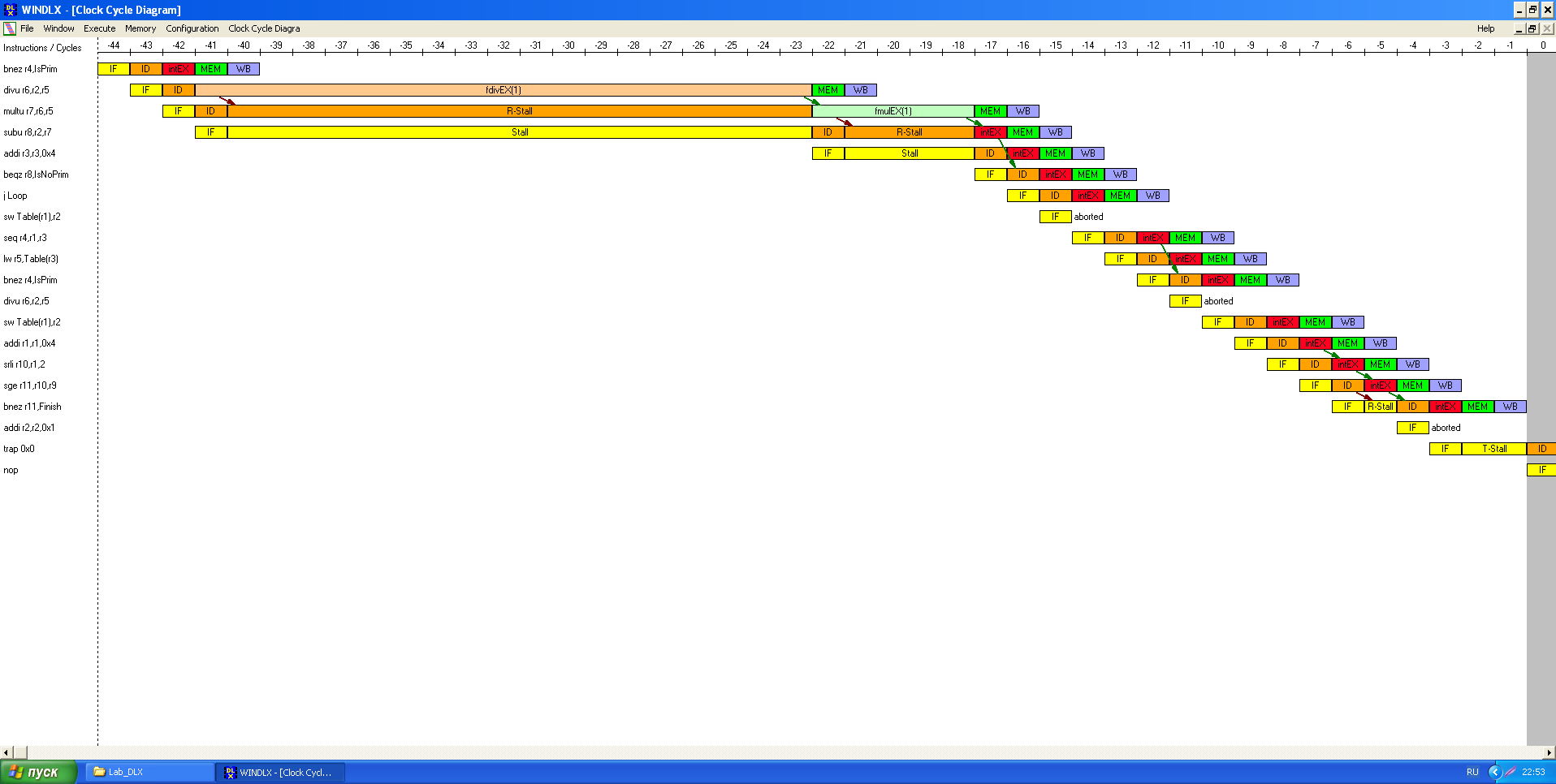

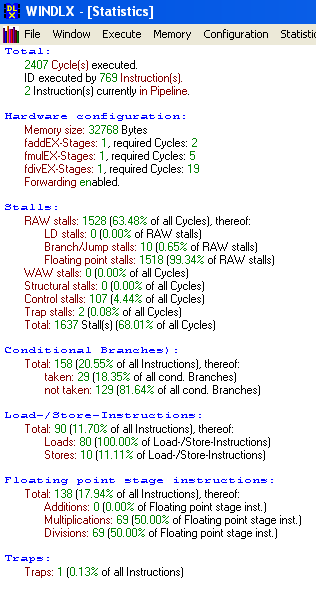

З скріншоту видно, що за допомогою перестановки інструкцій процесора без зміни логіки програми, ми змогли зменшити кількість затримок R-stall

Порівнюючи

з вікном статистики базисної програми

можна сказати, що ми позбулися деяких

затримок типу RAW-stalls

та скоротили кількість циклів виконання

програми з 2605 до 2407

Висновок

На цій лабораторній роботі я продовжив працювати з програмою WinDLX та всіма її компонентами, розібрав принцип роботи базисної програми «Просте число» та визначив, що її код не досконалий і викликає 2021 затримку в конвеєрі типу R-stall. Програму на асемблерній мові вдалося оптимізувати за допомогою перестановки її рядків, що не змінило логіку виконання програми, але спричинило ліквідування деяких затримок і скоротило кількість циклів виконання програми з 2605 до 2407.