Учебные материалы АОИС часть 1 / part_1 / Теория / АОИС1

.pdf

|

|

|

|

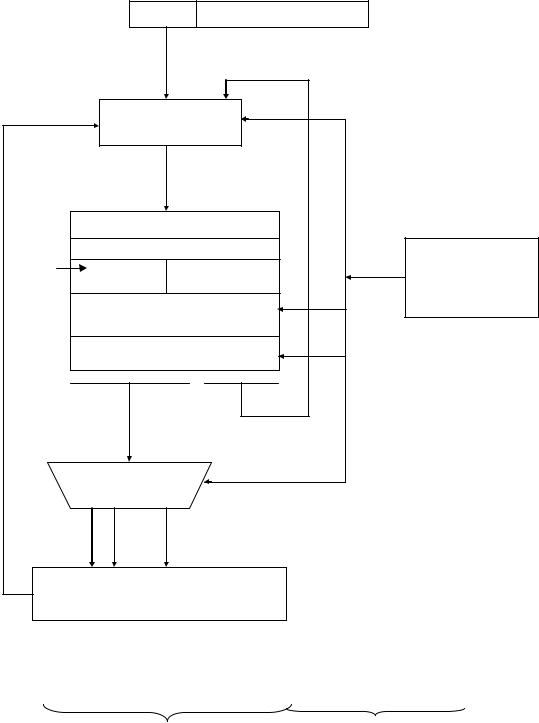

Ши Вх |

Пр Рг1 |

|

|

|

|

|

|

|

||

2-е слагаемое |

|

|

|

|

|

Рг 1 |

|

||

или |

|

|

||

вычитаемое |

0 |

|

n-1 |

Пр Рг В |

|

|

|

|

|

Пр Рг АП(прямая)

Пр РгАИ(инверсная)

(сложение) (вычитание)

Входные |

|

Рг А |

|

|

Рг В |

1-е слагаемое |

регистры |

|

|

|

|

|

или |

АЛУ |

0 |

n-1 |

|

0 |

n-1 |

уменьшаемое |

|

|

|

|

|

|

|

|

|

0 |

|

|

n-1 |

0 |

|

n-1 |

|

|

|

|

|

|

|

|

|

|

+1 См |

Сумматор |

|

|

|

|

См |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

n-1 |

|

|

|

||

|

Пн См [ 0 ] |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

Пр Рг См |

|

См [ 0 ] |

Пн См [ 1 ] |

|

|

|

|

||||

Формирование |

|

|

|

См [1 : n-1] |

|

|

|

||

|

|

|

|

|

|

||||

кода признака |

ПР |

|

|

|

|

|

|||

результата (ПР) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рг См |

|

|

|

Пр УБ |

|

|

|

0 |

|

n-1 |

|

||

|

|

|

|

|

|

|

|

|

|

Пр1 |

Пр0 |

|

|

|

Пр Ши Вых |

||||

В управляющий |

|

|

|

|

|

||||

|

|

блок |

|

Ши Вых |

|

|

|

||

|

|

|

|

|

|

Рис. 4.10 |

|||

108

ПР = 11, если

ПнСМ 0 ПнСМ 1

ПнСМ 1 ПнСМ 0

ПнСМ 0 ПнСМ 1 ;

ПнСМ 1 ;

ПР = 00, если

n

CM i 1;

i 0

ПР = 01, формируется, если

СМ 0 ПнСМ 0

ПнСМ 0 ПнСМ 1

ПнСМ 1 ПнСМ 0

ПнСМ 0 ПнСМ 1

ПнСМ 1 ;

;

ПР = 10, формируется, если

СМ 0 ПнСМ 0

ПнСМ 0 ПнСМ 1

ПнСМ 1 ПнСМ 0

ПнСМ 0 ПнСМ 1

ПнСМ 1 .

.

Кратко приведенная выше микропрограмма может быть записана следующим образом (табл. 4.2):

Таблица 4.2 Микропрограмма сложения/вычитания чисел

Такты |

Сигналы |

1 |

Пр Рг В |

2 |

Пр Рг 1 |

3 |

Пр Рг АП или Пр Рг АИ |

4 |

Пр Рг См или Пр Рг См + 1 См |

5 |

Пр Ш и Вых |

Напомним, что каждый управляющий функциональный сигнал поступает в начале некоторого такта на соответствующую ему шину ОБ, вызывая выполнение в ОБ определенной микрооперации (передача слов, суммирование кодов и т.д.).

Управляющие сигналы генерируются УБ. Последовательность этих сигналов задается поступающими на входы УБ:

1)кодом операции;

2)сигналами из ОБ, несущими информацию об особенностях операндов, промежуточных и конечных результатах;

3)синхросигналами, задающими границы тактов.

Формально УБ может рассматриваться как конечный автомат, определяемый:

а) множеством Z = {Z1, ... , Zm} – выходных сигналов, соответствующих множеству микроопераций в обрабатывающем блоке; при vi = 1 возбуждается i-я операция;

б) множеством v = {v1, ..., vn} – входных сигналов, соответствующих задаваемому извне двоичному коду операции, и двоичным значением оповещающих сигналов;

109

в) множествами подлежащих реализации микропрограмм, устанавливающих в зависимости от входных сигналов управляющие сигналы, выдаваемые блоком в определенные такты.

По множествам входных (v) и выходных (Z) сигналов и микропрограмм определяется множество внутренних состояний УБ: Q = {Q0, Q1,..., Qr},

«мощность» которого (объем памяти и оборудование УБ) в процессе проектирования стараются минимизировать.

Сказанное выше объясняет, почему УБ называют управляющими автоматами. Поскольку эти автоматы задаются микропрограммами, их часто называют микропрограммными автоматами.

УБ может быть задан как автомат Мура:

Q (t + 1) = f [Q (t), v1 (t), v2 (t), ..., vn (t)]; Z1 (t) = φ1 [Q (t)];

Zm (t) = φ m [Q (t)]

или как автомат Мили:

Q (t+1) = f [Q (t)] = f [Q (t), v1 (t), ...vn (t)]; Zi (t) = φi [Q (t), v1 (t), ..., vn (t)],

где f – функция переходов,

φ– функция выходов.

Эти функции определяются заданной микропрограммой.

Существуют два основных метода построения логики УБ:

1. УБ с жесткой или схемной логикой.

Для каждой операции строится набор комбинационных схем и конечный автомат.

2. УБ с хранимой в памяти блока логикой (с запоминаемой или программируемой логикой ).

Каждой выполняемой в обрабатывающем блоке операции ставится в соответствие совокупность хранимых в памяти слов – микрокоманд, содержащих информацию о микрооперациях, подлежащих выполнению в течение одного машинного такта, и указание (в общем случае зависящее от значений входных сигналов) – какая должна быть выбрана следующая микрокоманда. Таким образом, в этом случае функции переходов и выходов f и φ управляющего автомата хранятся в памяти в виде совокупности микрокоманд.

110

Последовательность микрокоманд, выполняющих одну машинную команду или процедуру, образует микропрограмму.

Микропрограммы хранятся обычно в отдельной памяти .

УБ, использующие такой принцип управления, называют микропрограм-

мными (рис. 4.11).

|

Рг К |

КОП . . . . . . . . . . . . . . |

|

|

|

УФАМК |

|

|

|

ПМК |

|

|

|

Рг АМК |

|

|

|

|

Блок |

Микро- |

В |

А |

синхро- |

команда |

|

|

сигналов |

|

|

Рг МК |

|

ДшМО

v1 v2 ..vm

Операционный блок

Структура микрокоманды

|

|

|

Код микрооперации |

|

Адрес следующей |

|

|

микрокоманды |

|

|

|

Операционная часть (В) |

|

Адресная часть (А) |

|

Рис. 4.11 |

|

111

На рисунке использованы следующие обозначения:

Рг К – регистр команды; КОП – код операции;

УФАМК – узел формирования адреса микрокоманды; Рг АМК – регистр адреса микрокоманды; ПМК – память микрокоманд; ДШМО – дешифратор микроопераций.

Применяются следующие типы структуры микрокоманд:

-вертикальная (одна микрооперация в микрокоманде);

-горизонтальная (все возможные микрооперации в микрокоманде);

-горизонтально-полевая, особенностью которой является разбиение структуры микрокоманды на отдельные поля, каждое из которых используется для задания микроопераций управления отдельными блоками и устройствами ЭВМ (памятью, арифметико-логическим устройством и т.д.). При этом внутри полей может применяться вертикальное или горизонтальное кодирование [3, 7]. Для каждого из полей в составе УБ имеется отдельный дешифратор, что позволяет формировать сигналы управления различными устройствами одновременно.

Пример структуры УБ с горизонтально-полевой микрокомандой приведен на рис. 4.12.

Память микрокоманд

Рг Мк

Адресная часть

Дш1 Дш2 ДшК

Операционная часть Рис. 4.12

Для хранения микропрограмм применяются различные виды устройств памяти: статические (ПЗУ), динамические (ОП) и статическо-динамические ЗУ.

112

4.7. Принципы построения устройств памяти

4.7.1. Общие сведения и классификация устройств памяти

Памятью называется совокупность устройств, предназначенных для запоминания и выдачи информации. Отдельные устройства, входящие в эту совокупность, называются запоминающими устройствами (ЗУ), или памятью того или иного типа [3].

Эти термины – ЗУ и память – стали синонимами, теперь термин ЗУ чаще используют, когда хотят подчеркнуть принцип построения (ЗУ на ферритах, ЗУ на магнитных дисках (МД) и т.д.), а память – когда подчеркивают функцию устройства или место его расположения в ЭВМ (основная память, внешняя память и т.д.).

Производительность и вычислительные возможности ЭВМ в значительной степени определяются составом и характеристиками ее ЗУ.

В составе ЭВМ используется одновременно несколько типов ЗУ, отличающихся характеристиками и назначением.

Основные операции, выполняемые в памяти: запись (ввод), считывание (вывод). В зависимости от типа ЗУ за одно обращение может считываться или записываться разный объем информации: байт, слово или блок данных.

Важнейшими характеристиками отдельных устройств памяти являются: емкость памяти, удельная емкость и быстродействие.

Емкость – это максимальное количество данных, которое может храниться в памяти.

Емкость измеряется в кило-, мега- , гига-, терабайтах и т.д.

Удельная емкость – отношение емкости к объему памяти (физическому). Быстродействие – продолжительность операции обращения, т.е. время,

затраченное на поиск информации и ее воспроизведение ( tобрсчит – при чтении и tобрзап – при записи). В некоторых типах ЗУ считывание информации стирает ее и требуется регенерация (восстановление).

Продолжительность обращения (tцикла памяти) при считывании и записи:

tобрсчит = tдостсчит + tсчит + t рег ;

113

tобрзап = tдостзап + tподг + tзап .

В большинстве случаев

tдостсчит= tдостзап = tдост.

В качестве времени цикла обращения к памяти принимается

tобр = max(tобрсчит,tобрзап ),

которое определяет интервал между двумя последовательными обращениями к памяти.

По принципу действия устройства памяти можно разделить на следующие

типы:

-память на электронных схемах;

-на неподвижных ферритовых (магнитных) элементах;

-на подвижных магнитных средах (носителях);

-на лазерных дисках.

Взависимости от реализуемых операций обращения различают:

-память с произвольным обращением (ЧТ/ЗАП);

-память только для считывания или постоянные запоминающие устройства (ПЗУ).

По способу организации доступа память делится:

-на память с непосредственным (произвольным) доступом;

-на память с последовательным доступом.

Эти памяти имеют разное tобр.

ЗУ различаются также по выполняемым функциям, зависящим от места расположения в структуре ЭВМ.

Требования к емкости и быстродействию памяти являются противоречивыми. Чем выше быстродействие, тем технически сложнее и дороже достигается большой объем памяти.

Поэтому память в ЭВМ организуется в виде иерархической структуры ЗУ, обладающих различными быстродействием и емкостью (рис. 4.13).

114

ЦП |

К аппаратуре |

|

|

процессора |

|

|

|

|

|

Сверхопера- |

|

Память |

тивная па– |

|

микропрограмм |

мять (кэш) |

|

|

|

|

Память

Основная память каналов ввода-

вывода

Ядро ЭВМ

Память с |

|

|

|

|

ЗУ на магнитных |

|

|

||

прямым |

|

|

||

дисках |

|

|

||

доступом |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Память с последо- |

ЗУ на магнитных |

вательным доступом |

лентах |

|

|

|

|

Рис. 4.13 |

|

Внутренняя память

Внешняя память

115

4.7.2. Адресная, ассоциативная и стековая организация памяти

Запоминающее устройство, как правило, содержит множество одинаковых элементов, образующих запоминающий массив (ЗМ). Массив разделен на отдельные ячейки, каждая из которых предназначена для хранения двоичного кода, количество разрядов в котором определяется шириной выборки памяти.

Способ организации памяти зависит от методов размещения и поиска информации в ЗМ. По этому признаку различают адресную, ассоциативную и стековую (магазинную) память [3].

Адресная память.

В такой памяти размещение и поиск информации в ЗМ основаны на использовании номера ячейки ЗМ (адреса) хранения слова (команды, числа и т.д.), в которой это слово размещается.

Для записи/чтения слова в ЗМ инициирующая эту операцию команда должна указать адрес (номер ячейки), по которому производится обращение

(ЧТ/ЗП).

Схема памяти с адресной структурой (организацией) изображена на рис. 4.14. Емкость ЗМ – N n-разрядных слов.

Аппаратное обрамление памяти имеет: Рг А – регистр адреса; Рг И – регистр информационный;

БАВ – блок адресной выборки; Дш А – дешифратор адреса;

БУС – блок усилителей считывания; БУЗ – блок усилителей записи; БУП – блок управления памятью; ША – шина адреса.

Цикл работы памяти начинается с поступления в БУП сигнала

«Обращение».

Общая часть цикла «Обращение» включает:

-прием в Рг А адреса ячейки памяти с ША;

-прием в БУП и расшифровку типа операции (ЧТ/ЗП);

-операцию (ЧТ/ЗП).

116

Если физически запись осуществляется со стиранием, то производится регенерация содержимого ячейки ЗУ.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

БУС |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

n-1 |

Считывание |

|

||

|

|

|

|

|

|

|

|

|

|

|

Ши Вх |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

n-1 |

|

|

|

|

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

k-1 |

|

БАВ |

· |

|

|

|

|

|

|

|

ША |

|

|

|

|

0 |

|

n–1 |

||||

|

|

|

|

|

|

||||||

Рг А |

|

|

|

ЗМ |

|

|

Рг И |

|

|||

|

|

|

|

|

|

|

|||||

|

0 |

|

ДшА |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

N–1  .

.

Ши Вх

Пр Рг И

Пр Рг А Выборка |

|

|

|

||

Обра- |

|

|

|

|

|

БУП |

|

|

|

БУЗ |

|

щение |

|

|

|

||

|

|

Запись |

0 |

n–1 |

|

ЧТ/ЗП |

|

|

|

|

|

|

|

|

|

|

|

Пр Ши Вых

Рис. 4.14

117