- •Интерфейсы жестких дисков

- •Интерфейс ATA

- ••Хост-контроллер (хост-адаптер) взаимодействует с контроллером винчестера по специальному протоколу

- •Эволюция ATA. Версии интерфейса

- ••ATA/ATAPI-4:

- ••Интерфейс Serial ATA является наследником ATA/ATAPI, но по сути разработан и поддерживается другой

- •Электрический интерфейс ATA

- ••Проверив заземление на 28 контакте, винчестер может определить, является ли он Master

- •Описание сигналов ATA

- •Переопределение сигналов в режиме Ultra DMA

- •Регистры устройства ATA

- •Блок командных регистров

- ••011 R/W: SN (Sector Number) – номер сектора (CHS) или биты [0:7] адреса

- ••111 R: SR (Status Register) – регистр состояния. Чтение регистра вызывает сброс некоторых

- •Блок управляющих регистров

- •Адресация секторов

- •Адресация CHS

- •Адресация LBA

- •Команды. Общая информация

- •Протокол 1: PIO In

- •Протокол 2: PIO Out

- •Протокол 3: DMA

- •Режимы обмена данными

- •Параметры режимов PIO

- •Режимы DMA и UDMA

- •Параметры режимов DMA/Ultra DMA

- •Дополнительные функции ATA

- •Шина SCSI

- •Архитектурная модель SCSI

- ••Помимо классического транспортного протокола SIP (SCSI Interlocked Protocol), архитектурная модель предполагает использование других

- •Архитектурная модель SCSI

- •Применение SCSI для подключения жестких дисков

- •Отличия между SCSI и ATA

- ••Интерфейс SCSI:

- •Электрический интерфейс SCSI SPI

- ••Существует несколько видов кабелей и разъемов для параллельного интерфейса SCSI

- ••Кабели:

- •Сигналы интерфейса SPI SCSI

- •Адресация шины SCSI

- •Фазы шины

- •–Message: фаза сообщений используется для управления шиной. Сообщения бывают однобайтными, двухбайтными и расширенными

- •Порядок следования фаз при обмене данными

- •Порядок следования фаз при возобновлении обмена

Интерфейсы жестких дисков

ATA: история, сигналы, регистры, адресация, команды, протоколы.

SCSI: архитектура, сигналы, разъемы и кабели, команды, адресация, фазы

Интерфейс ATA

•Разрабатывался в конце 80-х годов ХХ века для подключения жестких дисков со встроенными контроллерами к шине ISA

•Особенность интерфейса состоит в переносе собственно контроллера стандарта AT на плату электроники, закрепленную на жестком диске (IDE – Integrated Drive Electronics, привод со встроенной электроникой)

•Сам интерфейс с электрической точки зрения представляет собой упрощенный вариант шины ISA

•Сохранены следующие механизмы и сигналы ISA:

–16-битная шина данных;

–3 бита шины адреса для адресации регистров;

–аппаратный сброс, готовность, разрядность обмена;

–сигнал прерывания;

–сигналы чтения/записи портов;

–сигналы DMA.

•Хост-контроллер (хост-адаптер) взаимодействует с контроллером винчестера по специальному протоколу

•Переход к локальным шинам (VLB, PCI) и встраивание хост-контроллера в чипсет не повлияло на интерфейс – он остался прежним

•Лишь введение интерфейса Serial ATA позволило избавиться от наследия ISA; протокол ATA был расширен, но совместимость сохранена

•Протокол ATA (регистры, команды и т.п.) ориентирован на обмен данными только с жестким диском. Регистры заполняются адресами секторов, команды учитывают особенности винчестеров

•Расширение ATAPI позволяет с помощью отдельной команды пересылать командный пакет большого объема и содержания

Эволюция ATA. Версии интерфейса

•Разработкой и стандартизацией интерфейса ATA/ATAPI занимается рабочая группа T13 института INCITS, входящего в организацию ANSI

•Исходный стандарт ATA описывал 16-битный параллельный интерфейс с 40-контактными интерфейсными разъемами и поддержкой 2 винчестеров. Скорость обмена данными – до 8 Мб/с

•ATA-2, он же Fast ATA, он же EIDE:

–До 4 устройств – 2 канала по 2 устройства

–16.6 Мб/с, режимы PIO Mode 4 и MW DMA Mode 2

•ATA-3:

–SMART

–Пароли и безопасность

–APM

–Другие дополнения протокола

•ATA/ATAPI-4:

–Пакетный протокол ATAPI

–Режимы Ultra DMA Mode 0, 1 и 2

–Защита передаваемых данных кодами CRC

•ATA/ATAPI-5:

–Удаление устаревших команд и битов

–Новые режимы защиты и управления

–Режимы Ultra DMA Mode 3, 4

–80-жильный кабель

•ATA/ATAPI-6:

–Режим Ultra DMA Mode 5

–AAM

–A/V Streaming Command Set

•ATA/ATAPI-7:

–Последняя версия стандарта

–Режим Ultra DMA Mode 6

–Обновление команд Streaming

•Интерфейс Serial ATA является наследником ATA/ATAPI, но по сути разработан и поддерживается другой организацией – Serial ATA International Organization (SATA-IO), бывшая Serial ATA Working Group

•Serial ATA должен войти в спецификацию ATA/ATAPI-7 ревизии 3

•Первая официальная версия – 1.0а, потом была ревизия 1.2, последняя – 2.5

•Низковольтный дифференциальный (LVDS) последовательный интерфейс сменил параллельный интерфейс с TTL-уровнями

•Добавлены теневые (shadow) регистры, расширяющие возможности регистров ATA

•Множество новых функций управления, масштабирования, расширения

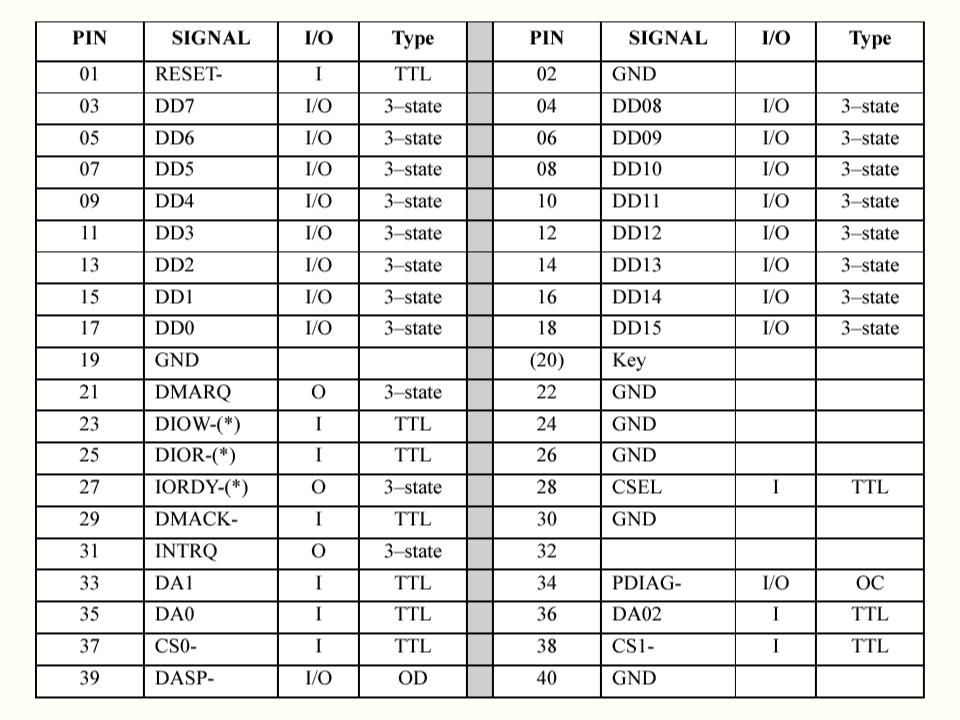

Электрический интерфейс ATA

•Сигналы ATA имеют уровни TTL:

–Высокий уровень входного (для винчестера) сигнала – от 2 до 5.5 В

–Высокий уровень выходного сигнала – выше 2.4 В

–Низкий уровень входного сигнала – от -0.5 до 0.8 В

–Низкий уровень выходного сигнала – ниже 0.5 В

•Разъем для настольных винчестеров имеет 40 контактов, плоский шлейф состоит из 40 или 80 проводников; имеется отдельный разъем питания (GND, +5, +12)

•Разъем для мобильных винчестеров имеет 44 контакта, так как включает питание (+5, ПТВ)

•Длина кабеля – не более 0.46 м

•Три разъема на кабеле

•Выбор ведущего устройства (Master) осуществляется либо перемычками, либо разъемом кабеля. Средний разъем имеет неподключенным контакт 28

•Проверив заземление на 28 контакте, винчестер может определить, является ли он Master

•80-жильный кабель чередует сигнальные линии и линии заземления

•Контакт 34 на стороне хост-разъема не подключен, что позволяет устройствам проверять, имеется ли 80- жильный кабель

•Необходимость увеличения количества жил связано с повышением требований к помехозащищенности интерфейса на больших частотах обмена (режимы Ultra DMA)

Описание сигналов ATA

•DD00-DD15 – данные между хостом и винчестером; двунаправленные трехстабильные линии

•DA00-DA02 – выбор регистра, младшие линии шины адреса ISA

•CS0# - выбор блока командных регистров (Command Block Registers), вырабатывается в зависимости от порта, к которому обращается процессор

•CS1# - выбор блока управляющих регистров (Control Block Registers)

•Reset# - аппаратный сброс устройства

•DIOW# - строб записи в регистры устройства, фиксируется по положительному перепаду

•DIOR# - строб чтения из регистров, фиксируется по положительному перепаду

•INTRQ – запрос прерывания, вырабатывается устройством для сигнализации об очередном блоке данных (режим PIO) или об окончании обмена DMA (режим DMA). Может быть запрещен битом IEN# регистра Device Control. Сбрасывается при чтении регистра Status и при записи команды в регистр Command

•DASP# - используется как индикатор активности для работы соответствующего светодиода. Во время сброса с его помощью проверяется наличие устройства Slave

•PDIAG# - информация от устройства Slave устройству Master о прохождении диагностики. Master следит за сигналом во время сброса и команды самодиагностики, чтобы определить исправность Slave. Хост-контроллер сигнал не использует

•CSEL – сигнал выбора Master/Slave. На хост-контроллере заземлен, на разъеме Master подключен, на Slave – нет. Устройство проверяет уровень и настраивается на работу как Master или Slave

•IORDY – сигнал снимается устройством во время обмена данными для паузы (тактов ожидания), а потом поднимается при готовности

•DMARQ – сигнал готовности устройства к обмену по протоколу DMA. В режимах MW и Ultra DMA удерживается на протяжении всего цикла

•DMACK# - подтверждение готовности от хоста, без которого обмен DMA не начинается