- •Шины и интерфейсы

- •Архитектура подсистемы ввода-вывода ПК

- •Архитектура HyperTransport

- •Шины

- •Архитектура PCI Express

- •PCI Express

- •Архитектура PCI

- •Шина PCI

- ••Команда, от которой зависит тип транзакции, передается по отдельным линиям

- •Конструктивное исполнение разъемов PCI

- •Малогабаритные форматы PCI-карт

- •PCMCIA/PC Card

- •Шина USB

- •Архитектура

- •Протокол обмена данными

- •–Все транзакции начинаются по инициативе хоста при посылке маркера транзакции (ввод, вывод, управление,

- •Физический интерфейс

- •Шина FireWire

- •Архитектура FireWire

- •Протокол обмена данными

Шины и интерфейсы

(Очень краткая информация)

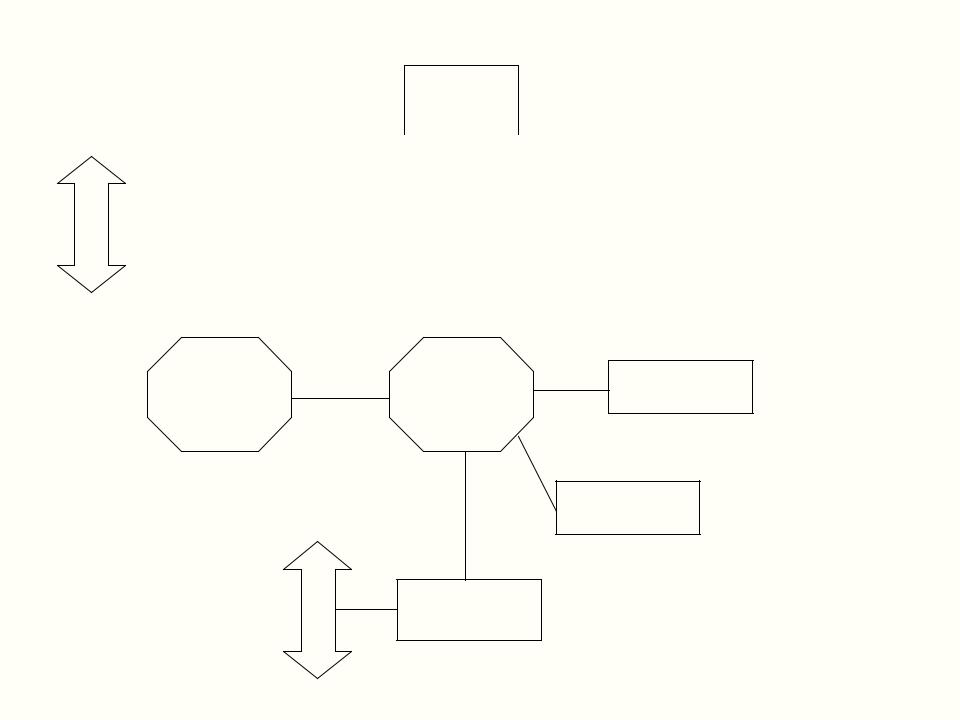

Архитектура подсистемы ввода-вывода ПК

Центральный |

Центральный |

процессор |

процессор |

|

|

FSB

AGP/PCIe |

Системный |

ОЗУ |

|

мост |

|||

|

|

USB |

Периферийный |

PCI/PCIe |

|

|

|||

(S|P)ATA |

мост |

||

|

COM, LPT, PS/2… |

Мост |

ввода-вывода |

|

|

|

Архитектура HyperTransport

ОЗУ |

Центральный |

Центральный |

ОЗУ |

|

процессор |

процессор |

|||

|

|

Тоннель AGP/PCIe AGP/PCIe

USB |

Периферийный |

PCI/PCIe |

|

|

|||

(S|P)ATA |

тоннель |

||

|

COM, LPT, PS/2… |

Мост |

ввода-вывода |

|

|

|

Шины

•Архитектура ПК является иерархической и многоуровневой

•Периферийная подсистема построена на основе локальной периферийной шины, работающей по принципу системной шины

•Системная шина использует плоскую глобальную адресацию. Всем устройствам доступно пространство адресов и портов ввода/вывода

•Текущая локальная периферийная шина – PCI Express. Поддержка PCI сохраняется, но эта шина является одной из вторичных шин в архитектуре

•Иерархичность подсистемы ввода-вывода обеспечивается именно периферийной шиной

Архитектура PCI Express

ЦП

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Мост |

|

|

Корневой |

|

|

|||

|

|

|

|

Точка PCIe |

|||||

|

PCI-PCIe |

|

|

комплекс |

|

||||

|

|

|

|

||||||

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Коммутатор |

Коммутатор |

Точка PCIe |

|

Точка PCIe

Мост другой шины

PCI Express

•Логическая модель унаследована от PCI

•Каждый канал PCI Express представлен как мост PCI

ивторичная шина PCI со своим номером

•Конфигурирование и адресация – по аналогии с PCI

•Уровни:

–Транзакций: пакеты TLP содержат данные, адрес (память, порт, идентификатор), тип транзакции (команда PCI), дополнительный CRC-код

–Канальный: пакеты DLLP содержат номер и CRC, требуют ответа от приемника

–Физический уровень: кодирование 8b/10b, символы синхронизации

–Электрический уровень: две дифференциальные пары, опорная частота (100 МГц), сброс, пробуждение, сигналы горячего подключения, питание (+3.3, +12, +3.3Vsb)

–Частота обмена данными – 2.5 ГГц

Архитектура PCI

ЦП

Главный

мост

Мост |

|

Мост |

|

Мост |

|

Устройство |

PCI-PCI |

|

PCI-LPC |

|

PCI-… |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

Устройство |

Устройство |

Устройство |

|

LPC |

|||

|

|

Шина PCI

•Устройство может выполнять роль как приемника (Target), так и инициатора (Master)

•Bus-master device – устройство, способное инициировать обмен. Не все устройства на это рассчитаны

•Обмен выполняется циклами – транзакциями

•Чтобы получить доступ к шине, устройство должно послать сигнал REQ

•Доступ дает арбитр, встроенный в мост, обслуживающий данный сегмент шины

•Сегменты шины разделены мостами, которые отвечают за арбитраж, маршрутизацию и управление потоками данных

•Транзакция состоит из фаз арбитража, адресации (к портам или пространству адресов) и передачи данных

•Команда, от которой зависит тип транзакции, передается по отдельным линиям

•Устройство может обращаться к портам ввода- вывода, памяти или регистрам конфигурации

•Конфигурирование через регистры конфигурации выполняет только главный мост. Цикл доступа к конфигурации использует специальную адресацию

•Существует специальный цикл для широковещательных сообщений

•Данные передаются по 32 бита, часть байт можно замаскировать, если адрес или пакет не выровнен по границе двойного слова

•Длина транзакции заранее неизвестна, ее определяет инициатор сигналом FRAME#

•Частота шины PCI – 33 МГц, существуют варианты с частотой 66 МГц. Поддерживаются изначально 64- битный режим работы и 64-битная адресация по 32- битной шине

•Прерывания передаются либо через сигналы INTA#- INTD#, которые через мосты доводятся до контроллера прерываний, либо сообщениями – циклами записи в порты контроллера прерываний

•Транзакция может быть отложена (инициатору сообщен отказ) сигналом STOP#, инициатор должен повторно выполнить запрос

•Разделенные транзакции, адресация по идентификатору, ускорение обмена данными реализованы в шине PCI-X