- •1. Классификация аналоговых электронных устройств.

- •2. Основные параметры усилительных устройств.

- •3. Основные характеристики усилительных устройств.

- •4. Режимы работы усилительных каскадов: а, в, ав.

- •5. Задание рабочей точки биполярного транзистора (бт) в схеме с фиксированным током базы. Основные расчетные соотношения.

- •6. Задание рабочей точки бт в схеме с фиксированным напряжением база-эмиттер. Основные расчетные соотношения.

- •7. Стабилизация рабочей точки бт в схеме с коллекторной стабилизацией. Основные расчетные соотношения.

- •8. Стабилизация рабочей точки бт в схеме с эмиттерной стабилизацией. Основные расчетные соотношения.

- •9. Эквивалентные представления усилительного каскада в виде управляемого источника напряжения и управляемого источника тока.

- •10.Ук на бт с оэ в области средних частот: эквивалентная схема, вх и вых сопротивление, ку по току и апряжению.

- •11. Ук на бт с об в области средних частот: эквивалентная схема, вх и вых сопротивление, ку по току и напряжению.

- •12 Ук на бт с ок (эмиттерный повторитель) в области средних частот. Эквивалентная схема, входное и выходное сопротивление, коэффициент усиления по току и напряжению.

- •13. Обратные связи в усилительных устройствах: основные понятия, классификация.

- •14. Коэффициент передачи усилителя охваченного ос. Влияние обратных связей на параметры и характеристики усилителя.

- •15. Сравнительная характеристика параметров ук на бт с оэ, ок и об: коэффициенты усиления по току и напряжению, входное и выходное сопротивление, полоса пропускания.

- •16. Усилительные каскады на пт с общим истоком.

- •17. Усилители постоянного тока (упт) на бт: способы устранения дрейфа нуля, согласование уровней постоянного напряжения между каскадами.

- •18. Двухтактный бестрансформаторный оконечный каскад в режиме класса в. Переходные искажения.

- •19. Двухтактный бестрансформаторный оконечный каскад в режиме класса ав.

- •20.Дифференциальные усилительный каскад: принцип действия.

- •21.Дифференциальный усилительный каскад : вх и вых сопротивление, коэффициенты усиления синф. И диф. Сигналов, Косс.

- •22. Способы улучшения параметров дифференциальных усилительных каскадов.

- •23. Классификация и параметры операционных усилителей(оу).

- •24. Инвертирующий усилитель на оу.

- •25. Неинвертирующий усилитель на оу.

- •26. Схема сумматора на оу.

- •27. Дифференцирующий усилитель на оу.

- •28. Интегрирующий усилитель на оу.

- •29. Логарифмирующий усилитель на оу.

- •30. Антилогарифмирующий усилитель на оу.

- •31 . Ключ на бт: принципиальная схема, передаточная характеристика, статический режим работы.

- •32 . Ключ на бт: принципиальная схема, динамический режим работы.

- •33. Способы повышения быстродействия ключей на бт

- •34. Ключи на мдп-транзисторах

- •35. Ключ на комплементарных мдп-транзисторах

- •36.Логические элементы, логические функции, основные законы алгебры логики

- •37.Принцип построения лог. Элементов на основе полупроводниковых диодов.

- •37.Принцип построения лог. Элементов на основе полупроводниковых диодов.

- •38.Базовый логический элемент транзистрно-транзисторной логики (ттл).

- •39. Базовый логический элемент эммитерно-связанной логики (эсл).

- •40.Интегрально-инжекционная логика.

- •41. Основные параметры являются общими для всех существующих и возможных логических имс и позволяют сравнивать между собой микросхемы различных типов. Основными параметрами являются:

- •42.Rs–триггер

- •43. Синхронный rs-триггер.

- •44. D-триггер

- •45. Т-триггер

- •46.Jk-триггер

- •47.Мультивибратор на логических элементах

- •48.Особенности диапазона свч. Деление свч диапазона на поддиапазоны.

- •49. Особенности эп свч с динамическим управлением электронным потоком. Общий принцип действия и характеристики эп свч.

- •50. Конструкция, принцип действия и параметры двухрезонаторного пролетного клистрона.

- •51. Устройство и принцип действия лампа бегущей волны о-типа (лбво)

- •52.Конструкция, принцип действия и условия самовозбуждения лампа обратной волны о-типа

- •53.Движение электронов в скрещенных постоянных электрическом и магнитном полях.

- •54.Конструкция,принцип действия, амплитудное и фазовое условия самовозбуждения многорезонаторного магнетрона. Парабола критического режима.

- •55. Диоды Ганна. Эффект Ганна. Особенности многодолинных полупроводников.

- •56. Автогенераторы на диодах Ганна. Конструкции, эквивалентная схема. Режимы работы. Параметры генераторов, области применения.

- •58. Оптические квантовые генераторы (лазеры) на твердом теле: конструкция, принцип действия, параметры, области применения.

37.Принцип построения лог. Элементов на основе полупроводниковых диодов.

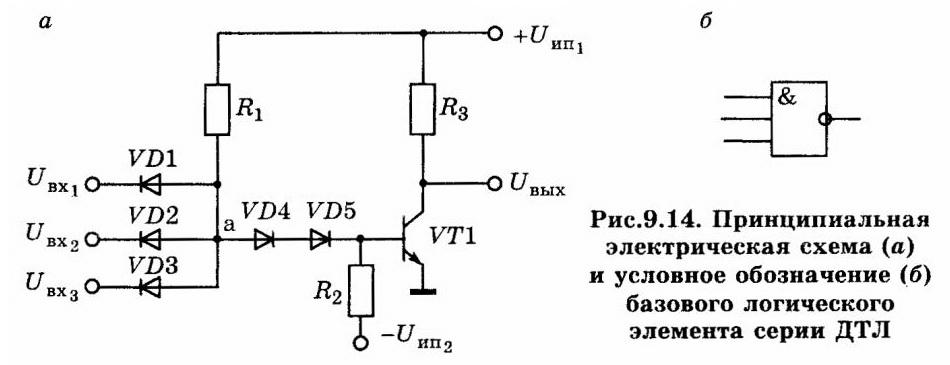

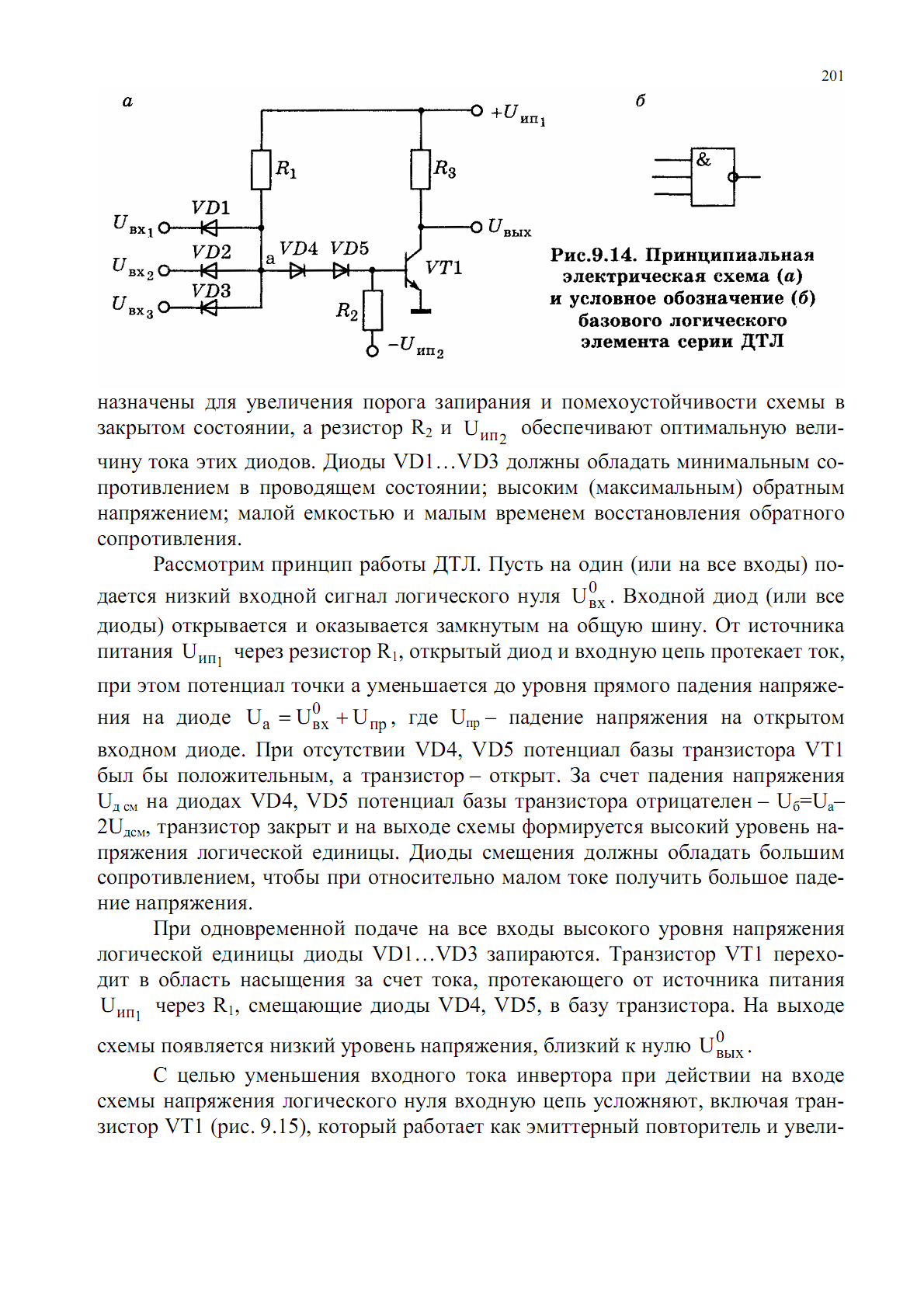

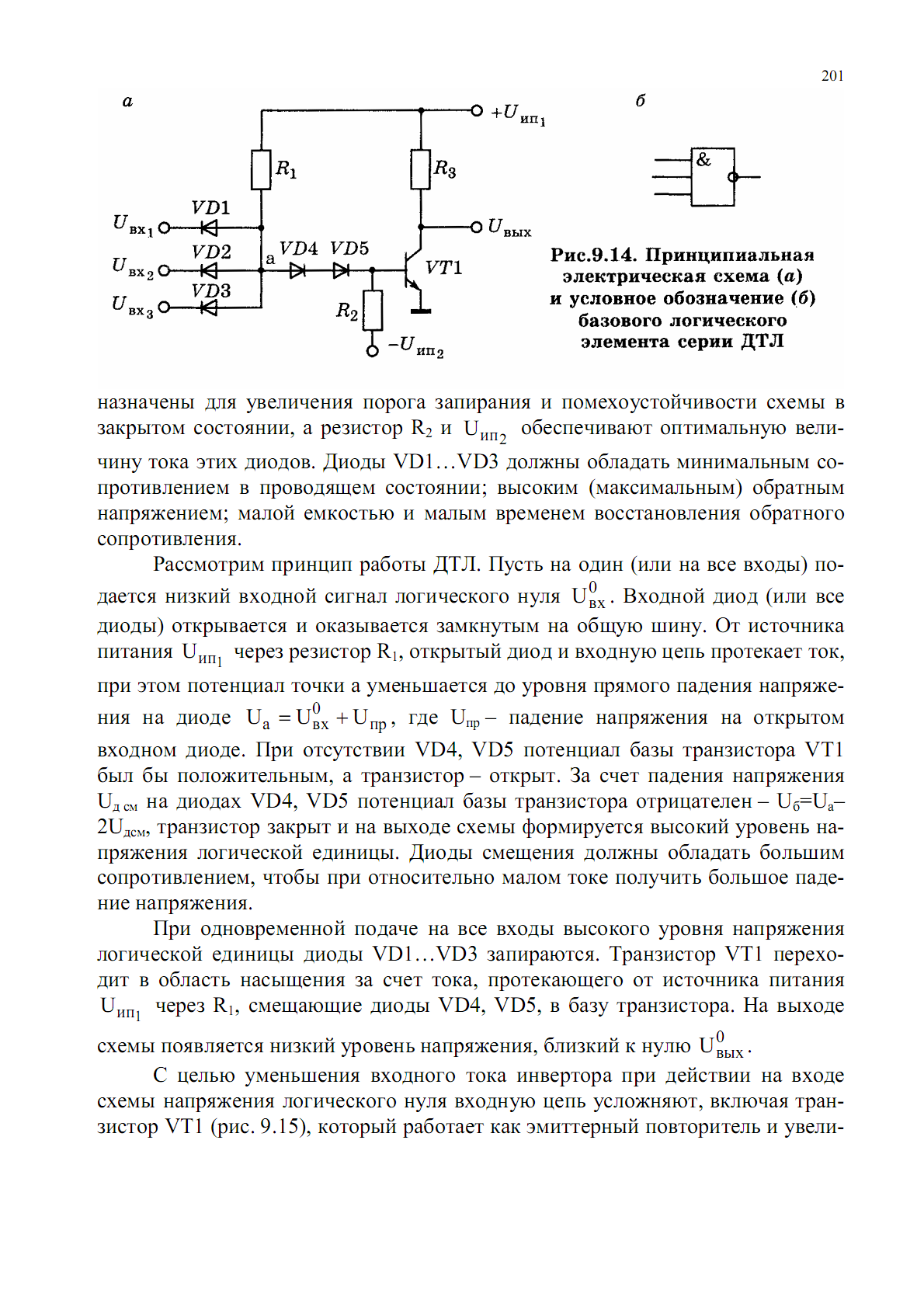

Диодно–транзисторная логика (ДТЛ) представляет собой сочетание ди-

одных логических ячеек с транзисторным инвертором. Базовым логическим

элементом всех серий ДТЛ является элемент Шеффера (элемент И–НЕ), реали-

зующий операцию логического умножения с отрицанием.

Схема логического элемента ДТЛ представлена на рис. 9.14. Входные диоды VD1…VD3 и резистор R1 образуют входную логическую схему, выполняющую в положительной логике операцию И. Инвертор на транзисторе VТ1 выполняет логическую операцию НЕ, усиливает и формирует сигналы на выходе до стандартного уровня. Смещающие диоды VD4 и VD5 пред назначены для увеличения порога запирания и помехоустойчивости схемы в закрытом состоянии, а резистор R2 и

U2ип обеспечивают оптимальную величину тока этих диодов. Диоды VD1…VD3 должны обладать минимальным сопротивлением в проводящем состоянии; высоким (максимальным) обратным напряжением; малой емкостью и малым временем восстановления обратного сопротивления.

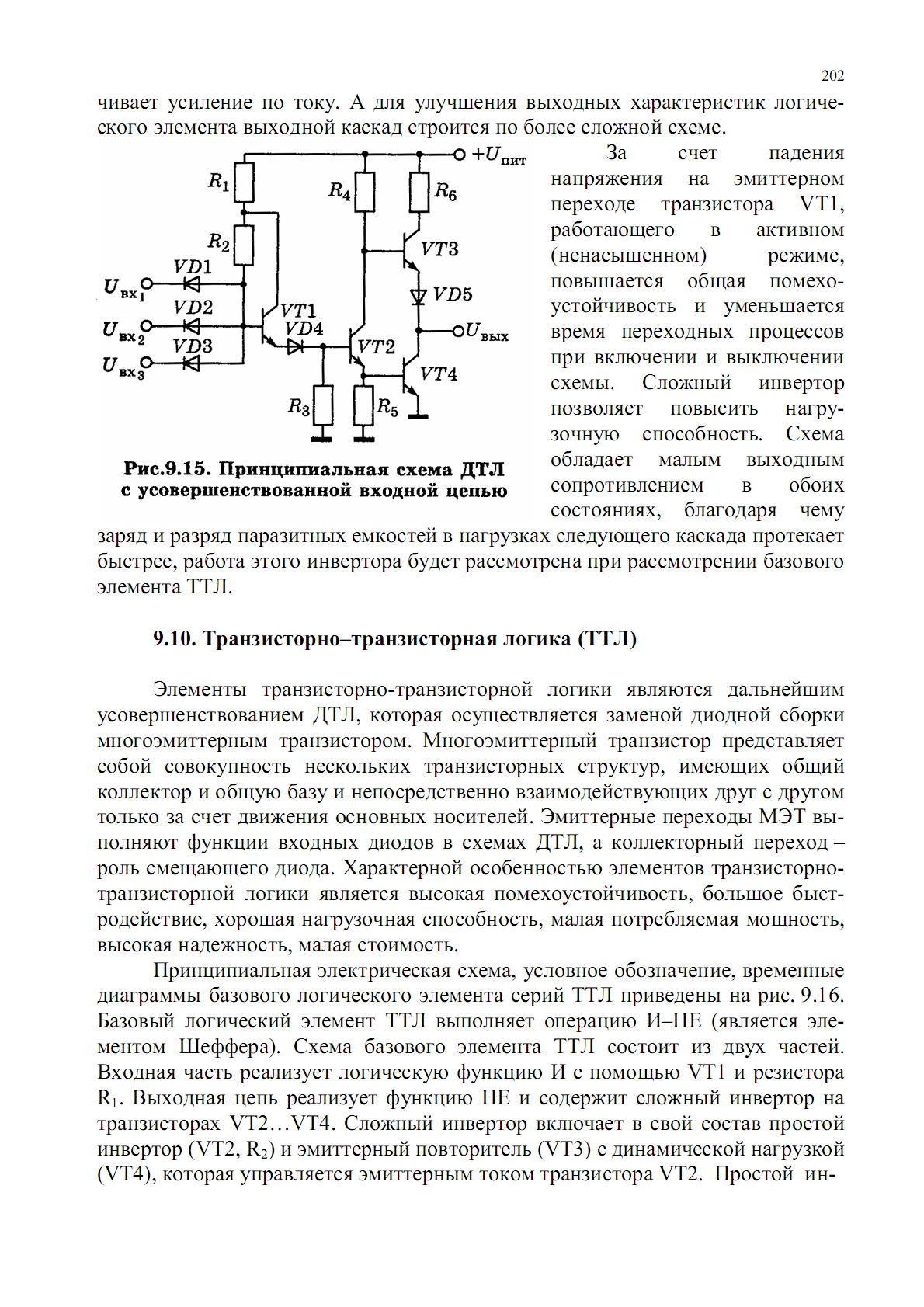

38.Базовый логический элемент транзистрно-транзисторной логики (ттл).

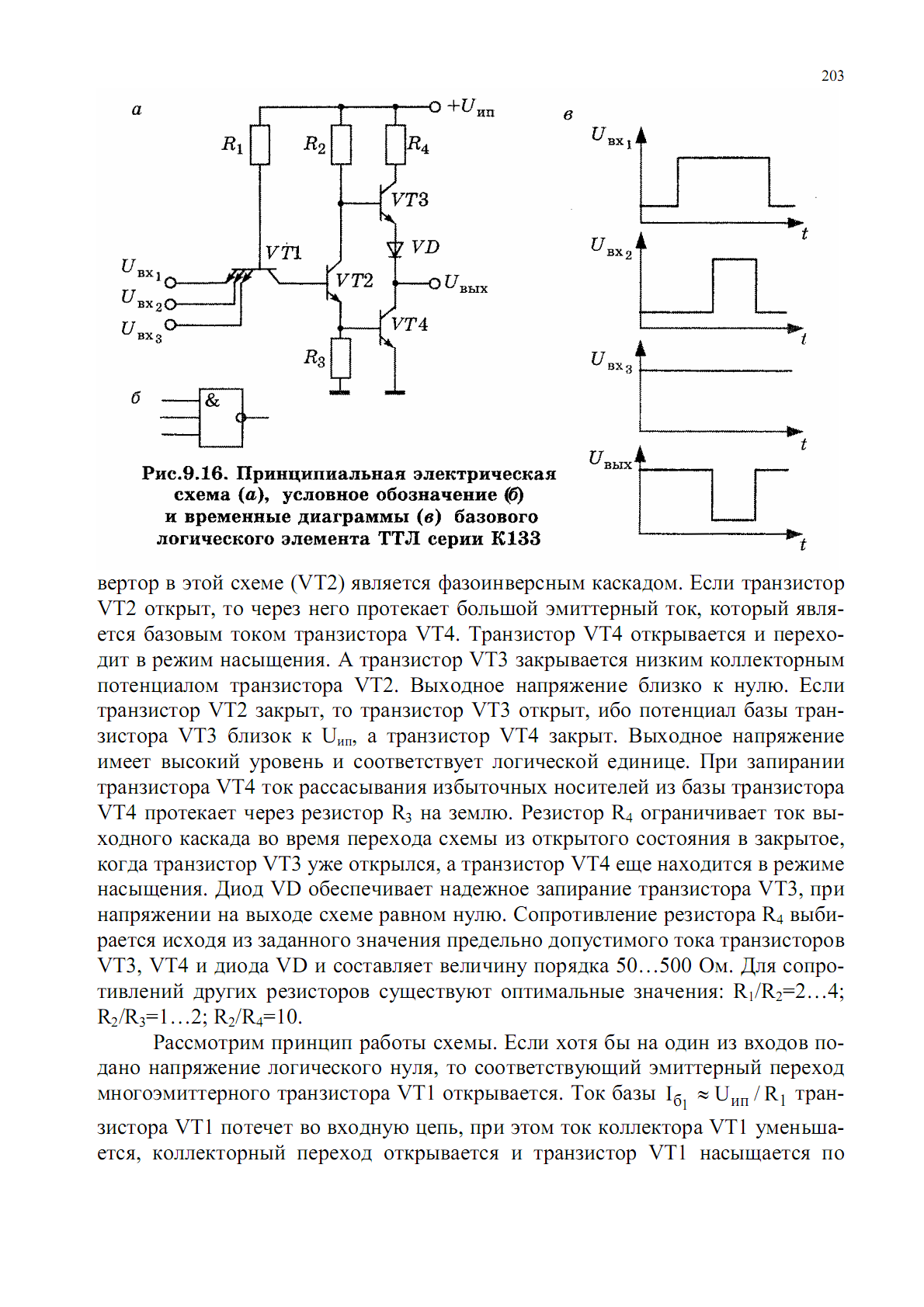

Принципиальная электрическая схема, условное обозначение, временные диаграммы базового логического элемента серий ТТЛ приведены на рис 9.16. Базовый лог элемент ТТЛ выполняет операцию И–НЕ (является элементом Шеффера). Схема базового элемента ТТЛ состоит из двух частей. Входная часть реализует лог функцию И с помощью VТ1 и резистора R1. Выходная цепь реализует функцию НЕ и содержит сложный инвертор на транзисторах VТ2…VТ4.

Базовые элементы различных серий ТТЛ различаются только инверторами, которые должны улучшать переходные характеристики, повышать помехоустойчивость и нагрузочную способность, потреблять небольшую мощность.

Для уменьшения входных токов транзистор VТ1 должен обладать малым ко-

эффициентом передачи тока базы в инверсном режиме h i э 21 ≈0,005…0,05 .

Логические элементы со сложным инвертором потребляют большую

мощность, занимают большую площадь кристалла, поэтому на их основе изготавливаются цифровые микросхемы малой и средней степени интеграции.

Быстродействие логических элементов различных серий ТТЛ можно повысить двумя путями:

– уменьшая сопротивление резисторов и паразитные емкости;

– обеспечивая работу транзисторов в активном, т.е. ненасыщенном режиме, при котором отсутствует накопление и рассасывание носителей в базах транзисторов. Оба эти способа повышения быстродействия нашли практическое применение.

39. Базовый логический элемент эммитерно-связанной логики (эсл).

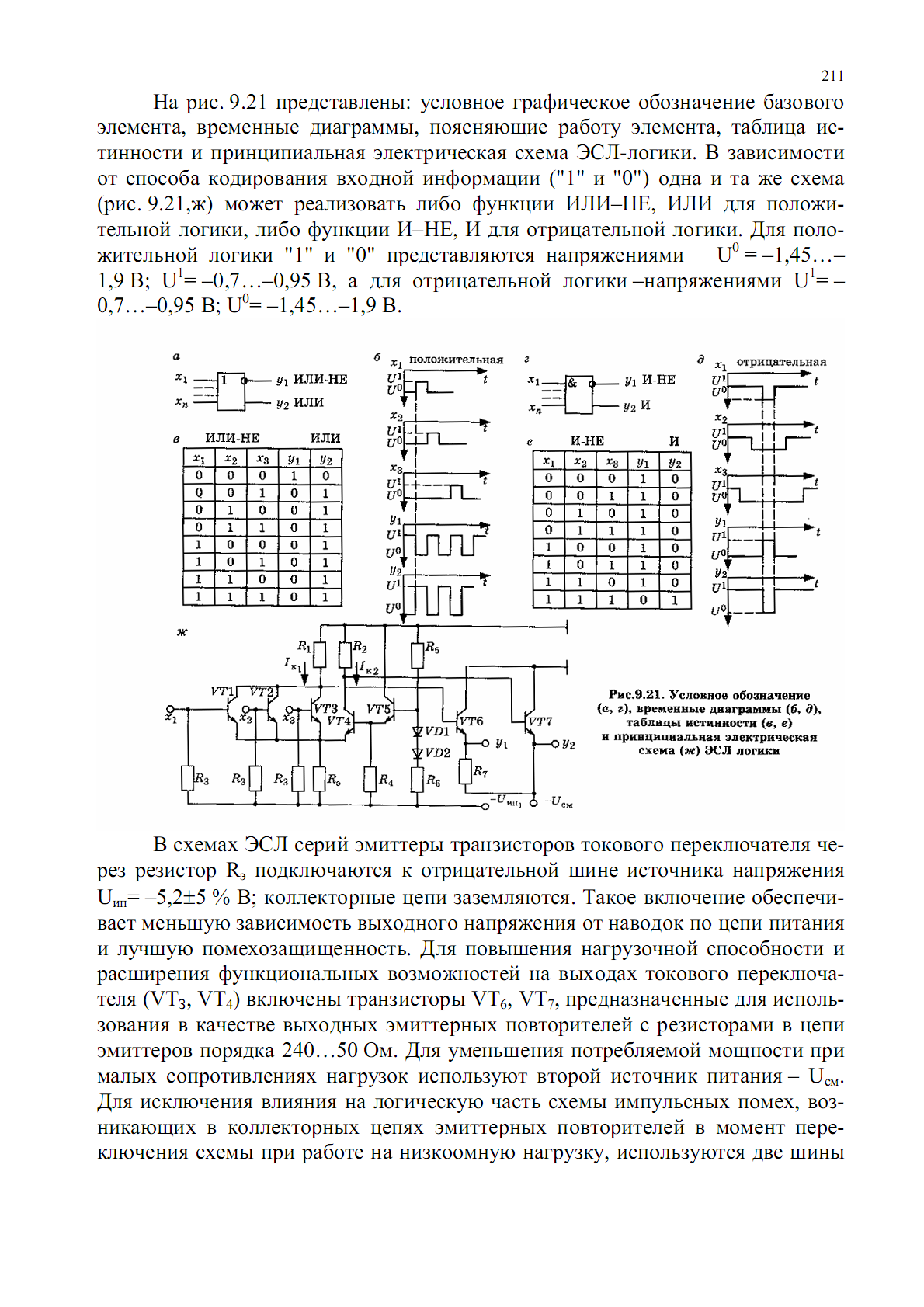

Цифровые микросхемы эмиттерно–связанной логики составляют схемы на переключателях тока с объединенными эмиттерами, обладающие по сравнению с другими типами цифровых схем наибольшим быстродействием и большой потребляемой мощностью.

Большое быстродействие ЭСЛ логики обеспечивается:

– за счет работы транзисторов в ненасыщенном (линейном) режиме;

– за счет применения на выходах схемы эмиттерных повторителей, ускоряющих процесс заряда и разряда нагрузочных емкостей;

– за счет ограничения перепада выходного напряжения, что приводит к снижению статической помехоустойчивости.

Логический элемент состоит из трех частей: токового переключателя

(ТП), эмиттерных повторителей (ЭП), источника опорного напряжения (ИОН).

Рассмотрим принцип работы базового лог элемента для положительной логики. Если на все логические входы подается напряжение низкого уровня, соответствующее логическому нулю, то транзисторы VТ1–VТ3 закрываются, а транзистор VТ 4 открывается, так как напряжение на его базе становится выше, чем на базах входных транзисторов. Через открытый транзистор протекает ток Iк2, значение которого задается резистором Rэ, и создает падение напряжения на резисторе R2. Потенциал коллектора транзистора VТ4 при этом понижается и подается на вход эмиттерного повторителя, собранного на транзисторе VТ7. На выходе эмиттерного повторителя получается низкий уровень напряжения, соответствующий логическому нулю.

В это же время через резистор R1 левой ветви токового ключа протекает небольшой обратный ток Iк1. Потенциал коллектора транзистора VТ3 повышается и поступает на базу эмиттерного повторителя транзистора VТ6. На выходе транзистора VT6 имеем большой потенциал, логическую единицу, при этом выполняется логическая операция ИЛИ–НЕ.