- •1.Общие сведения о пэвм.

- •3.Принципы взаимодействия основных частей пэвм.

- •4. Общие сведения об операционных системах, применяемых на пэвм.

- •5.Базовая система ввода/вывода (bios). Подсистема post.

- •Вопрос 9.Файловая система fat

- •10) Ntfs

- •11)Резидентные системные программы и утилиты. Командные файлы, файлы конфигурации системы

- •Файл autoexec.Nt

- •Файлы winstart.Bat и dosstart.Bat

- •Файл config.Nt

- •12. Прерывания дисковой системы пэвм.

- •14. Назначение, структурная схема и программирование контроллеров нdd.

- •15. Назначение и состав системы ввода-вывода.

- •19. Организация обмена данными через параллельные порты.

- •20. Характеристики микропроцессоров intel и amd

- •21. Математические сопроцессоры.

- •1. Регистры ммх

- •2. Типы данных ммх

- •3. Команды пересылки данных ммх

- •4. Команды преобразования типов ммх

- •5. Арифметические операции ммх

- •6. Команды сравнения ммх

- •7. Логические операции ммх

- •8. Сдвиговые операции ммх

- •9. Команды управления состоянием ммх

- •10. Расширение amd 3d

- •25. Модель микропроцессора для программиста.

- •Реальный режим общие сведения

- •26. Спецификация регистров микропроцессора. Режимы работы. Типы данных.

- •Реальный режим общие сведения

- •Работа с адресами

- •Обработка прерываний

- •27. Системные регистры.

- •Регистры управления памятью

- •Регистры управления процессором

- •Отладочные регистры

- •Машинно-специфичные регистры

- •31. Системные ресурсы пэвм

- •32. Дескрипторы

- •33. Сегмент состояния задачи

- •35. Прерывания пэвм

- •Исключения в защищённом режиме

- •Обработка аппаратных прерываний

- •39. Контроллер прерываний. Исключения.

- •42 Полупроводниковые пзу, рпзу.

- •43 Сегментация. Физические и логические адреса.

- •Общие сведения

- •Работа с адресами

- •Обработка прерываний

- •Вход в защищённый режим(286)

- •2.1. Подготовка к переключению в защищённый режим

- •2.2. Переключение в защищённый режим

- •2.3. Возврат в реальный режим

- •47 Режим виртуального процессора i8086

- •48 Преобразование адресов

- •Программирование микросхемы таймера 8253/8254.

- •50.Каналы и управление таймеров. Микросхемы таймера 8253/8254

- •Средства ms-dos для работы с таймером

- •51.Режимы работы таймеров. Микросхемы таймера 8253/8254

- •52.Назначение, структурная схема контроллера пдп(dma).

- •53 Программирование контроллера пдп(dma).

- •54 Организация ввода данных с клавиатуры.

- •56. Прерывания и порты клавиатуры.

- •58. Прерывания видеосистемы.

- •59.Организация вывода информации на экран дисплея через память видеоадаптера.

- •60. О рганизация вывода информации на экран дисплея через прерывания. Прерывания dos

- •Прерывания bios

- •Int 10h

- •Int 1Dh

- •Int 1Fh

Общие сведения о ПЭВМ, классификация, основные характеристики.

Архитектура 16, 32, 64 разрядных ПЭВМ.

Принципы взаимодействия основных частей ПЭВМ.

Общие сведения об операционных системах, применяемых на ПЭВМ.

Базовая система ввода/вывода (BIOS). Подсистема POST.

Понятие о многозадачности.

Классы приоритетов. Драйверы.

Принципы построения файловой системы.

Файловая система FAT

Файловая система NTFS.

Резидентные системные программы и утилиты. Командные файлы, файлы конфигурации системы.

Прерывания дисковой системы ПЭВМ.

Назначение, структурная схема и программирование контроллеров НГМД.

Назначение, структурная схема и программирование контроллеров НDD.

Назначение и состав системы ввода-вывода.

Параллельный порт.

Последовательный порт.

Организация обмена данными через последовательные порты

Организация обмена данными через параллельные порты.

Архитектура, характеристики микропроцессоров Intel, AMD.

Математические сопроцессоры.

Расширения MMX.

Расширения SSE.

Системная логика ПК(чипсеты).

Модель микропроцессора для программиста.

Спецификация регистров микропроцессора. Режимы работы. Типы данных.

Системные регистры.

Регистр флагов.

Регистры для работы в защищенном режиме.

Регистры для работы в реальном режиме.

Системные ресурсы ПЭВМ.

Дескрипторы.

Сегмент состояния задачи.

Карта ввода-вывода.

Прерывания ПЭВМ.

Аппаратные, логические и программные прерывания.

Таблица векторов прерываний в реальном режиме.

Таблица векторов прерываний в защищенном режиме

Контроллер прерываний. Исключения.

Организация памяти ПЭВМ.

Оперативная память ПК, характеристики, конструктивное исполнение.

Полупроводниковые ПЗУ, РПЗУ.

Сегментация. Физические и логические адреса.

Реальный режим работы с памятью.

Принципы переключения режимов работы с памятью.

Защищенный режим работы с памятью.

Виртуальный режим работы с памятью.

Управление страничной памятью.

Таймер ПЭВМ.

Каналы и управление таймеров.

Режимы работы таймеров.

Назначение, структурная схема контроллера ПДП(DMA).

Программирование контроллера ПДП(DMA).

Организация ввода данных с клавиатуры.

Функции BIOS и операционной системы при работе с клавиатурой.

Прерывания и порты клавиатуры.

Видеоадаптеры.

Прерывания видеосистемы.

Организация вывода информации на экран дисплея через память видеоадаптера.

Организация вывода информации на экран дисплея через прерывания.

1.Общие сведения о пэвм.

ПЭВМ – это вычислительная система, представляющая собой совокупность аппаратных (в литературе встречается термин Hard Ware) и программных( Soft Ware) средств.

Архитектура ПЭВМ - совокупность методов, алгоритмов и аппаратных средств, предназначенных для функционирования ЭВМ.

Архитектура современной ПЭВМ может быть представлена следующей схемой:

Современные ПЭВМ, в отличие от самых первых, обзавелись большим количеством шин, к которым подключаются внешние устройства. Это связано с тем, что не все устройства могут работать на той скорости и тактовой частоте, на которой работает центральный процессор. На схеме вверху - самые быстрые устройства (процессор работает на частоте 3000 или больше мегагерц), внизу - самые медленные (устройства на шине ISA - не более 16-ти мегагерц). Для того, чтобы более медленные устройства не замедляли более быстрые, введены несколько промежуточных шин и контроллеров.

Видеосистема переместилась на собственную шину в связи с возрастающей потребностью в более сложной графике, к тому же современные ПЭВМ должны справляться с потоком видеоданных, получаемых с видеокамер и видеомагнитофонов для осуществления кодирования и обработки в реальном времени - раньше персональные ЭВМ не годились для таких целей. Шина PCI больше не может обслуживать видеоподсистему, тем более шина ISA - самая первая системная шина у ПЭВМ.

Память более не подключается к общей шине, а управляется своим контроллером, который, в свою очередь, подключен к шине процессора. Между памятью и процессором добавлена кэш-память, доступ к которой осуществляется быстрее, т.к. она относится к статической памяти . В кэш-памяти сохраняется порции памяти, использовавшиеся ранее. В случае запроса тех порций, которые уже есть в кэше, доступ к обычной Оперативной памяти на производится.

Шина USB позволяет подключать устройства без выключения питания. Все необходимые ресурсы (порты, прерывания, адреса памяти) назначаются автоматически по технологии Plug&Play.

Все внешние устройства, подключенные ко всем шинам, получают порты. Через порты можно получить доступ ко внутренним регистрам состояния устройств и выдавать команды управления. Обратную связь также организуют через аппаратные прерывания (IRQ).

MOST

- контроллер, согласующий работу двух шин, управляющий работой дисковых устройств.

ROM BIOS

Read - Only Memory Base Input-Output System - микросхема ПЗУ, хранящая программы настройки и самодиагностики ПЭВМ, а также часть системы ввода-вывода для обмена с дисковой и другими подсистемами.

SRAM

Static Random Access Memory - статическая память, не требующая циклов регенерации для предотвращения потери (в отличие от DRAM). Доступ к ней осуществляется быстрее, особенно если она находится на одном кристалле с процессором и работает на его тактовой частоте.

DRAM

Dynamic Random Access Memory - динамическая память, требующая циклов регенерации для предотвращения потери (в отличие от SRAM). Доступ к ней осуществляется за 5-7 тактов, а в случае последовательного доступа - за 2 или (в случае синхронной памяти SDRAM) за 1 такт задержки между циклами выдачи информации.

2.Архитектура 16, 32, 64 разрядных ПЭВМ.

Микропроцессор – сердце ПЭВМ. На примере эволюции процессоров рассмотрим примеры архитектур 16,32,64 разрядных ПЭВМ. Суть работы ПЭВМ в следующем: любая программа должна быть записана в память; процессор считывает из памяти очередную команду, загружает ее в специально быстродействующий регистр (регистр памяти) и декодирует. Команда содержит закодированные в двоичном виде тип выполняемой операции, адреса элементов (операндов), необходимых для выполнения команды; адрес места в памяти, куда будет помещен результат. Логически оперативную память можно представить в виде совокупности пронумерованных ячеек, доступ к каждой из которых осуществляется по ее адресу. Разрядность процессора определяет размер машинного слова, обрабатываемого компьютером одновременно. Тактовая частота характеризует производительность компьютера.

МП, как минимум, содержит:

арифметико-логическое устройство (АЛУ), предназначенное для выполнения арифметических и логических операций;

устройства управления (УУ), обеспечивающее общее управление вычислительным процессом по программе и координацию работы всех устройств ПЭВМ.

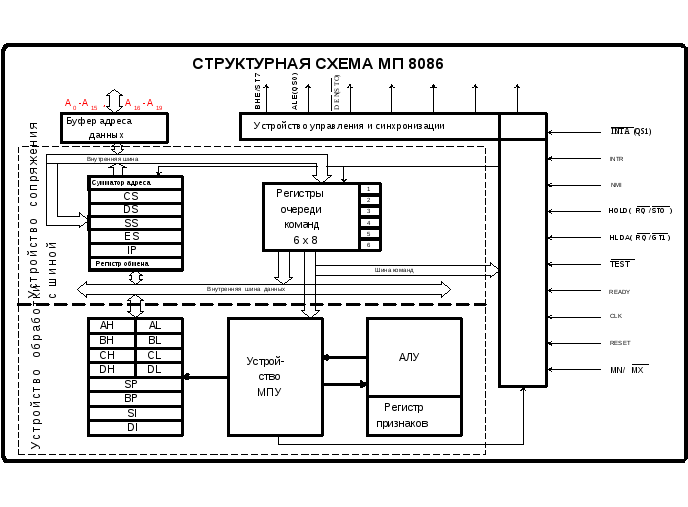

Микропроцессор 8086 фирмы Intel включает в свой состав 29 000 транзисторов и производится по МДП-технологии. По сравнению со своим предшественником ИМС 8080 МП 8086 имеет значительно более высокую производительность, число линий адреса возросло с 16 до 20, что позволило увеличить объем адресуемой памяти до 1 Мбайт вместо 64 Кбайт. Совместимость по архитектурным решениям с учетом расширения функциональных возможностей не позволила добиться полной преемственности МП 8080 и 8086. По структуре и системе команд МП 8088 идентичен МП 8086. К основным отличиям МП 8088 можно отнести уменьшенное до четырех число регистров очереди команд и 8-разрядную внешнюю шину данных. В структурной схеме МП 8086/88 (рис. ) можно выделить устройство обработки, устройство сопряжения с шиной, устройство управления и синхронизации. Устройство сопряжения с шиной состоит из шести 8-разрядных регистров очереди команд, четырех 16-разрядных сегментных регистров, 16-разрядного регистра адреса команды, регистра обмена и сумматора обмена. Регистр очереди команд заполняется новой информацией при выполнении команд условного перехода, работает по принципу «первым записан — первым считан». Такая организация позволяет хранить в нем 6 байт информации, заполняя его по 2 байта в те моменты времени, когда внутренняя шина свободна. Сумматор обмена и четыре сегментных регистра для формирования 20-разрядного адреса обеспечивают прямой доступ к памяти емкостью 1 Мбайт. При этом 16 разрядов адреса выводятся на внутреннюю шину и буфер адреса данных, а четыре — на многофункциональные выводы A16/ST3...A19/ST6, которые в другие моменты времени служат для вывода управляющей информации.

Устройство обработки состоит из 16-разрядного АЛУ, регистра признаков состояния МП, устройства микропрограммного управления (МПУ) и восьми РОН.

Программно-доступными являются РОН, сегментные регистры, адреса команд и признаков. Регистры общего назначения разделены на 4 регистра данных и 4 индексных. Старшие и младшие байты регистров данных адресуются раздельно, поэтому их можно рассматривать как восемь 8-разрядных регистров. Остальные регистры используются как 16-разрядные.

Команды МП 8086 занимают в памяти от 1 до 6 байт . В первом байте содержится код операции (в некоторых случаях он может размещаться и во втором байте). Одноразрядное поле W служит указателем разрядности (при W = 0 операнды 8-разрядные, а при W = 1 операнды 16-разрядные). Поля MOD и R/M второго байта команды определяют один из 24 режимов формирования относительного адреса операнда в сегменте данных или стека. Одно-или двухбайтовое смещение в команде определяют соответственно поля DISP8 и DISP16. При однобайтовом смещении производится знаковое расширение поля до 2 байт путем установки всех разрядов второго байта равными старшему разряду исходного байта. Поле R/M при коде MOD, равном 11, и поле REG определяют содержимое РОН, поле DATA8 или DATA16 — одно- или двухбайтовые непосредственные данные.

В систему команд 8086/88 включено 135 базовых команд. Команды передачи данных предназначены для пересылки операнда-источника на место операнда-приемника. Четырнадцать команд пересылки данных делятся на четыре группы: пересылки данных РОН, логического адреса и признаков, ввода-вывода.

Основные арифметические операции (сложение, вычитание, умножение и деление) выполняются над 8- и 16-разрядными порядковыми и целыми двоичными числами, упакованными и распакованными двоично-десятичными числами. В эту группу команд входят и команды преобразования форматов данных двоичного числа в двоично-десятичное и наоборот, а также преобразования байта в слово, слова в двойное слово.

В МП используется прямая, косвенная, регистровая, стековая, строковая и табличная адресация операндов в памяти. Адрес операнда состоит из двух 16-разрядных компонентов: базы сегмента и смещения относительно базы сегмента исполнительного адреса. База сегмента хранится в сегментном регистре. Исполнительный адрес (расстояние в байтах от начала сегмента, содержащего операнд, до операнда) интерпретируется как порядковое число от 0 до 65 536.

Микропроцессор 8086 позволяет обрабатывать 256 типов прерываний, которые делятся на аппаратные (внешние и внутренние) и программные, организованные по приоритетному принципу. По любому прерыванию управление передается программе обслуживания прерывания посредством вектора прерывания, выбираемого из таблицы, располагаемой в памяти.

Действия, выполняемые МП, можно свести к последовательности циклов шины по обмену информацией с памятью и внешними устройствами. Циклы шины подразделяются на два базовых цикла — чтения и записи. В такте Т1 на канал адреса данных всегда выдается адрес . Идентификатором начала цикла шины и занесения адреса во внешний регистр является сигнал STB. В такте Т2 переключается направление работы канала адреса данных. В тактах ТЗ и Т4 осуществляется передача данных. Между тактами Т4 текущего цикла и Т1 следующего МП может вводить дополнительные («холостые») такты.