- •Архитектура процессора

- •Машины управляемые потоком команд

- •Этапы цикла выполнения инструкций МУПК

- •Особенности МУПК

- •Машины управляемые потоком данных

- •Особенность МУПД

- •Этапы цикла выполнения инструкций МУПД

- •CISC архитектура (Complex Instruction Set Computer)

- •RISC архитектура (Reduced instruction set computer)

- •Причины перехода от CISC к RISC

- •Причины перехода от CISC к RISC

- •VLIW (very long instruction word)

- •Ключевая идея.

- •Исторические предпосылки

Архитектура процессора

•1. Набор инструкций, регистров, режимов адресации, организации виртуальной памяти, обработки исключений и прерываний. То есть все то что представляет процессор со стороны программиста

•2. То каким образом конкретный процессор реализует 1-ый пункт. То есть набор функциональных блок и их взаимодействие. (Микроархитектура).

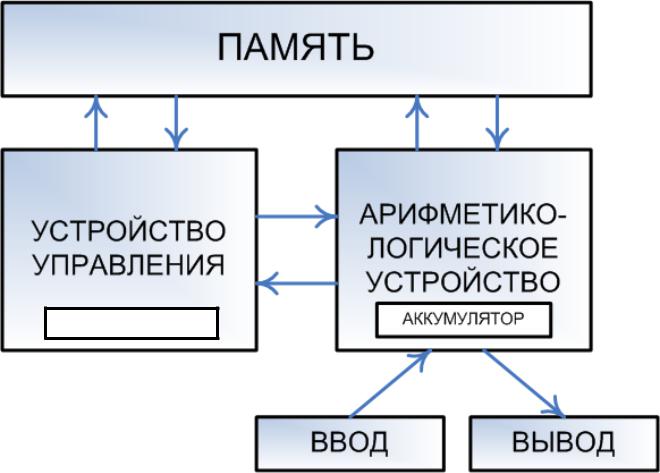

Машины управляемые потоком команд

(Архитектура фон Неймана)

СЧЕТЧИК КОМАНД

Этапы цикла выполнения инструкций МУПК

•1. Процессор выполняет чтение из памяти текущей инструкции по адресу хранящемуся в регистре счётчика команд.

•2. Декодирование инструкции и выборка ее операндов в АЛУ.

•3. Исполнение инструкции на АЛУ.

•4. Сохранение результата выполнения инструкции

•5. Изменение счетчика команд в соответствии с типом инструкции. Переход к П.1

Особенности МУПК

•1.Парадигма МУПК подразумевает последовательное исполнение инструкций.

•2.Порядок исполнение инструкций задается счетчиком команд и специальными управляющими инструкциями.

•3. Данные и инструкции хранятся в общей памяти.

Машины управляемые потоком данных

Ассоциативн ая память

Устройство |

|

|

|

|

|

|

|

|

|

…. |

|

|

|

|

АЛУ |

АЛУ |

||||

управления |

|

|||||

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Устройство

Ввода/Вывод

а

Особенность МУПД

•1. Параллельная парадигма исполнения инструкций в МУПД

•2. Отсутствует счетчик команд.

•3. Инструкции исполняются в порядке готовности их аргументов.

Этапы цикла выполнения инструкций МУПД

•1. Запрос и выборка готовых к исполнению инструкций в

ассоциативной |

памяти. |

Количество |

выбираемых |

инструкций меньше |

или равно |

числу АЛУ. |

|

•2. Исполнение инструкций на АЛУ.

•3. Сохранение результатов выполнения инструкций в память. Переход к пункту 1.

CISC архитектура (Complex Instruction Set Computer)

•Малое количество регистров.

•Большое количество режимов адресации

•Сложные инструкции

•Переменная длина инструкции

RISC архитектура (Reduced instruction set computer)

•Архитектура загрузки сохранения (load-store)

•Большое количество универсальных регистров (register-register)

•Простые инструкции

•Ограниченное число режимов адресации

•Инструкции фиксированной длинны

Причины перехода от CISC к RISC

•Конвейеризация процессора

•Увеличение объема памяти

•Совершенствование компилятора.