Лекции / Схемотехника ЭВМ. Лекция 10. Дешифраторы

.pdfГлава 2. Дешифраторы

2.1. Уравнения и структуры

Дешифратором в цифровой технике называют комбинационный узел, преобразующий n-разрядный двоичный код в однопозиционный (одноместный) код или в совокупность однопозиционных кодов. Примерами однопозиционного кода могут быть: цепь установки в нулевое состояние регистра или счётчика, адрес конкретной ячейки памяти, сигналы типа «Включить нагреватель», «Тревога» и т.п. Примером совокупности однопозиционных кодов является семисегментный алфавитноцифровой индикатор и индикаторы других типов.

Так как n-разрядный двоичный код имеет 2n наборов, то соответствующее число может быть и однопозиционных кодов. Если дешифратор выполняется в виде интегральной схемы (ИС) и имеет число выходов N = 2n, то он называется полным дешифратором, если N < 2n, то - неполным. Примером последнего является ИС дешифратора двоичнодесятичного кода (n = 4, N = 10). Для случая N = 1 дешифратор принято называть детектором состояния.

Активный сигнал в цепи однопозиционного кода может быть либо статическим потенциалом, кодирующим логические «0» и «1», либо переходами 01 и 10, поэтому различают дешифраторы с активным «0»

и активной «1» выхода.

Таблица 2.1

Обобщённая таблица истинности для дешифраторов «1 из 4-х» с активными единицей и нулём выхода

|

|

|

|

|

|

|

|

Выходы |

|

|

|

|

|

|

Номер |

Входы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

с активной «1» |

|

|

с активным «0» |

|

|||||||||

|

|

|

|

|

|

|||||||||

набора |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x1 |

x0 |

y0 |

|

y1 |

y2 |

|

y3 |

y0 |

|

y1 |

y2 |

|

y3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

|

0 |

0 |

|

0 |

0 |

|

1 |

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

|

1 |

0 |

|

0 |

1 |

|

0 |

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

1 |

0 |

0 |

|

0 |

1 |

|

0 |

1 |

|

1 |

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

1 |

1 |

0 |

|

0 |

0 |

|

1 |

1 |

|

1 |

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рассмотрим структуру полного дешифратора, преобразующего двухразрядный двоичный код в однопозиционный код (табл.2.1), где x1 и x0 - переменные дешифрируемого двухразрядного двоичного кода, y0 - однопозиционный выход дешифратора, вырабатывающий активный сигнал (0 или 1) на наборе x1x0 = 00 и неактивные сигналы на остальных наборах и т.д. Таким образом, табл.2.1 построена так, что индекс у однопозиционного выходного сигнала совпадает с номером набора входного двоичного кода.

Рассматривая выходные сигналы yi как функции алгебры логики (ФАЛ), зависящие от переменных x1 и x0, для дешифратора с активной единицей выхода из табл.2.1 получаем

y0 = x1 x0 = x1 + x0 ;

y1 = x1x0 = x1 + x0 ; |

|

y2 = x1 x0 = x1 + x0 ; |

(2.1) |

y3 = x1x0 = x1 + x0 ,

где выражения с групповой инверсией получены с использованием закона двойного отрицания и правила де-Моргана [4].

Из выражений (2.1) следует, что полный дешифратор с активной единицей выхода может рассматриваться как совокупность четырёх

двухвходовых элементов И, реализующих все конституенты единицы (элементарные произведения максимального ранга [4]), либо как совокупность четырёх двухвходовых элементов ИЛИ-НЕ, реализующих отрицание всех конституент нуля (элементарных сумм максимального ранга [4]). Для дешифратора с активным нулём выхода из табл.2.1 получаем

y0 = x1 + x0 = x1x0 ; |

|

y1 = x1 + x0 = x1x0 ; |

|

y2 = x1 + x0 = x1x0 ; |

(2.2) |

y3 = x1 + x0 = x1x0 .

Из выражений (2.2) следует, что дешифратор с активным нулём выхода можно рассматривать как совокупность четырёх двухвходовых элементов ИЛИ, реализующих все конституенты нуля, либо как совокупность четырёх двухвходовых элементов И-НЕ, реализующих отрицание всех конституент единицы.

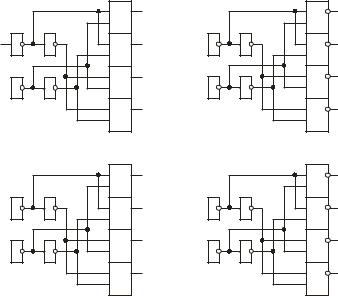

Так как в одной половине реализуемых конституент любая входная переменная встречается без инверсии, а в другой - с инверсией, то каждый вход дешифратора при такой реализации будет представлять собой 2n−1 единичных нагрузок для выходов тех элементов, с которых снимаются эти переменные. При практической реализации дешифраторов в виде ИС в них добавляются 2n буферных инверторов для обеспечения одной единичной нагрузки по входу каждой переменной. С учётом сказанного, схемы будут иметь вид, представленный на рис.2.1.

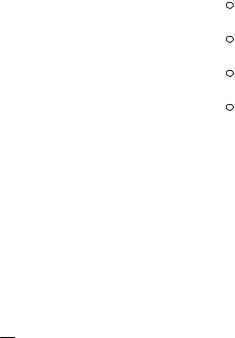

Функциональное обозначение полученных структур приведено на рис.2.2 (для дешифратора с активной единицей выхода и с активным нулём выхода), где DC - decoder - аббревиатура, принятая для обозначения дешифраторов; цифры 2 и 1 в левом узком поле обозначают двоичные веса разрядов (входных переменных) дешифрируемого двоичного кода, а кружки справа на рис.2.2,б указывают на то, что активными сигналами выхода являются уровни «0» (в положительной логике).

|

|

|

& |

x1 |

1 |

1 |

& |

x0 |

1 |

1 |

& |

|

|||

|

|

|

& |

|

|

|

а |

|

|

|

1 |

x1 |

1 |

1 |

1 |

|

|||

x0 |

1 |

1 |

1 |

|

|||

|

|

||

|

|

|

1 |

|

|

|

в |

y0 |

|

|

|

1 |

y0 |

y1 |

x1 |

1 |

1 |

1 |

y1 |

y2 |

x0 |

1 |

1 |

1 |

y2 |

|

|

|

|||

y3 |

|

|

|

1 |

y3 |

|

|

|

б |

|

|

y0 |

|

|

|

& |

y0 |

y1 |

x1 |

1 |

1 |

& |

y1 |

y2 |

x0 |

1 |

1 |

& |

y2 |

|

|

|

|||

y3 |

|

|

|

& |

y3 |

|

|

|

г |

|

|

Рис.2.1. Структуры дешифраторов «1 из 4-х»: а, б - с активной единицей выхода; в, г - с активным нулём выхода

x1 |

|

|

DC |

y0 |

|

x1 |

|

|

DC |

y0 |

|

|

|

||||||||||

2 |

|

y1 |

|

2 |

|

y1 |

|

||||

x0 |

|

|

x0 |

|

|

||||||

1 |

|

y2 |

|

1 |

|

y2 |

|

||||

|

|

|

|

|

|

|

|

||||

|

|

|

|

y3 |

|

|

|

|

|

y3 |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

аб

Рис.2.2. Функциональное обозначение дешифраторов «1 из 4-х»: а - с активной единицей выхода; б - с активным нулём выхода

Отметим, что структура дешифратора будет определяться тем, как схемотехнически выполняется вся совокупность конституент. Так, для дешифратора с активной единицей выхода при n = 4 произвольный выход может быть реализован как

y |

~ ~ ~ ~ |

||

= x x x x ; |

|||

i |

3 |

2 1 |

0 |

yi |

~ |

~ |

~ ~ |

= (x3 |

(x2 |

(x1x0 ))) ; |

|

|

~ ~ |

~ ~ |

|

yi = (x3x2 ) |

(x1x0 ) , |

||

где ~x j = xj или x j ; i = 0 ... 2n−1; j = 0 ... n – 1.

(2.3)

(2.4)

(2.5)

Дешифратор, который реализуется по выражению (2.3), называется линейным, так как его структура представляет собой линейку четырёхвходовых (в общем случае n-входовых) элементов И. Именно по этой структуре реализуются все дешифраторы, выполненные в виде ИС малой и средней степени интеграции, так как эта структура обладает минимальными задержками распространения сигналов.

Дешифратор, который реализуется по выражению (2.4), называется пирамидальным, так как его структура представляет собой n−1- ярусную «пирамиду», состоящую только из двухвходовых элементов И. На вершине пирамиды (первом ярусе) расположены четыре двухвходовых элемента И, реализующих конституенты единицы от двух младших переменных x1 и x0, на втором ярусе - восемь двухвходовых элементов И, реализующих конституенты единицы от трёх младших переменных и т.д. В основании пирамиды, т.е. на выходе дешифратора, расположены 2n двухвходовых элемента И. Эта структура никогда не выпускалась и

не выпускается в виде ИС, так как имеет очень большие задержки распространения сигналов.

Дешифратор, который реализуется по выражению (2.5), называется двухступенчатым, так как его схема представляет собой матричную структуру, состоящую из двух ступеней. Первая ступень включает в себя два n/2-входовых ((n + 1)/2 и (n − 1)/2 при нечётном n) линейных дешифратора, выходы которых образуют 2n/2 строк и 2n/2 столбцов, а вторая ступень включает в себя 2n двухвходовых элемента И, расположенных в каждом из пересечений строк и столбцов, причём на входы этих элементов подаются сигналы с соответствующих строк и столбцов. Двухступенчатые дешифраторы используются в микросхемах памяти для дешифрации адреса запоминающих ячеек, причём, как правило, вторая ступень реализуется как составная часть этих ячеек.

Используя принцип построения последней структуры, в общем случае можно реализовать многоступенчатый дешифратор.

В большинстве случаев ИС дешифраторов выполняются с активным нулём выхода, что обосновывается следующими соображениями: быстродействием (время перехода 10, как правило, меньше времени перехода 01); потребляемой мощностью (большая́ мощность потребляется при низком уровне сигнала на выходе, например ТТЛ-элементов, и поэтому целесообразно, чтобы все элементы, формирующие неактивный высокий уровень, потребляли бы меньшую мощность) и помехозащищенностью (навести помеху в низкоомную цепь, формирующую низкий уровень, крайне тяжело).

Перед разработчиком, использующим дешифраторы, возникают следующие основные вопросы: как построить дешифратор m- разрядного кода, если имеются дешифраторы n-разрядного кода, причём m > n; можно ли использовать дешифраторы не по прямому назначению, т.е. являются ли они многофункциональными узлами.

Для решения первого вопроса рассмотрим уравнения полного дешифратора с активным нулём выхода при n = 3:

y0 = |

x2 x1x0 |

, |

y4 = |

|

x2 x1x0 |

, |

|

|||||||||||

y1 = |

x2 x1x0 |

, |

y5 = |

|

x2 x1x0 |

, |

|

|||||||||||

y2 = |

|

|

, |

y6 = |

|

|

, |

(2.6) |

||||||||||

|

x2 x1x0 |

|

x2 x1x0 |

|||||||||||||||

y3 = |

|

, |

y7 = |

|

. |

|

||||||||||||

x2 x1x0 |

x2 x1x0 |

|

||||||||||||||||

В уравнениях (2.6) для y0...y3 переменная x2 встречается только с инверсией, а для y4...y7 - только без инверсии, в то время как переменные x1 и x0 образуют совпадающие комбинации в y0 и y4, y1 и y5 и т.д.

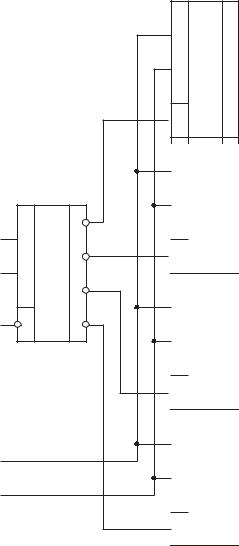

Будем рассматривать переменную x2 как стробирующий вход v (valve - клапан, вентиль) для дешифратора «1 из 4-х» (см. рис.2.1,г). Из соображений, отмеченных выше, выберем активный уровень для v равным 0. Тогда получим схему, представленную на рис.2.3,а, называемую стробируемым дешифратором, функциональное обозначение которого приведено на рис.2.3,б.

Из уравнений (2.6) видно, что для реализации дешифратора «1 из 8-ми» (дешифрирующего трёхразрядный двоичный код) необходимо взять два стробируемых дешифратора «1 из 4-х» и один внешний дополнительный инвертор. Получается схема, приведённая на рис.2.4.

Нетрудно видеть, что также легко реализуется дешифратор «1 из 16-ти» на пяти стробируемых дешифраторах «1 из 4-х» (рис.2.5), причём один из них будет дешифрировать наборы, представленные двумя старшими переменными, и стробировать остальные четыре. Вход v этого дешифратора будет являться стробирующим входом для всего дешифратора «1 из 16-ти». Приведённых примеров достаточно, чтобы разобраться в структурах многочисленных типов дешифраторов, реализуемых в виде ИС в различных сериях.

На второй вопрос можно ответить положительно, что подтверждается рассмотрением нескольких применений дешифратора в качестве многофункционального узла.

|

|

& |

y0 |

|

|

|

|

|

|

|

|

||

|

|

& |

x1 |

2 |

DC y0 |

|

x1 |

|

y1 |

||||

1 |

1 |

y1 |

|

|||

|

|

|||||

|

|

|

x0 |

1 |

y2 |

|

|

|

|

|

|

||

x0 |

1 |

& |

y2 |

V |

y3 |

|

1 |

||||||

|

||||||

|

|

& |

|

|

б |

|

|

|

y3 |

|

|

||

V |

|

1 |

|

|

||

|

|

|

|

|||

|

|

а |

|

|

|

Рис.2.3. Стробируемый дешифратор «1 из 4-х» с активным нулём выхода: а - структура; б - функциональное обозначение

|

DC |

y0 |

y0 |

|

2 |

y1 |

y1 |

|

|

||

|

|

|

|

|

1 |

y2 |

y2 |

|

|

||

|

|

|

|

x2 |

V |

y3 |

y3 |

|

|

||

x1 |

DC |

y0 |

y4 |

2 |

|

|

|

|

y1 |

y5 |

|

|

|

||

x0 |

|

|

|

1 |

|

y6 |

|

|

y2 |

||

|

|

||

|

|

|

|

|

1 |

y3 |

y7 |

|

V |

|

Рис.2.4. Схема дешифратора «1 из 8-ми» с активным нулём выхода, построенная на двух стробируемых дешифраторах «1 из 4-х»

с активным нулём выхода

x3 |

DC |

y0 |

2 |

|

|

|

y1 |

|

x2 |

|

|

1 |

|

|

|

y2 |

|

|

|

|

V |

V |

y3 |

x1 |

|

|

x0 |

|

|

DC y0

2

y1

1

y2

V y3

V y3

DC y0

2

y1

1

y2

V y3

V y3

DC y0

2

y1

1

y2

V y3

V y3

DC y0

2

y1

1

y2

V y3

V y3

y0

y1

y2

y3

y4

y5

y6

y7

y8

y9

y10

y11

y12

y13

y14

y15

Рис.2.5. Схема дешифратора «1 из 16-ти» с активным нулём выхода, построенная на пяти стробируемых дешифраторах «1 из 4-х»

с активным нулём выхода

|

2.2. Дешифратор как многофункциональный узел |

||||

|

2.2.1. Дешифратор в режиме селектора |

||||

Однобитовым селектором (демультиплексором) в цифровой |

|||||

технике называют комбинационный узел с адресной передачей данных |

|||||

с одного входа в один из многих выходов. Простейший селектор - это, |

|||||

например, |

обычный |

поворотный |

или |

клавишный |

переключатель |

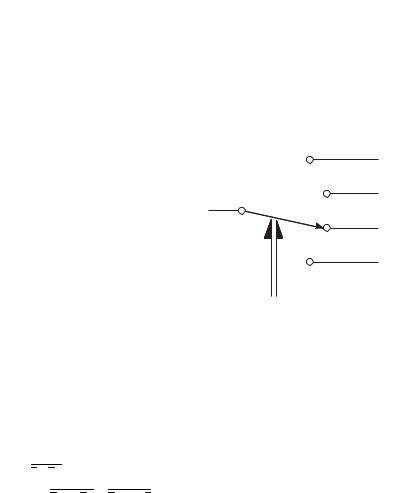

(рис.2.6). |

|

|

|

|

|

Для селектора, выпол- |

|

|

D0 |

||

няемого как логический узел, |

|

|

|||

адрес, разумеется, задается |

|

|

D1 |

||

двоичным кодом. Если ис- |

|

|

|||

пользовать стробируемый де- |

xвх |

|

|

||

шифратор «1 из 4-х» с актив- |

|

|

D2 |

||

ным |

нулём |

выхода, |

|

|

|

логическим аналогом механи- |

|

φ |

D3 |

||

ческого селектора (см. рис.2.6) |

|

||||

|

|

||||

будет схема, приведённая на |

|

|

|

||

рис.2.7, где xвх подаётся |

на |

Рис.2.6. Электромеханическая модель |

||

стробирующий вход, двухраз- |

||||

однобитного селектора «из 1 в 4» |

||||

рядный адрес а1а0 |

одного |

из |

||

φ - адрес выходного направления |

||||

четырёх выходных |

направле- |

|

||

ний подаётся на информационные входы дешифратора, а выходы дешифратора являются выходами селектора, причём индекс активного или выбранного выхода совпадает с номером набора адреса. На невыбранных выходах будут формироваться уровни 1 (в дешифраторах с активной единицей выхода - соответственно уровни 0).

Пусть необходимо передать данные xвх на выход D2, т.е. по адресу а1а0 = 10. Уравнение для выхода y2 в терминах дешифратора имеет вид

y2 = vx1 x0 . После подстановки переменных в терминах селектора име-

ем D2 = xвха1а0 = хвх 1 0 = хвх .

Если у разработчика нет стробируемого дешифратора, то можно использовать в качестве стробирующего входа любой из его информационных входов, но предпочтительнее - вход с максимальным весом. Пусть имеется нестробируемый дешифратор «1 из 8-ми» с активной единицей выхода (рис.2.8).