Лекция 13 Сумматоры. Преобразователи кода, шифратор, дешифратор

.doc

7.9. Сумматор

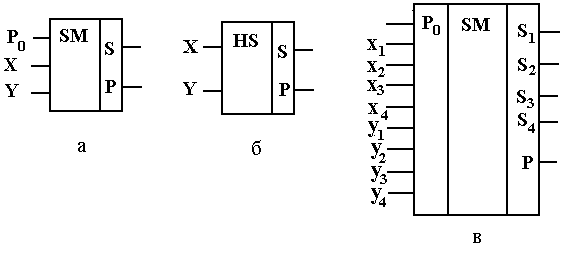

Сумматором выполняется операция арифметического сложения двух многоразрядных двоичных чисел. Эта операция проводится по разрядам, что определяет целесообразным сначала рассмотреть принцип построения одноразрядного сумматора. Как видно из рис. 7.35,а, он имеет три ввода и два вывода. На два ввода Х и Y подаются логические “1” или “0”, соответствующие определенному разряду суммируемых чисел, а третий, Р0, предназначен для подачи логической “1”, если при суммировании предыдущего разряда будет его переполнение. На выводе Р сумматора будет “1” при переполнении разряда, который суммируется. В табл. 7.16 приведены возможные состояния одноразрядного сумматора.

Рисунок 7.35. Схемное обозначение:

а - сумматора, б – полусумматора;

в - многоразрядного (четырехразрядного) сумматора

Таблица 7.16

|

X |

Y |

P0 |

S |

P |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

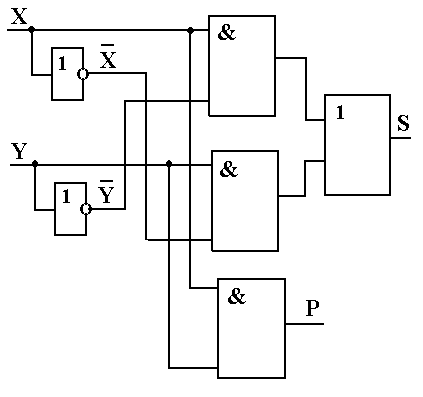

Рисунок 7.36. Схема полусумматора

В простейшем одноразрядном сумматоре, называемом полусумматором (рис. 7.35,б), отсутствует ввод Р0. Состояния полусумматора соответствуют данным табл. 7.16 при Р0 = 0. Согласно этой таблице для него функции S и Р от логических переменных Х и Y имеют вид:

S

=

X![]() +

+

![]() Y,

Р

=ХY.

(7.15)

Y,

Р

=ХY.

(7.15)

Следовательно, полусумматор может быть реализован на двух элементах “НЕ”, трех элементах “И” и одном элементе “ИЛИ”. Схема такой реализации представлена на рис. 7.36. На базе двух полусумматоров строится схема одноразрядного сумматора, как показано на рис. 7.37.

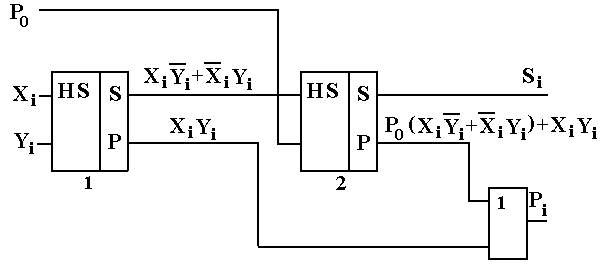

Рисунок 7.37. Схема сумматора

Действительно, согласно табл. 7.16,

Si

= XiYi

P0

+

![]() i

Yi

i

Yi

![]() 0

+

P0

Xi

Yi

+ P0

Xi

Yi;

0

+

P0

Xi

Yi

+ P0

Xi

Yi;

Pi

=

P0

(Xi![]() i

+

i

+

![]() iYi)

+ XiYi.

iYi)

+ XiYi.

Эти соотношения с использованием тождеств алгебры логики могут быть преобразованы следующим образом:

Si

= (Xi![]() i

+

i

+

![]() i

i![]() i)

i)

![]() 0

+ P0

(

0

+ P0

(![]() i

i![]() i

+

0 + ХiYi

+ 0) =

i

+

0 + ХiYi

+ 0) =

=

(Xi![]() i

+

i

+

![]() iYi)

iYi)

![]() 0

+ P0

(Хi

0

+ P0

(Хi![]() i

+

XiYi

+ Yi

i

+

XiYi

+ Yi![]() I)

=

I)

=

=

(Xi![]() i

+

i

+

![]() iYi)

iYi)

![]() 0

+ P0

(

0

+ P0

(![]() I

+ Yi) =

I

+ Yi) =

=

(Xi![]() i

+

i

+

![]() iYi)

iYi)

![]() 0

+ P0

0

+ P0![]() =

=

=

(Xi![]() i

+

i

+

![]() iYi)

iYi)

![]() 0

+ (

0

+ (![]() )

P0

)

P0

Pi

=

P0

(Xi![]() i

+

i

+

![]() iYi)

+ XiYi

(P0

+

iYi)

+ XiYi

(P0

+![]() 0)

=

0)

=

=

P0

(Xi![]() i

+

i

+

![]() iYi)

+ XiYi

∙

1 =

iYi)

+ XiYi

∙

1 =

=

P0

(Xi![]() i

+

i

+

![]() iYi)

+ XiYi.

iYi)

+ XiYi.

Из сравнения

полученных соотношений с формулами

(7.15) следует, что информация, снимаемая

с клеммы S второго

полусумматора, является результатом

суммирования информации P0

и (Xi![]() i

+

i

+

![]() iYi),

поступающих на его вход. Информация Рi

является результатом логического

сложения информации с клемм Р

первого и второго полусумматоров.

iYi),

поступающих на его вход. Информация Рi

является результатом логического

сложения информации с клемм Р

первого и второго полусумматоров.

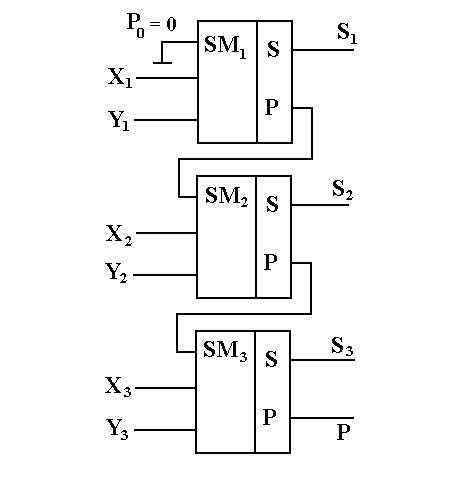

Для суммирования n-разрядных чисел используется n одноразрядных сумматоров, включенных по схеме рис. 7.38. На два входа каждого одноразрядного сумматора Xi и Yi подается информация, соответствующая определенному i-му разряду суммируемых чисел. На третий вход Р0 каждого такого сумматора, кроме первого, передается информация переноса с предыдущего сумматора (“1” в случае переполнения при суммировании в этом сумматоре). Ввод Р0 первого сумматора заземлен. Схемное обозначение многоразрядного сумматора приведено на рис. 7.35,в.

Рисунок 7.38. Схема трехразрядного сумматора

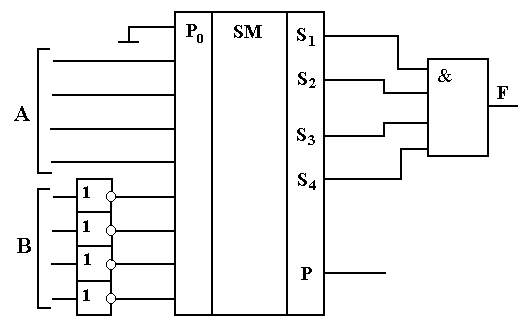

Многоразрядный сумматор можно использовать в качестве основы построения схем сравнения двоичных n-разрядных чисел, т.е. числового компаратора. Такая схема сравнения четырехразрядных чисел А и В приведена на рис. 7.39. Одно из этих чисел, например В, вводится в сумматор через логические элементы “НЕ”. Информация с вывода S сумматора подается на четырехвходовый логический элемент “И”. Таким образом, схема сравнения имеет два выхода: F – вывод элемента “И” и Р – вывод сумматора, фиксирующего переполнение последнего разряда при суммировании. При равенстве чисел А и В одинаковыми будут и числа в каждом их разряде, т.е. Аi = Вi. В соответствии с тождеством (7.2) алгебры логики (раздел 7.1) на всех выводах Si сумматора будут логические “1” и не будет переполнение всех разрядов при суммировании, т.е. Р = 0. Следовательно, на выходе схемы сравнения F = 1 и Р = 0. Если А ≠ В, то хотя бы в одном из разрядов этих чисел Аi ≠ Вi. Тогда при суммировании чисел таких разрядов с применением элемента “НЕ”, в схеме рис. 7.39, на выводах сумматора, соответствующих этим разрядам, будут логические “0”, что обусловливает появление “0” и на выходе логического элемента “И”.

Рисунок 7.39. Цифровая схема сравнения двух четырехразрядных чисел

7.8. Преобразователи кода.

Дешифратор. Шифратор

Преобразователями кода называются комбинационные логические устройства, обеспечивающие преобразование m-разрядной числовой информации в n-разрядную. Такими устройствами являются дешифратор и шифратор.

Дешифратором (декодером) называется устройство с m вводами и n ≤ 2m выводами, “опознающее” информацию, представленную в виде двоичного m–разрядного числа, и выдающее результат “опознания” как набор логических “1” и ”0” на каждом из своих выводов. В частности, дешифраторы используются для преобразования двоичных чисел в десятичные. Возможные состояния такого устройства, распознающего трехразрядное число, сведены в табл. 7.13. Каждому числу соответствует логическая “1” на одном из выводов, когда на остальных выводах будут “0”.

Таблица 7.13

|

Число |

Вводы |

Выводы |

|||||||||

|

X3 |

X2 |

X1 |

F0 |

F1 |

F2 |

F3 |

F4 |

F5 |

F6 |

F7 |

|

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

2 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

3 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

4 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

5 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

6 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

7 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

Принцип построения схемы такого дешифратора можно понять, если представить логические функции Fi для каждой комбинации входных переменных Xj как:

F0

=

![]()

![]()

![]() ,

,

F1

=

![]()

![]() Х1,

Х1,

F2

=

![]() Х2

Х2

![]() ,

,

………………

F7 = Х3 Х2 Х1,

где

Xj

соответствует логической «1», а

![]() - логическому «0» j-го

разряда входной информации. Как следует

из анализа этих функций, дешифратор

может быть реализован с использованием

трех логических элементов “НЕ” и восьми

трехвходовых элементов “И”. К каждому

элементу “И” подводятся все три входных

информации, которые первоначально либо

проходят через соответствующий элемент

«НЕ», либо проходят в обход его, как

показано на схеме рис. 7.31.

- логическому «0» j-го

разряда входной информации. Как следует

из анализа этих функций, дешифратор

может быть реализован с использованием

трех логических элементов “НЕ” и восьми

трехвходовых элементов “И”. К каждому

элементу “И” подводятся все три входных

информации, которые первоначально либо

проходят через соответствующий элемент

«НЕ», либо проходят в обход его, как

показано на схеме рис. 7.31.

Рисунок 7.31. Схема дешифратора, распознающего

трехразрядные числа

Шифратор (кодер) – устройство, выполняющее совокупность логических операций, обратных операциям дешифратора (декодера). Шифратор имеет n выводов и m ≤ 2n вводов. Он преобразует набор “1” и ”0”, поступающих на его входы, в n-разрядное число. Примером шифратора является преобразователь десятичного числа в двоичное, возможные состояния которого отражены в табл. 7.14.

Таблица 7.14

|

Чис-ло |

Вводы |

Выводы |

||||||||||||

|

X0 |

X1 |

X2 |

X3 |

X4 |

X5 |

X6 |

X7 |

X8 |

X9 |

F4 |

F3 |

F2 |

F1 |

|

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

2 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

3 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

|

4 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

5 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

|

6 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

7 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

|

8 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

|

9 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

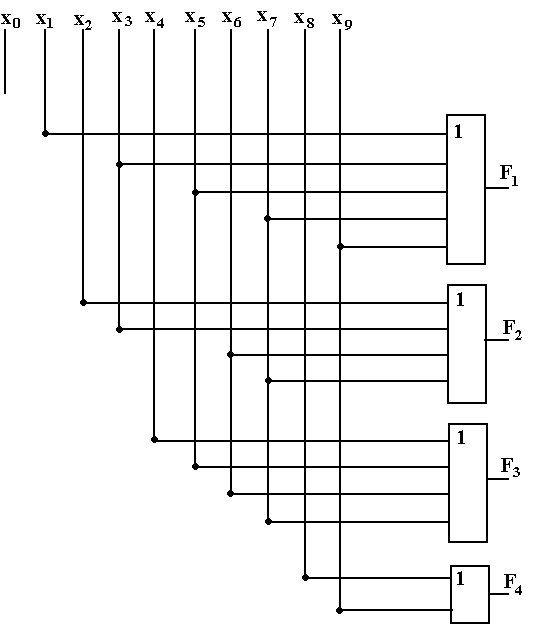

Рис.5.27. Схема шифратора, преобразующего

десятичное число в двоичное

Из таблицы следует, что на выходе F1 будет логическая «1», если логическая «1» будет или на Х1, или на Х3, или на Х5, или на Х7, или на Х9, т.е.

F1 = Х1 + Х3 + Х5 + Х7 + Х9.

Аналогичным образом могут быть записаны логические функции или для других выводов шифратора.

F2 = Х2 + Х3 + Х6 + Х7,

F3 = Х4 + Х5 + Х6 + Х7,

F4 = Х8 + Х9.

Следовательно, шифратор должен содержать четыре логических элемента «И», один из которых пятивходовой, два – четырехвходовые и один – двухвходовой. Вход Х0 не связан ни с одним из этих элементов. Схема такого шифратора приведена на рис. 7.32.

Схемное обозначение дешифратора и шифратора представлено на рис. 7.33.

Рисунок 7.33. Схемное обозначение дешифратора (а)

и шифратора (б)

Таблица 7.15

|

Цифра на индикаторе |

Ввод |

Вывод |

|||||||||

|

8 |

4 |

2 |

1 |

а |

b |

c |

d |

e |

f |

g |

|

|

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

|

2 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

|

3 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

|

4 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

5 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

|

6 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

|

7 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

|

8 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

9 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |