- •1. Классификация современных измерительных устройств.

- •3.Формы представления измерительной информации

- •4. Основные компоненты компьютерных измерительных приборов.

- •5. Структурная схема систем сбора измерительной информации.

- •6. Вопросы согласования измерительных сигналов.

- •7. Комбинированные и последовательные логические измерительные элементы.

- •8. Дискретизация и квантование измеряемых сигналов.

- •9. Типы и структуры ацп.

- •10.Сигма-дельта ацп.

- •11. Цифро-аналоговые преобразователи.

- •12.Типы и структуры линий ввода/вывода современных компьютерных приборов.

- •13.Микроконтроллеры, архитектура, критерий выбора.

- •14. Интегрированные среды разработки для программирования микроконтроллеров.

- •15. Обобщенная процедура подключения ацп к Микроконтроллеру.

- •16. Методы обмена данными между ацп и Микроконтроллером.

- •17. Способы генерации тактовых сигналов.

- •19. Последовательная передача данных usart, uart

- •20. Передача данных по интерфейсу i2c.

- •21. Передача данных по интерфейсу spi.

- •22. Форматы шестнадцатеричных файлов.

- •23. Программируемые системы на кристалле pSoC.

- •24. Плисы. Архитектура, применение, программирования.

- •25. Сетевая модель передачи информации (osi).

- •26. Модули Xport и Wiport.

- •27. Пакеты для проектирования электронных устройств Eagle и Proteus.

- •28. Использование платформы Eclipse для создания программного обеспечения встроенных систем.

- •29-30. Средства ввода и вывода.

- •Резистивные сенсорные экраны. Четырёхпроводной экран.

- •Пятипроводной экран

- •Матричные сенсорные экраны.

7. Комбинированные и последовательные логические измерительные элементы.

Логические элементы - устройства, предназначенные для обработки информации в цифровой форме (последовательности сигналов высокого - "1" и низкого - "0" уровней). Это позволяет значительно сократить количество операций и элементов, выполняющих эту обработку.

Логические элементы делятся на комбинационные (порт: транзистор + элемент) и последовательные. Последние отличаются наличием памяти (ПЗУ).

Триггеры и регистры являются простейшими представителями цифровых микросхем, имеющих внутреннюю память. Выходные сигналы микросхем с внутренней памятью зависят от того, какие входные сигналы и в какой последовательности поступали на них в прошлом, то есть они помнят предысторию поведения схемы. Триггеры и регистры сохраняют свою память только до тех пор, пока на них подается напряжение питания.

Большим преимуществом триггеров и регистров перед другими типами микросхем с памятью является их максимально высокое быстродействие (то есть минимальные времена задержек срабатывания и максимально высокая допустимая рабочая частота). Однако недостаток триггеров и регистров в том, что объем их внутренней памяти очень мал, они могут хранить только отдельные сигналы, биты (триггеры) или отдельные коды, байты, слова (регистры).

В основе любого триггера (англ. — "тrigger" или "flip-flop") лежит схема из двух логических элементов, которые охвачены положительными обратными связями (то есть сигналы с выходов подаются на входы). В результате подобного включения схема может находиться в одном из двух устойчивых состояний, причем находиться сколь угодно долго, пока на нее подано напряжение питания.

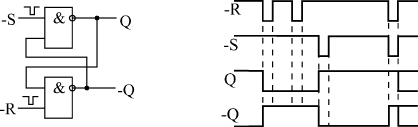

Пример так называемой триггерной ячейки на двух двухвходовых элементах И-НЕ приведен на рис ниже.

У схемы есть два инверсных входа: -R — сброс (Reset), и -S — установка (Set), а также два выхода: прямой выход Q и инверсный выход –Q.

Для правильной работы схемы отрицательные импульсы должны поступать на ее входы не одновременно. Приход импульса на вход -R переводит выход -Q в состояние единицы, а так как сигнал -S при этом единичный, выход Q становится нулевым. Этот же сигнал Q поступает по цепи обратной связи на вход нижнего элемента. Поэтому даже после окончания импульса на входе -R состояние схемы не изменяется (на Q остается нуль, на -Q остается единица). Точно так же при приходе импульса на вход -S выход Q в единицу, а выход -Q — в нуль. Оба эти устойчивых состояния триггерной ячейки могут сохраняться сколь угодно долго, пока не придет очередной входной импульс, — иными словами, схема обладает памятью.

Существуют J-,K-, JK- триггеры, RS- триггеры. В счетчиках используются К- триггеры. В линиях, интерфейсах, портах для передачи используют Latch- триггеры

1) RS-триггер

S-set, R- reset

Здесь на входе не может быть два одинаковых уровня 0 и 0 или 1 и 1, ввели: 0 и 1: set и reset

|

S |

R |

Q |

|

|

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

На выходе не может быть 2 одинаковых уровня.

RS-триггер (обозначается ТР) — самый простой триггер, но редко используемый.

2) D-триггер

D-триггер (обозначается ТМ) — наиболее распространенный тип триггера. Помимо общих для всех триггеров входов установки и сброса S и R, он имеет один информационный вход D (вход данных) и один тактовый вход.

3) J,K – тип (для счетчиков):

![]()

JK-триггер (обозначается ТВ) значительно сложнее по своей структуре, чем RS-триггер. Он относится к так называемым тактируемым триггерам, то есть он срабатывает по фронту тактового сигнала.

1)Элемент “НЕ”, реализующий функцию логического отрицания.

![]()

![]()

2) Элемент “И” (AND) реализует функцию логического умножения.

![]()

![]()

3) Элемент “ИЛИ” (OR) реализует функцию логического сложения.

![]()

4) Элемент “И-НЕ” (отрицательный “И”, NAND)

![]()

![]()

5)Элемент “ИЛИ-НЕ” (отрицательный “ИЛИ”,NOR)

![]()

![]()

6) Элемент “Исключающее ИЛИ”. Сумматор (XNOR): Y=X1+X2

![]()

![]()