DgCXT_Lab_7

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра ЭПУ

отчет

по лабораторной работе №7

по дисциплине «Цифровая схемотехника»

Тема: «ИССЛЕДОВАНИЕ СХЕМ ЦАП И АЦП»

Студент гр. 7201 |

|

Семирякова А.А. |

Преподаватель |

|

Аристов С.А |

Санкт-Петербург

2021

Основные теоретические положения

Одним из самых распространенных способов преобразования цифрового сигнала (многоразрядного слова) в напряжение является использование резисторной матрицы R-2R.

Существует и более простой для анализа метод – использование резисторов веса. Фактически, этот метод сводится к тому, что при помощи набора резисторов удваивающегося от одного к другому сопротивления делитель напряжения, управляемый битами преобразуемого слова. Самый низкоомный резистор управляется старшим битом, самый высокоомный – младшим. Однако, этот простой метод не получил распространения из-за крайнего неудобства в подборе сопротивлений.

ЦАП с матрицей R-2R лишен этого недостатка: матрица содержит резисторы лишь двух сопротивлений. Рассмотрим принцип ее действия.

Рис.1. Резисторная матрица R-2R

На Рис. 1 показана схема 4-разрядной резисторной матрицы, управляемой словом B[3..0]. Номиналы резисторов 2R0–3 равно 2R и вдвое больше номиналов резисторов R0–3.

Положим, что напряжения логических уровней сигналов B3–B0 равны, соответственно, 0 / UП вольт, и проанализируем работу схемы.

Рассмотрим фрагмент схемы, включающий в себя только вход B0, игнорируя существование прочих элементов схемы. Она формирует свое выходное напряжение U0 под управлением младшего бита. Если B0 = 1, то выходное U0 по формуле делителя напряжения составит UП/2, иначе – ноль. Выходное сопротивление этой схемы равно сопротивлению, получаемому параллельным включением двух резисторов номиналом 2R, т.е. оно равно R.

Фрагмент схемы, включающий в себя бит B1, содержит в себе предыдущий фрагмент схемы (с битом B0). Представим, что B0 = 0, тогда два резистора 2R0 включены параллельно с получением сопротивления номиналом R. Этот составной резистор включается последовательно сопротивлению R1 таким же номиналом, т.е. узел цепи, где действует напряжение U1, соединен с землей сопротивлением номиналом 2R. Мы опять получили симметричный делитель напряжения, и если B0 = 0, B1 = 1, то U1 = UП / 2. Выходное сопротивление фрагмента схемы, включающего в себя бит B1, опять равняется величине R и рассчитывается, как ((2R0 || 2R0) + R1) || 2R1, где «||» – символ для обозначения параллельного включения сопротивлений.

Эти рассуждения можно повторить и для фрагмента схемы, содержащего бит B3. Если биты B0 и B1 равны нулю, для третьего фрагмента схемы опять выполняется формула делителя напряжения, верхнее плечо которого представляет сбой резистор 2R2, а нижнее плечо – источник нулевого напряжения с выходным сопротивлением ((2R0 || 2R0) + R1) || 2R1 + R2 = 2R. Опять если B0 = B1 = 0, а B2 = 1, выходное напряжение фрагмента схемы (U2) составит UП / 2.

Из этого анализа можно сделать ряд важный выводов. Во-первых, разрядность схемы можно увеличивать, теоретически, до бесконечности. Во-вторых, влияние n-го бита в выходное напряжение всей схемы равно влиянию всех ее младших битов. Иными словами, для 4-разрядной резисторной матрицы справедливо соотношение: 𝑈ВЫХ=𝑈П(𝐵312+𝐵214+𝐵118+𝐵0116)

Максимальное выходное напряжение схемы никогда не будет в точности равно напряжению питания из-за наличия в схеме резистора 2R0, соединяющего узел U0 с землей, однако, по мере роста числа разрядов, оно будет асимптотически стремиться к напряжению питания. В более общем виде выражение, связывающее выходное напряжения матрицы со значением управляющий битов, имеет следующий вид: 𝑈ВЫХ=𝑈ПΣ𝐵𝑛−𝑖12𝑖+1𝑛−1𝑖=0

То есть, скажем, для 8-разрядной матрицы выходное напряжение складывается из напряжений битов с весами, от старшего к младшему, 1/2, 1/4, …1/256, а шаг изменения напряжения на выходе схемы равен весу младшего бита, умноженному на напряжение питания (т.е.UП / 256). Резисторная матрица работает как цифроаналоговый преобразователь, выходное напряжение которого изменяется ступенчато и пропорционально управляющему числу.

Для 4-разрядной матрицы зависимость выходного напряжения от управляющего числа показана на Рис. 2

Рис.2. Характеристика преобразования для 4-разрядной резисторной матрицы R-2R

Построим схему АЦП последовательного приближения и проанализируем его работу:

Рис. 1 Схема АЦП последовательного приближения

Возьмем Uвх=2,115В (номер зачетки 720115)

Рис. 2 Результат анализа работы АЦП последовательного приближения

Рассчитаем теоретические значения

и

числа, полученного на выходе АЦП:

и

числа, полученного на выходе АЦП:

Сделаем работу над ошибками, для этого модернизируем схему и проверим ее работу:

Рис. 3 Исправленная схема АЦП последовательного приближения

Рис. 4 Схема двоичного синхронного 8-разрядного счетчика

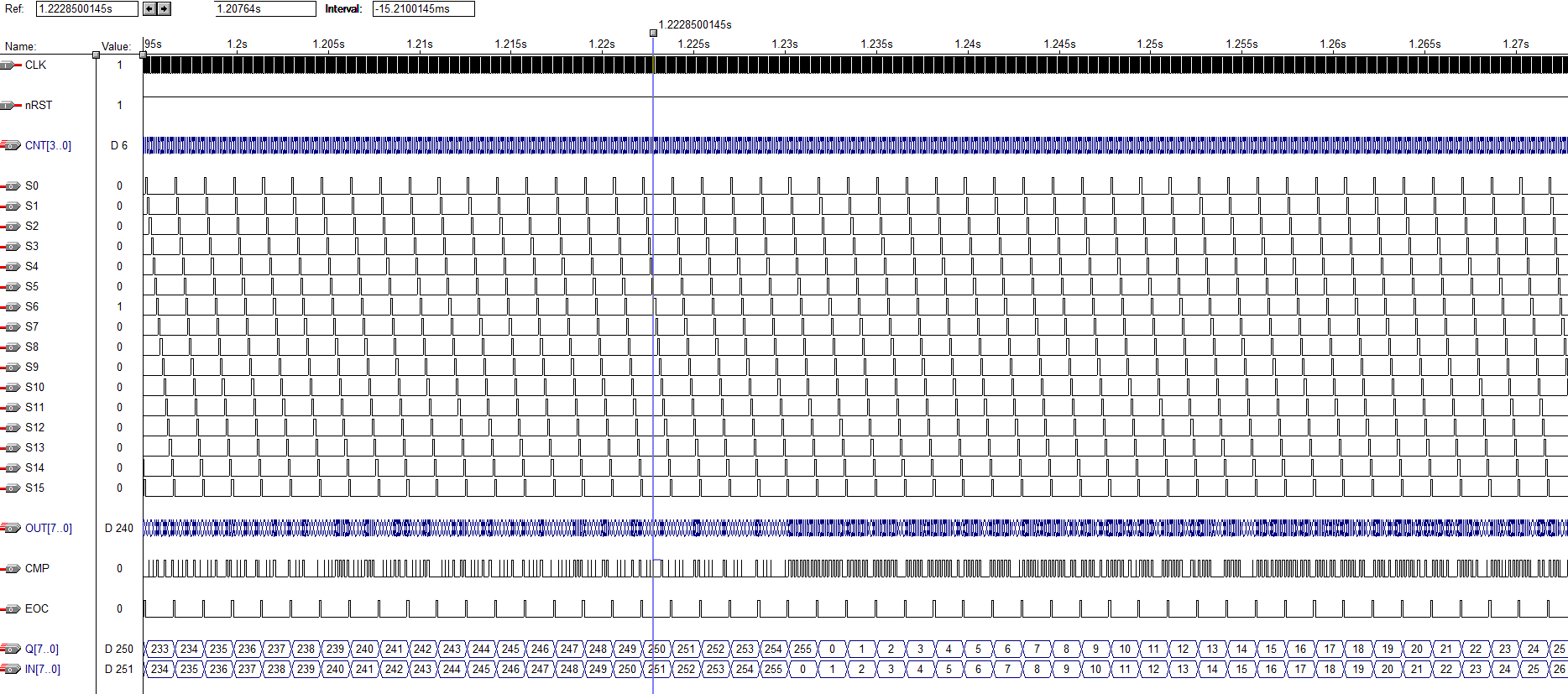

Рис. 5 Тактовая диаграмма

Выводы: в данной лабораторной работе была построена схема АЦП последовательного приближения и проанализирована его работа. В схеме используется компаратор, сигнал с которого вместе с сигналом, приходящим после счетчика с дешифратором, попадает на JK-триггеры, которые сравнивают и получившиеся напряжение. Значения, получившиеся после триггеров, хранятся в 8-битном регистре. Также был получены теоретические значения и числа, полученного на выходе АЦП. Полученные значения приближены к экспериментальным значениям.