Элементы и узлы ЭВМ. Ч. 2 (120

.pdfМосковский государственный технический университет

имени Н.Э. Баумана

В.И. Виноградов, С.Б. Спиридонов, А.В. Шигин

ЭЛЕМЕНТЫ И УЗЛЫ ЭВМ

Методические указания к лабораторному практикуму по курсу

«Элементы и узлы ЭВМ»

Часть 2

М о с к в а Издательство МГТУ им. Н.Э. Баумана

2011

УДК 621.3.038 ББК 32.973

В49

Рецензент М.В. Мурашов

Виноградов В.И.

В49 Элементы и узлы ЭВМ : метод. указания к лабораторному практикуму по курсу «Элементы и узлы ЭВМ». — Ч. 2 / В.И. Виноградов, С.Б. Спиридонов, А.В. Шигин. — М. : Из= д=во МГТУ им. Н.Э. Баумана, 2011. — 20 с. : ил.

Приведено задание для выполнения лабораторной работы по курсу «Элементы и узлы ЭВМ». Даны краткие пояснения по применению про= граммного комплекса Electronics Workbench.

Для студентов 2=го курса специальности «Системы обработки ин= формации и управления» факультета «Информатика и системы управ= ления».

УДК 621.3.038 ББК 32.973

© МГТУ им. Н.Э. Баумана, 2011

2

Работа № 3. ИССЛЕДОВАНИЕ РАБОТЫ СЧЕТЧИКОВ

Цель работы — изучение принципов построения счетчиков и пе= ресчетных схем, выполненных на динамических счетных триггерах.

Продолжительность работ : 1=я часть (на макете УМ=11) — 4 ч, 2=я часть (на ЭВМ) — 4 ч.

Теоретическая часть

Одной из наиболее распространенных операций, выполняемых в вычислительных устройствах цифровой обработки информации, является подсчет числа сигналов импульсного или потенциального вида.

Узел вычислительных устройств, предназначенный для подсче= та числа входных сигналов, называется счетчиком. Счетчики широ= ко применяются почти во всех цифровых устройствах автоматики и вычислительной техники. В цифровых вычислительных машинах счетчики используются для подсчета шагов программы, циклов сло= жения и вычитания при выполнении арифметических операций, пре= образования кодов. Их также используют в делителях частоты, рас= пределителях сигналов и т. п.

По системе счисления счетчики подразделяют на двоичные, дво= ично=десятичные, десятичные, счетчики с основанием системы счис= ления, не равным 2 и 10 (пересчетные схемы).

По реализуемой операции счетчики подразделяют на суммирую= щие, вычитающие и реверсивные.

К основным параметрам счетчиков относятся:

– модуль счета, или коэффициент пересчета счетчика Ксч, ха= рактеризующий число устойчивых состояний, в которых может на= ходиться n=разрядный счетчик, т. е. предельное число входных сиг= налов, которое может быть подсчитано счетчиком.

Двоичный n=разрядный счетчик имеет 2n различных состояний. Число разрядов двоичного счетчика можно определить по выражению

3

n ≥ log2 Kсч, |

(1) |

где n — число разрядов, определяемое ближайшим целым числом, удов= летворяющим данному неравенству; Ксч — коэффициент пересчета;

– максимальная частота поступления входных сигналов fсч max – частота, при которой счетчик еще сохраняет работоспособность; эта частота определяется, как правило, максимально допустимой часто= той переключения триггера младшего разряда счетчика.

Синтез асинхронных счетчиков и пересчетных схем на универсальных D и JK триггерах

Простейшим счетчиком является триггер со счетным входом, ре= гистрирующий сигналы по модулю 2, т. е. осуществляющий подсчет и хранение результата подсчета не более двух сигналов. Соединив несколько счетных триггеров определенным образом, можно полу= чить схему многоразрядного счетчика.

В настоящее время в состав большинства современных серий ло= гических микросхем (133, К133, 155, К155 и др.) входят широко используемые D= и JK=триггеры.

При использовании D=триггера в качестве счетного триггера его инверсный выход соединяют с его входом D. Работать в счетном режиме могут триггеры только динамического типа.

Представление счетчика цепочкой счетных триггеров возможно как для суммирующего, так и для вычитающего вариантов, посколь= ку закономерность по соотношению частот переключения разрядов сохраняется при просмотре таблицы как сверху, так и снизу. Разли= чия при этом состоят в направлении переключения предыдущего разряда, вызывающего переключение следующего.

При прямом счете (суммирование) следующий разряд переклю= чается при переходе предыдущего в направлении из 1 в 0, а при об= ратном счете – при переключении из 0 в 1.

Асинхронный суммирующий счетчик на D#триггерах можно по= лучить, соединив инверсный выход предыдущего триггера Q со вхо= дом С последующего триггера.

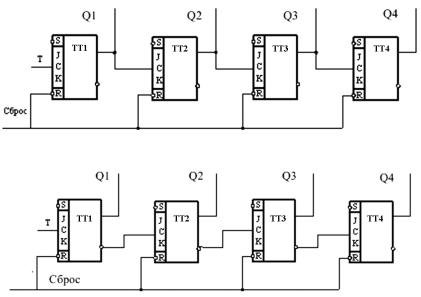

Схема асинхронного четырехразрядного суммирующего счетчи= ка на D#триггерах приведена на рис. 1.

Для построения вычитающего счетчика на D=триггерах прямой выход предыдущего триггера соединяют со входом С последующего триггера.

4

Рис. 1. Схема асинхронного суммирующего счетчика на D=триггерах

Схема асинхронного четырехразрядного вычитающего счетчика на D=триггерах приведена на рис. 2.

Рис. 2. Схема асинхронного вычитающего счетчика на D=триггерах

Для построения асинхронного суммирующего счетчика на JK= триггерах необходимо соединить прямые выходы предыдущих триг= геров со входом С последующих триггеров.

JK=триггер должен находиться в счетном режиме, при котором входные сигналы J = K = 1.

Все выводы триггеров на макете УМ=11 имеют потенциал логи= ческой единицы, поэтому в счетчике достаточно организовать толь= ко межразрядные связи.

Схема асинхронного четырехразрядного суммирующего счетчи= ка на JK=триггерах приведена на рис. 3.

Асинхронный вычитающий счетчик на JK=триггерах можно по= лучить, соединив инверсный выход предыдущего триггера со вхо= дом С последующего триггера (рис. 4).

Следует отметить, что в изображениях JK=триггеров на рис. 3 и 4 не показаны единичные потенциалы, которые необходимо подавать на входы J и K каждого триггера, чтобы данный триггер работал

5

Рис. 3. Схема асинхронного суммирующего счетчика на JK=триггерах

Рис. 4. Схема асинхронного вычитающего счетчика на JK=триггерах

в счетном режиме. Данные изображения соответствуют триггеру ма= кета УМ=11, в котором все незадействованные входы всех схем име= ют потенциал логической единицы.

Реверсивные счетчики осуществляют подсчет сигналов как в пря= мом, так и в обратном направлении, т. е. они могут работать в режи= ме сложения и в режиме вычитания сигналов.

Для построения реверсивных счетчиков необходимо предусмот= реть схемы, пропускающие сигналы на вход следующих триггеров либо с инверсионного (при суммировании), либо с прямого (при вычитании) выходов предыдущего триггера.

Схема асинхронного последовательного реверсивного счетчика на JK=триггерах со схемой управления прямым и обратным счетом на JK=триггере представлена на рис. 5.

Рассмотренные выше счетчики имели коэффициент пересчета 2n. Однако на практике возникает необходимость в счетчиках, коэф= фициент пересчета которых отличен от 2n. Очень часто, например, применяют счетчики с Ксч = 3; 10 и т. д., т. е. счетчики, имеющие число устойчивых состояний соответственно 3, 10 и т. д. Принцип построения таких счетчиков заключается в исключении «лишних» ус=

6

Рис. 5. Схема асинхронного реверсивного счетчика на JK=триггерах

тойчивых состояний счетчика с Ксч = 2n, т. е. в организации схем, зап= рещающих некоторые состояния.

Число запрещенных состояний для любого счетчика можно оп= ределить по следующему выражению:

m = 2n – Ксч, |

(2) |

где m — число запрещенных состояний; 2n — число устойчивых состо= яний двоичного счетчика; Ксч — требуемый коэффициент пересчета.

Например, для счетчика с Ксч = 3, который строится на двух счет= ных триггерах, и для счетчика с Ксч = 10, который строится на четы= рех счетных триггерах, число избыточных состояний согласно фор= муле (2) равно 1 и 6 соответственно.

Рассмотрим способ построения счетчика с естественным поряд= ком счета, для которого уменьшение числа устойчивых состояний достигается за счет сбрасывания показаний счетчика в нулевое со= стояние при записи в него заданного числа сигналов.

В соответствии с этим способом к счетчику добавляется логичес= кая схема, проверяющая условие: «Код на счетчике изображает чис= ло, равное Ксч, и в зависимости от результата проверки направляет входной сигнал либо на шину «установка 0», либо на суммирование к записанному коду».

Это условие можно проверить с помощью n=входовой схемы И, связанной с прямыми выходами тех триггеров, которые при записи в счетчике коэффициента Ксч должны находиться в состоянии «1», и с инверсными выходами триггеров, которые в этом случае должны находиться в состоянии «0».

Практически число входов элемента «И» можно сократить, свя= зав его с прямыми выходами, так как сочетание единиц в записи

7

кода коэффициента Ксч может повториться только в недозволенных кодах, бóльших Ксч.

Рассмотрим синтез схемы подобного счетчика на примере Ксч = 10, т. е. счетчик должен иметь 10 состояний — от 0 до 9 в десятичной системе и от 0000 до 1001 в двоичной системе. Сначала определим разрядность счетчика:

n ≥ log2 Kсч = log210 3,35. |

(3) |

Рис. 6. Суммирующий счетчик с Ксч = 10 на D=триггерах

Рис. 7. Суммирующий счетчик с Ксч = 10 на JK=триггерах

8

Полученное значение n округлим до ближайшего целого числа, т. е. n = 4. Затем определим, какие разряды счетчика будут находиться в единичном состоянии при записи в счетчик коэффициента Ксч:

— —

Ксч = 1010 = Q4Q3Q2Q1.

Прямые выходы этих разрядов заводятся на входы логической схемы И и далее в цепь установки «0». Таким образом, при достиже= нии счетчиком значения Ксч он автоматически возвращается в состо= яние 0000 и счет начинается сначала.

Схемы суммирующих счетчиков с Ксч = 10, построенных на D=триггерах и JК"триггерах, приведены на рис. 6 и 7.

Синтез синхронных счетчиков на основе JК триггера

Особенностью синхронного счетчика является то, что счетный сигнал подается по шине одновременно на синхровходы триггеров всех разрядов. Логика переключения счетчика управляется перево= дом триггера данного разряда в счетное состояние (логические еди= ницы на входах J и K), либо в иное состояние, когда изменение со= стояния триггера не меняется при наличии счетного сигнала.

Во многих схемах JK=триггер реализуется с наличием несколь= ких входов J и входов K, объединенных конъюнкторами (логичес= кий элемент И).

JK=триггеры, входящие в состав макета УМ=11, имеют по три входа J и по три входа K, под символами J и К изображен знак &,по= ясняющий, что входные сигналы подаются на внутренние встроен= ные конъюнкторы. В макете УМ=11 все незадействованные входы имеют потенциал логической единицы, поэтому некоторые из неза= действованных входов будут работать правильно, отражая логику логического элемента И.

Проанализировав последовательность двоичных состояний счет= чика, можно сделать вывод о том, что i=й разряд счетчика должен поменять свое состояние при приходе очередного счетного импуль= са только тогда, когда все более младшие разряды находятся в состо= янии логических единиц.

Самый младший разряд счетчика должен менять свое состояние при каждом счетном импульсе. Счетное состояние первого разряда обеспечивают логические единицы на всех трех входах J и K.

9

Схема трехразрядного синхронного суммирующего счетчика по= казана на рис. 8.

Рис. 8. Синхронный суммирующий счетчик на JK=триггерах

Исследование работы счетчиков на макете УМ#11

Задание на выполнение работы

А. Изучение описания лабораторной работы и проверка лабора# торного макета

А1. Внимательно прочитать теоретическую часть описания ла= бораторной работы.

А2. Включить электропитание лабораторного макета. Должна за= гореться зеленая лампочка около тумблера «Вкл».

А3. Проверить набор прилагаемых соединительных шнуров на обрыв, подключая каждый шнур одним концом к тумблеру, а дру= гим — к индикаторной лампочке.

Б. Исследование работы счетчиков на D триггерах

Б1. В соответствии с заданным преподавателем вариантом (табл. 1) собрать одну из схем счетчиков на D=триггерах, соединяя триггеры с помощью соединительных шнуров в соответствии со схе= мами на рис. 1, 2.

Б2. Шину установки нуля (У«О») подключить к одному из тум= блеров тумблерного регистра (верхнее гнездо) для снятия потенциа= ла, необходимого для установки счетчика в нулевое состояние. Вер= хнее положение тумблера — счетный режим, нижнее — установка нуля.

Б3. Прямые выходы триггеров подключить к индикаторным лам= почкам.

10