МИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра вычислительной техники

отчет

по дисциплине «Конструкторско-технологическое обеспечение

средств вычислительной техники»

Тема: Проектирование фрагмента БИС КМОП КНС

Студенты гр. 8308 |

|

Беляева А. А. |

|

|

Довженко А. Е. |

|

|

Лукашов Н. С. |

|

|

Смирнова В. С. |

Преподаватель |

|

Зуев И. С. |

Санкт-Петербург

2021

Техническое задание:

Таблица 1. Техническое задание

№ вар. |

Фраг- мент |

№ схем |

Внешние условия включения |

Целевая функция минимизации |

S0, мкм |

|||||||

на входе |

на выходе |

|||||||||||

t = 0 |

t = -∞ |

ЭМ |

ОФ |

Сf |

||||||||

16 |

И |

11; 12; 13 |

|

X |

A1→Y A2→C |

- |

S→Cs P→Cp |

max {tpi,tsi} |

102 |

|||

Конкретные значения параметров: A1 = 6 мкм; A2 = 6 мкм; Cs = 36 мкм; Cp = 36 мкм; Wmin = 6 мкм; Kt = 1; t0 = 1 нс.

Внешние условия включения:

Рисунок 1. Внешние условия включения

Фрагмент БИС реализует следующие функции:

S = XYC

P = XY

Алгебраическая модель

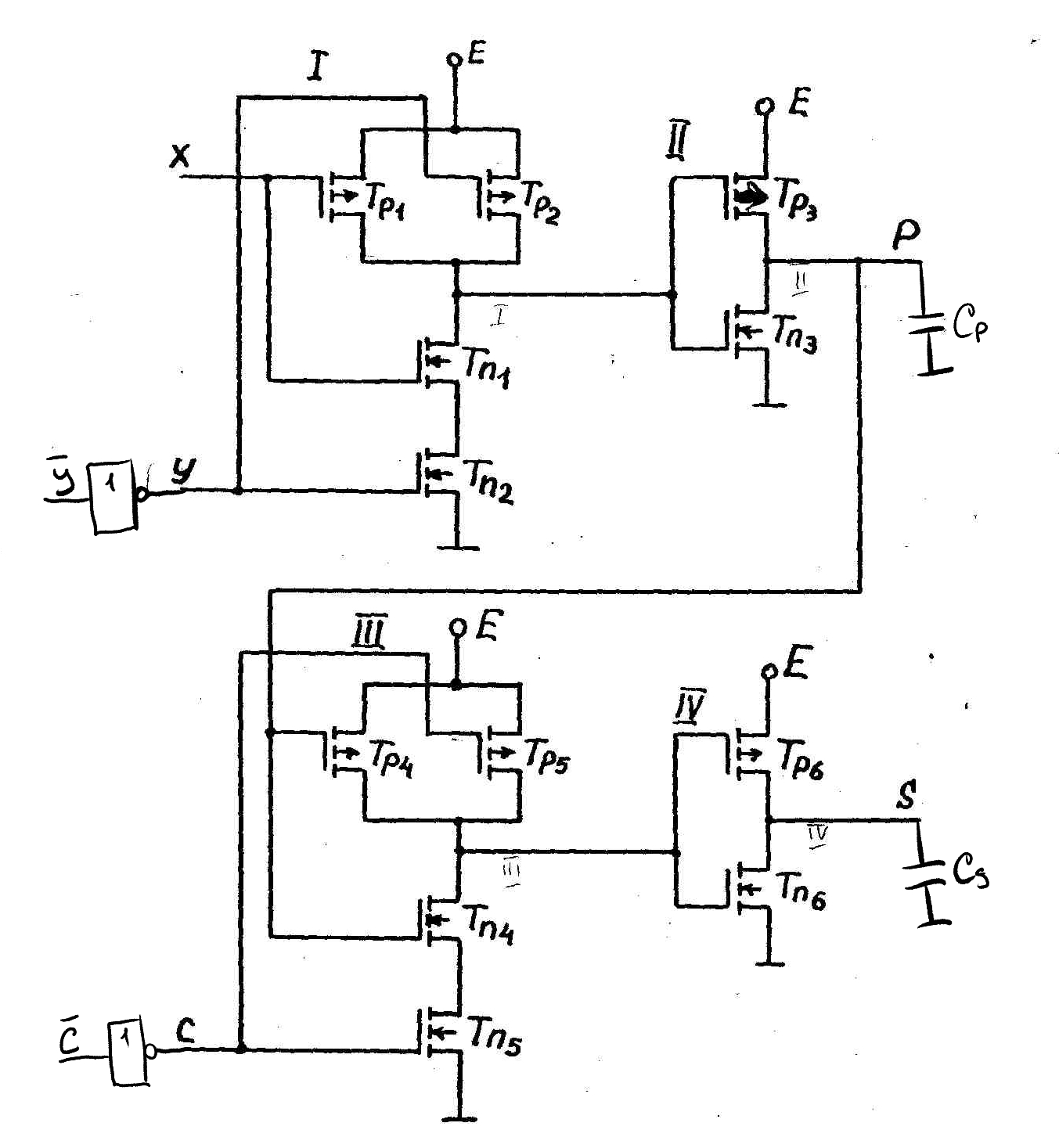

Схема №1 (рис. 11)

Рисунок 2. Схема 1

В таблице 2 представлены пути тока перезарядки для выхода P.

Таблица 2. Логическое моделирование схемы (схема 1, выход P)

№ варианта |

Входные сигналы |

Пути тока перезаряда нагрузочной емкости каскада |

|||

X |

Y |

C |

I |

III |

|

0 |

0 |

0 |

0 |

|

|

1 |

0 |

0 |

1 |

|

|

2 |

0 |

1 |

0 |

|

|

3 |

0 |

1 |

1 |

|

|

4 |

1 |

0 |

0 |

|

|

5 |

1 |

0 |

1 |

|

|

6 |

1 |

1 |

0 |

|

|

7 |

1 |

1 |

1 |

|

|

В таблице 3 представлены пути тока перезарядки для выхода S.

Таблица 3. Логическое моделирование схемы (схема 1, выход S)

№ варианта |

Входные сигналы |

Пути тока перезаряда нагрузочной емкости каскада |

|||

X |

Y |

C |

II |

IV |

|

0 |

0 |

0 |

0 |

|

|

1 |

0 |

0 |

1 |

|

|

2 |

0 |

1 |

0 |

|

|

3 |

0 |

1 |

1 |

|

|

4 |

1 |

0 |

0 |

|

|

5 |

1 |

0 |

1 |

|

|

6 |

1 |

1 |

0 |

|

|

7 |

1 |

1 |

1 |

|

|

Вывод формул времен задержек схемы 1

Обозначив через СK нагрузочную емкость K-того каскада схемы, запишем выражения для нагрузочных емкостей каскадов:

Рассмотрим времена переключения каскадов:

Для выхода P

Сначала определим некритические пути переключения транзисторов. Отметим некритические варианты переключения схемы, которые не будут участвовать в формулах времён задержек. Так как в вариантах 0 и 1 присутствуют параллельности в проводящем пути тока перезаряда, данные пути являются некритическими. Из-за того, что вход X предварительно установлен, варианты, в которых на него подаётся логический ноль (0, 1, 2, 3), являются также некритическими.

Таким образом, получим формулы времен задержек схемы по выходу P:

Для выхода S:

Так как в вариантах 0, 1, 2, 4 присутствуют параллельности в проводящем пути тока перезаряда, данные пути являются некритическими. Из-за того, что вход X предварительно установлен, вариант 3 является некритическим.

Таким образом, получим формулы времен задержек схемы по выходу S:

Вместе

формулы

представляют собой алгебраическую

модель схемы 1.

представляют собой алгебраическую

модель схемы 1.

Схема №2 (рис. 12)

Рисунок 3. Схема 2

В таблице 4 представлены пути тока перезарядки для обоих выходов.

Таблица 4. Логическое моделирование схемы (схема 2)

№ варианта |

Входные сигналы |

Пути тока перезаряда нагрузочной емкости каскада |

|||||

X |

Y |

C |

I |

II |

III |

IV |

|

0 |

0 |

0 |

0 |

|

|

|

|

1 |

0 |

0 |

1 |

|

|

|

|

2 |

0 |

1 |

0 |

|

|

|

|

3 |

0 |

1 |

1 |

|

|

|

|

4 |

1 |

0 |

0 |

|

|

|

|

5 |

1 |

0 |

1 |

|

|

|

|

6 |

1 |

1 |

0 |

|

|

|

|

7 |

1 |

1 |

1 |

|

|

|

|

Вывод формул времен задержек схемы 2

Обозначив через СK нагрузочную емкость K-того каскада схемы, запишем выражения для нагрузочных емкостей каскадов:

Рассмотрим времена переключения каскадов.

Для выхода P

Так как в вариантах 0, 1 присутствуют параллельности в проводящем пути тока перезаряда, данные пути являются некритическими. Из-за того, что вход X предварительно установлен, варианты 0, 1, 2, 3 являются некритическими.

Таким образом, получим формулы времен задержек схемы по выходу P:

Для выхода S:

Так как в вариантах 0, 1, 2, 4 присутствуют параллельности в проводящем пути тока перезаряда, данные пути являются некритическими. Из-за того, что вход X предварительно установлен, вариант 3 является некритическим.

Таким образом, получим формулы времен задержек схемы по выходу S:

Вместе формулы представляют собой алгебраическую модель схемы 2.

Схема №3

Рисунок 4. Схема 3

В таблице 5 представлены пути тока перезарядки для выхода P.

Таблица 5. Логическое моделирование схемы (схема 3, выход P)

№ варианта |

Входные сигналы |

Пути тока перезаряда нагрузочной емкости каскада |

|||

X |

Y |

C |

I |

III |

|

0 |

0 |

0 |

0 |

|

|

1 |

0 |

0 |

1 |

|

|

2 |

0 |

1 |

0 |

|

|

3 |

0 |

1 |

1 |

|

|

4 |

1 |

0 |

0 |

|

|

5 |

1 |

0 |

1 |

|

|

6 |

1 |

1 |

0 |

|

|

7 |

1 |

1 |

1 |

|

|

В таблице 6 представлены пути тока перезарядки для выхода P.

Таблица 6. Логическое моделирование схемы (схема 3, выход S)

№ варианта |

Входные сигналы |

Пути тока перезаряда нагрузочной емкости каскада |

||||

X |

Y |

C |

I |

II |

IV |

|

0 |

0 |

0 |

0 |

|

|

|

1 |

0 |

0 |

1 |

|

|

|

2 |

0 |

1 |

0 |

|

|

|

3 |

0 |

1 |

1 |

|

|

|

4 |

1 |

0 |

0 |

|

|

|

5 |

1 |

0 |

1 |

|

|

|

6 |

1 |

1 |

0 |

|

|

|

7 |

1 |

1 |

1 |

|

|

|

Вывод формул времен задержек схемы 3

Обозначив через СK нагрузочную емкость K-того каскада схемы, запишем выражения для нагрузочных емкостей каскадов:

Рассмотрим времена переключения каскадов.

Для выхода P

Так как в вариантах 0, 1 присутствуют параллельности в проводящем пути тока перезаряда, данные пути являются некритическими. Из-за того, что вход X предварительно установлен, варианты 0, 1, 2, 3 являются некритическими.

Таким образом, получим формулы времен задержек схемы по выходу P:

Для выхода S:

Так как в вариантах 0, 1, 2, 4 присутствуют параллельности в проводящем пути тока перезаряда, данные пути являются некритическими. Из-за того, что вход X предварительно установлен, вариант 0, 1, 2, 3 является некритическим.

Таким образом, получим формулы времен задержек схемы по выходу S:

Вместе формулы представляют собой алгебраическую модель схемы 3.