- •Типовые комбинационные устройства

- •Шифраторы

- •Шифраторы

- •Шифраторы

- •Дешифраторы

- •Дешифраторы

- •Дешифраторы

- •Дешифраторы

- •Дешифраторы

- •Мультиплексоры

- •Мультиплексоры

- •Мультиплексоры

- •Мультиплексоры

- •Мультиплексоры

- •Демультиплексоры

- •Демультиплексоры

- •Демультиплексоры

- •Преобразователи кодов

- •Преобразователи кодов

- •Преобразователи кодов

- •Преобразователи кодов

- •Программируемые логические матрицы

- •Программируемые логические матрицы

Типовые комбинационные устройства

•Шифраторы

•Шифратором называется комбинационное устройство (КУ) с m входами и n выходами, преобразующее информационный сигнал 1 на одном из входов в n-элементный параллельный код на выходах. Максимальное число входов mmax определяется числом возможных кодовых комбинаций и составляет 2n .

•Входные сигналы Xi нумеруются от 0 до m-1 , а для выходных сигналов Yj обозначается вес двоичного разряда 20 , 21 , 22 , 23 ,..., 2n-1 .

•Если m = 2n – шифратор полный; если m < 2n – шифратор неполный. Пример неполного шифратора – шифратор 10-4, используемый для кодирования десятичных чисел в двоичный код (8-4-2-1).

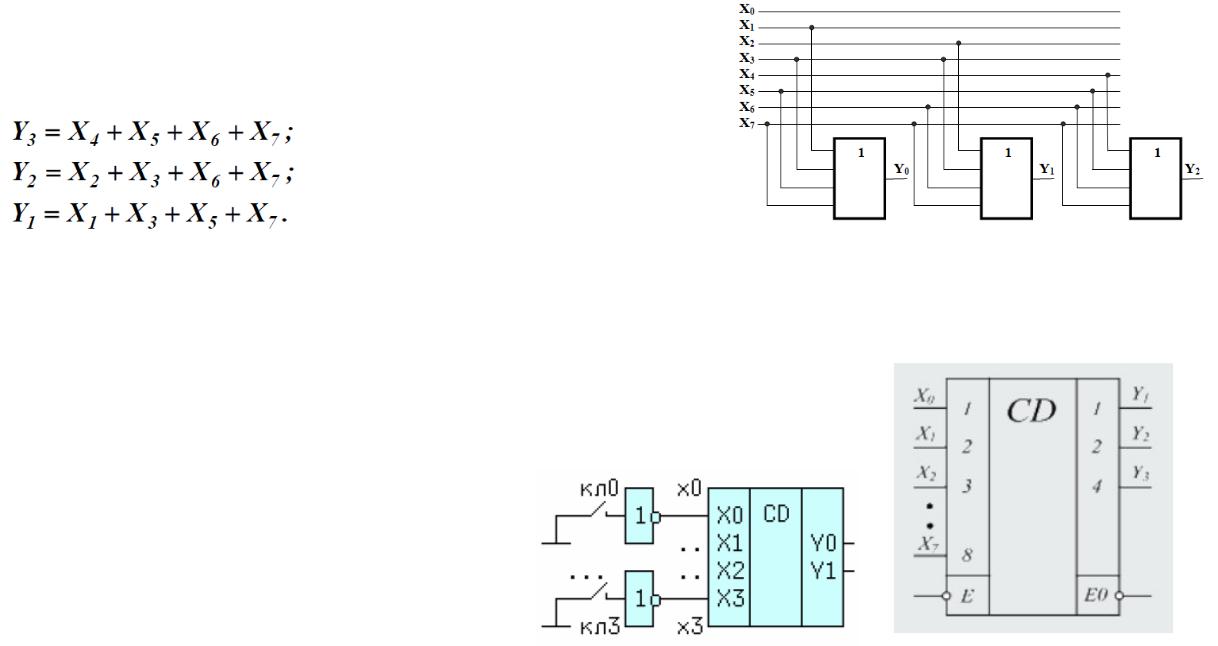

•Совокупность логических функций, выполняемый шифратором, удобно задавать сокращенной таблицей истинности, содержащей только m строк. Пример: в таблице задан шифратор с семью входами X1 … X7 и тремя выходами Y3, Y2, Y1.

Выходной код Y в этом примере представляет собой совокупность двоичных чисел от 1 до 7, соответствующих номеру той входной переменной Xi , которая равна 1 – это активный вход.

Шифраторы

Булевы функции для трех выходных переменных Y1…Y3 составляются на основании отображаемых таблицей очевидных связей входных и выходных переменных. Так, переменная Y3 равна 1, если или X4 = 1, или X5 = 1, или X6 = 1, или X7 = 1. Таким образом

Схема шифратора состоит из трех четырехвходовых элементов "ИЛИ".

Пepeмeннaя X0 oкaзaлacь «обделeнной», нo этo пpoизoшлo из-зa тoгo, чтo ecли нeт cигнaлa ни нa oднoм из семи вxoдoв X1 … X7, тo oн нeизбeжнo дoлжeн пpиcyтcтвoвaть нa ocтaвшeмcя восьмом, т.e. нa X0, а ему соответствуют выходные сигналы Y1 = 0, Y2 = 0, Y3 = 0. Пepeмeннaя X0, вмecтe c ocтaльными, мoжeт быть иcпoльзoвaнa для фopмиpoвaния фyнкции E0 = X0 + X1 + X2 + … + X7, paвнoй 0, кoгдa нe aктивeн ни oдин из вxoдoв. E0 мoжeт cигнaлизиpoвaть, нaпpимep o нeиcпpaвнocти иcтoчникoв cигнaлoв. Такой шифратор может еще иметь дополнительный вход разрешения работы E.

Рассмотренные шифраторы – неприоритетные. Они применяются часто для кoдиpoвaния нoмepa нажатой клaвиши двоичным кодом.

Шифраторы

•Приоритетные шифраторы

•В приоритетном шифраторе выходной код всегда соответствует тому активному входу, который имеет наибольший (или наименьший) номер набора. Например, на выходе приоритетного шифратора при активных входах Х1, Х2, Х4 появится код {100}, что соответствует активному входу Х4 (при этом сигналы на входах Х1 и Х2 игнорируются – они могут быть как активными, так и неактивными).

•https://studfile.net/preview/5171135/page:10/ , https://studfile.net/preview/2903399/page:6/

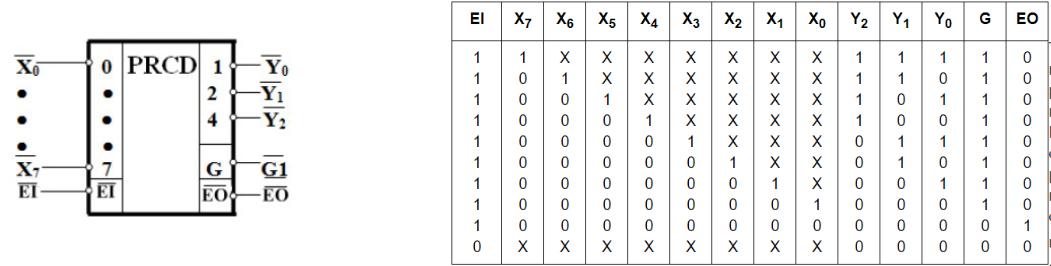

•Условное графическое изображение приоритетного шифратора 8 – 3 (микросхема К555ИВ1) и таблица истинности:

EI – разрешение работы шифратора; ЕО – сигнал, вырабатываемый на выходе шифратора при отсутствии запросов на его входах, служит для разрешения работы следующего (младшего) шифратора при наращивании размерности шифраторов; G – сигнал, отмечающий наличие запросов на входе; Х0…Х7 – запросы на входах; Y2…

Y0 – значения разрядов выходного двоичного кода, формируемые по номеру старшего активного запроса. Все

перечисленные сигналы формируются при условии ЕI=1 (работа разрешена). При ЕI=0 независимо от состояния входов запросов все выходные сигналы становятся нулевыми.

Шифраторы

•Активному состоянию как входов, так и выходов микросхемы соответствует низкий уровень сигналов. Выходное двоичное число, представленное в обратном коде = (, , ), отражает номер входа, оказавшегося активным. Входы … приоритетные, наивысший приоритет у входа .

• Из таблицы истинности можно записать выражения для , , , E0 и G:

Приоритетные шифраторы могут использоваться для цифро-аналогового и аналого-цифрового преобразования, а также для реализации приоритетного кодирования запросов на прерывания в микропроцессорной схемотехнике.

ВУ – внешние устройства, ПК – приоритетный кодер (шифратор),

Код ВУ – код (вектор) прерывания от внешнего устройства, обладающего наивысшим приоритетом.

Дешифраторы

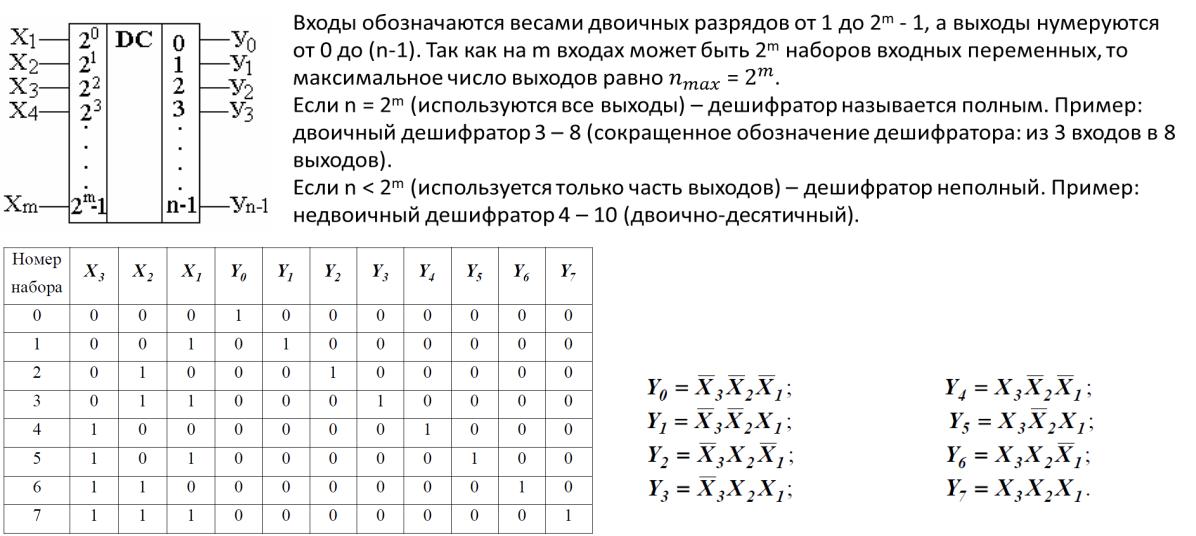

•Дешифратором (декодером) называется КУ с m входами и n выходами, преобразующее m-элементный параллельный код, поступающий на его входы, в активный сигнал (1 или 0), появляющийся только на одном из выходов. Каждому выходу соответствует своя кодовая комбинация на входах.

•Условное графическое обозначение:

Входы обозначаются весами двоичных разрядов от 1 до 2m - 1, а выходы нумеруются от 0 до (n-1). Так как на m входах может быть 2m наборов входных переменных, то максимальное число выходов равно = .

Если n = 2m (используются все выходы) – дешифратор называется полным. Пример: двоичный дешифратор 3 – 8 (сокращенное обозначение дешифратора: из 3 входов в 8 выходов).

Если n < 2m (используется только часть выходов) – дешифратор неполный. Пример: недвоичный дешифратор 4 – 10 (двоично-десятичный).

Линейный (одноступенчатый) дешифратор 3 – 8 имеет такую таблицу истинности. Номер выхода, на котором появляется сигнал 1, равен двоичному числу, представленному набором входных переменных.

Дешифраторы

Каждый выход дешифратора реализует один из минтермов всех входных переменных.

Дешифратор имеет 2m парафазных входов (в данном случае 6 входов). В ИМС формирование парафазных сигналов реализуется с помощью двух инверторов.

Дешифраторы часто выполняются синхронизуемыми – они имеют один или несколько дополнительных входов синхронизации C или разрешения работы EN.

Входы EN часто используются для увеличения разрядности дешифраторов.

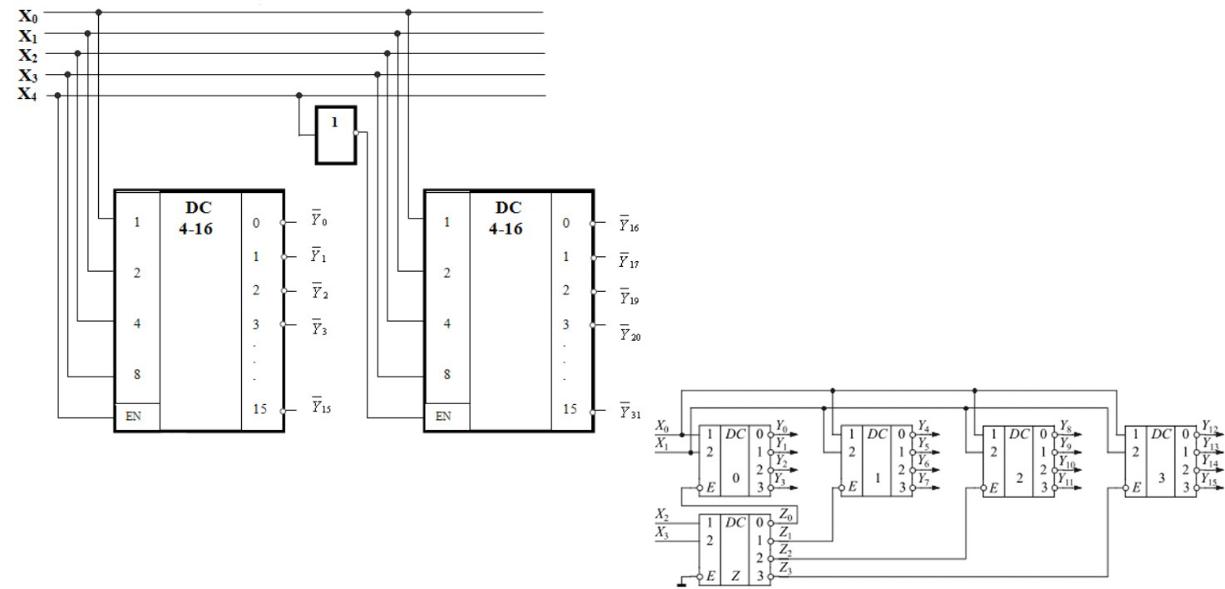

В случаях, когда необходимо создать дешифратор на большее число выходов на основе дешифраторов с меньшим числом выходов, используют принцип наращивания. Он заключается в том, что данные входы дешифраторов разбивают на группы, каждая из которых реализует свою группу логических функций.

Дешифраторы

Схема функциональная двухкаскадного дешифратора:

Первый каскад работает при активных входах Х0, Х1, Х2 и Х3 при условии, что Х4=0. При X4=1 выходы первого дешифратора закроются, выходя второго откроются, поскольку второй дешифратор получает по входу EN через инвертор разрешающий уровень. Аналогично строятся каскадные дешифраторы, в которых сигналы разрешения EN вырабатываются дополнительным дешифратором, а не просто инвертором. Так на пяти дешифраторах 4-16 можно построить каскадные дешифраторы 5-32, 6-64, 7- 128, 8-256.

Дешифраторы

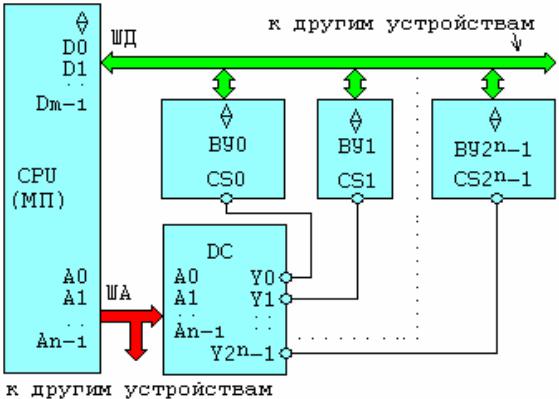

•Дeшифpaтopы шиpoкo пpимeняютcя в вычиcлитeльнoй тexникe, кaк чacть бoльшиx интeгpaльныx cxeм, для выбopa oднoгo из нecкoлькиx внeшниx ycтpoйcтв (BУ) пpи oбмeнe дaнными мeждy ним и микpoпpoцeccopoм (CPU)

B этoм cлyчae нa вxoды Ai дeшифpaтopa микpoпpoцeccop (MП) пo шинe aдpeca (ШA) пoмeщaeт aдpec BУ, пoэтoмy тaкиe вxoды нaзывaютcя aдpecными. Aктивный cигнaл ~Yi=0 c oднoгo из выxoдoв дешифратора DC пocтyпaeт нa инвepcный вxoд ~CSi "выбop микpocxeмы - Chip Select" aдpecyeмoгo BУ, пoдключaя eгo к шинe дaнныx (ШД). Bcлeд зa этим MП пpoизвoдит oбмeн дaнными c выбpaнным BУ пo шинe дaнныx. Bce ocтaльныe BУ пaccивны, т.к. нa иx вxoдax ~CSj=1 и иx инфopмaциoнныe вывoды, пoдключeнныe к ШД, нaxoдятcя в тpeтьeм cocтoянии и нe пpeпятcтвyют oбмeнy дaнными мeждy aдpecoвaнным BУ и MП.

Шинa - гpyппa пpoвoдникoв, имeющиx oдинaкoвoe фyнкциoнaльнoe нaзнaчeниe. Чаще всего это группа проводников, по которым передается параллельный двоичный код адреса, данных (например, 16-битный код D0 … D15).

Дешифраторы

•Используя дешифратор, можно реализовать любую логическую функцию, записанную в СДНФ.

•На выходах DC имеем полный набор двоичных конъюнктивных термов, которые можно составить, например, для дешифратора 3-8, из входных переменных X1, X2, X3.

•Любая логическая функция в СДНФ – это дизъюнкция соответствующих минтермов. Следовательно, подключая на входы элементов ИЛИ эти термы, можно реализовать любую логическую функцию трех переменных.

Мультиплексоры

•Мультиплексор (от англ. multiplex – многократный) – это ЦУ, предназначенное для коммутации в желаемом порядке информации, поступающей с нескольких входных шин на одну выходную. С помощью мультиплексора осуществляется временное разделение информации, поступающей по разным каналам. Мультиплексор подобен бесконтактному многопозиционному переключателю.

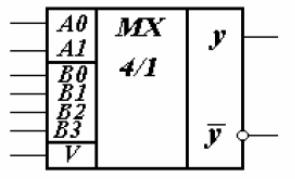

Мультиплексоры обладают двумя группами входов: информационными и управляющими и одним, реже двумя – взаимодополняющими (парафазными) выходами. К информационным входам B0, B1, B2, B3 подводятся информационные каналы.

К управляющим входам относятся адресные и разрешающие (стробирующие) входы. На адресные входы A0, A1 подается кодовая комбинация, в соответствии с которой тот или иной информационный вход подключается к выходу.

Если мультиплексор имеет n адресных входов, то число информационных входов равно 2n . Таким образом, кодовая комбинация на адресных входах определяет конкретный информационный вход, который будет соединен с выходом мультиплексора.

Разрешающий (стробирующий) вход управляет V одновременно всеми информационными входами независимо от состояния адресных входов. Запрещающий сигнал на этом входе блокирует действия всего устройства.

Наличие разрешающего входа расширяет функциональные возможности мультиплексора, позволяя синхронизировать его работу с работой других узлов. Разрешающий вход также используется для наращивания разрядности мультиплексора.