Регистры

•Регистры предназначены для хранения информации, которая поступает и хранится в регистре в виде n-разрядных двоичных чисел. Основу регистра составляют запоминающие устройства — триггеры. Кроме хранения, регистр может осуществлять преобразование принятого числового кода – сдвиг влево или вправо (арифметический и логический, преобразование двоичного кода из прямого в обратный (инвертирование разрядов кода), и наоборот, поразрядные логические сложение и умножение.

•В зависимости от способа ввода и вывода разрядов числа различают регистры:

параллельные,

последовательные,

параллельно-последовательные,

последовательно-параллельные,

комбинированные.

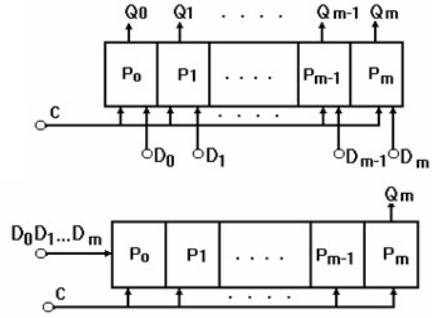

Впараллельном регистре ввод и вывод всех разрядов числового кода осуществляется одновременно.

Все разряды числового кода поступают на входы триггеров Po … Pm по линиям Do … Dm одновременно, стробируются сигналом C. Выходной код считывается одновременно с выходов триггеров Qo … Qm.

Впоследовательном регистре разряды числа вводятся и выводятся последовательно, разряд за разрядом.

Каждый синхроимпульс C сдвигает код в разрядах Po … Pm вправо на один разряд, а в разряд Po записывается очередной бит данных из входной последовательности Dm … Do. Выход – из последнего разряда Qm. Этот регистр осуществляет задержку на m+1 тактов.

Регистры

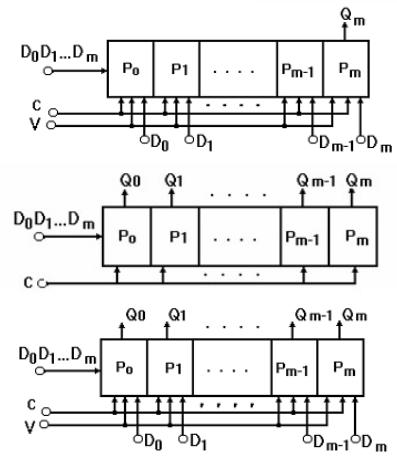

Впараллельно-последовательном регистре ввод числа производится в параллельной форме, а вывод — в последовательной. На рисунке дополнительный вход V – для сигнала разрешения параллельного ввода данных.

Впоследовательно-параллельном регистре ввод кода производится в последовательной форме, а вывод —в параллельной .

Вкомбинированном регистре как ввод, так и вывод числовых кодов могут происходить в любой форме (последовательной или параллельной). Режим работы такого регистра задается комбинацией управляющих сигналов.

Регистр, в котором можно осуществить сдвиг числа, называют сдвигающим (сдвиговым), причем сдвиг может быть или в одну сторону (в сторону младшего разряда или в сторону старшего разряда), или в обе стороны (реверсивный сдвигающий регистр). В этом смысле все последовательные регистры относят к сдвиговым.

Регистры могут также использоваться в качестве счетчиков и делителей частоты, узлов временной задержки импульсов и формирователей заданной временной последовательности импульсов.

Основными характеристиками регистров являются разрядность и быстродействие. Разрядность регистра определяет количество разрядов записываемого слова. Быстродействие регистра определяется максимально возможной тактовой частотой, с которой производится запись, сдвиг и считывание информации.

Регистры

•Регистры хранения (памяти) предназначены для записи, хранения и считывания информации. Регистры хранения строятся чаще всего на синхронных одно- и двухтактных RS- и D-триггерах. Но могут также использоваться и JK-триггеры.

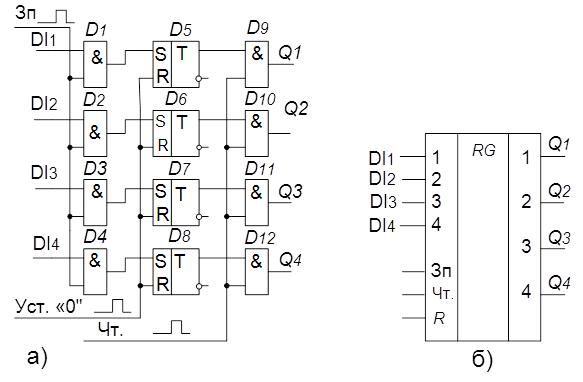

•Принцип построения регистра хранения на RS –триггерах:

Это схема 4-разрядного параллельного регистра, построенного на RS – триггерах D5…D8. Элементы D1…D4 образуют цепь управления записью, а элементы D9…D12 – цепь управления чтением. Перед записью информации все триггеры регистра устанавливают в состояние «0» путём подачи импульса «1» на их R – входы. Записываемая информация подаётся на входы DJ1…DJ4. Для записи информации подаётся импульс «Зп», открывающий входные элементы «И». Код входного числа записывается в регистр. По окончании импульса «Зп» элементы D1…D4 закрываются, а информация, записанная в регистр, сохраняется несмотря на то, что входная информация может изменяться.

Регистры

•Для считывания информации подают сигнал 1 на вход «Чт». По этому сигналу на выходные шины регистра на время действия сигнала передаётся код числа, записанный в регистр. По окончанию операции чтения выходные ключи закрываются, а информация, записанная в регистр, сохраняется. То есть возможно многократное считывание информации. Условное графическое обозначение параллельного регистра приведено на рисунке б).

•Регистр памяти на D-триггерах:

Общими для разрядов регистра являются цепи управления: синхронизации или разрешения записи (С) и сброса или начальной установки (Уст. “0”). Из принципа работы синхронного D-триггера следует, что разряды числа А=а3а2а1а0 запишутся в соответствующие

триггеры только после подачи сигнала (импульса) на вход синхронизации С, т.е. при С=1. После смены сигнала на входе С на “0” триггеры переходят в режим хранения. В это время на входы D триггеров можно подать следующее слово, например, В=b3b2b1b0, которое

при появлении сигнала С=1 запишется в регистр. Считывание слова осуществляется с прямых выходов триггеров (возможно считывание и с инверсных выходов). Для установки триггеров в нулевое состояние применяется специальная шина “Уст. “0”, связанная с асинхронными R-входами каждого триггера.

Регистры

•Примеры ИМС регистров хранения.

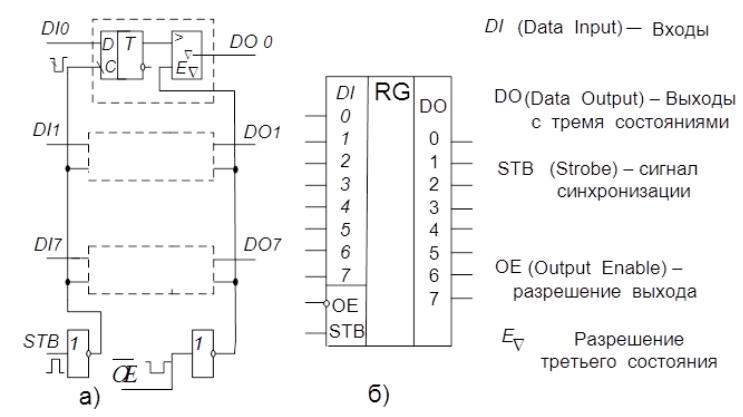

•Буферный регистр КР580ИР82, входящий в состав МП – комплекта КР580, построен на D – триггерах и

предназначен для записи и сохранения 8 – разрядных данных в течение заданного промежутка времени. Этот регистр называют также регистром – защёлкой. Например, в МП – системах КР580 он используется для сохранения в течение машинного цикла байта состояния, а на МП 1810 – адреса, поступающего по мультиплексированной шине адреса – данных. Его функциональная схема и условное графическое обозначение приведены на рисунке:

Регистр состоит из восьми D – триггеров, тактируемых фронтом, и восьми элементов с тремя выходными состояниями.

Если на вход OE поступит разрешающий сигнал низкого уровня, а на вход STB – сигнал высокого уровня, то информация с входов передаётся на выходы. После перехода сигнала на входе STB с высокого уровня на низкий информация, записанная в регистр, сохраняется до появления следующего разрешающего сигнала на входе STB. Сигнал OE высокого уровня переводит выводы DO0 – DO7 в 3-е состояние.

Регистры

• Таким образом, микросхема может работать в трёх режимах: oOE=0, STB=1 – режим шинного формирователя;

oOE=0, STB=0 – режим защёлки;

oOE=1 – 3-е состояние (режим отключения от нагрузки).

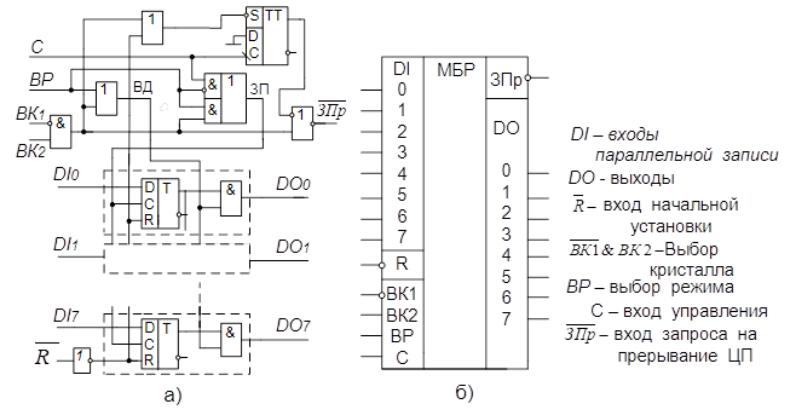

•Многорежимный буферный регистр (МБР) К589ИР12 является универсальным 8-и разрядным регистром, состоящим из D – триггеров и выходных буферных схем с 3-мя устойчивыми состояниями. МБР имеет также встроенную

селективную логику: «Схема управления режимами» и отдельный D – триггер для формирования запроса на прерывание центрального процессора. МБР предназначен для использования в качестве портов ввода информации в МП от внешних устройств, или портов вывода информации из МП во внешние устройства.

Схема управления режимами в зависимости от сочетания управляющих сигналов С, ВР, ВК1, ВК2 обеспечивает:

-Запись входной информации от внешнего устройства;

-Хранение информации;

-Выдачу информации;

-Передачу входной информации на выход (режим шинного формирователя).

Регистры

• Схема управления прерываниями формирует запрос на прерывание для МП по окончании сигнала записи информации в МБР от внешнего устройства по спаду сигнала «С». Сброс сигнала ЗПр осуществляется по входу S триггера D5 при выборе кристалла микропроцессором для считывания информации, а также при начальной установке МБР сигналом «R».

•Регистровая (сверхоперативная) память. Поскольку интегральные триггеры представляют собой элементарные ячейки памяти, способные хранить 1 бит информации, регистры хранения также используются для хранения информации чаще всего в виде полубайта (4 бита) и байта (8 бит). Они обладают очень высоким быстродействием по сравнению с другими видами памяти, поэтому называются сверхоперативной памятью. Под регистровой памятью понимается объединение нескольких регистров в один блок, выполняющий функции запоминающего устройства. В них отдельные регистры объединены в единую регистровую структуру (РС).

•Если к любому регистру можно обращаться по адресу, такая регистровая структура образует СОЗУ с произвольным доступом.

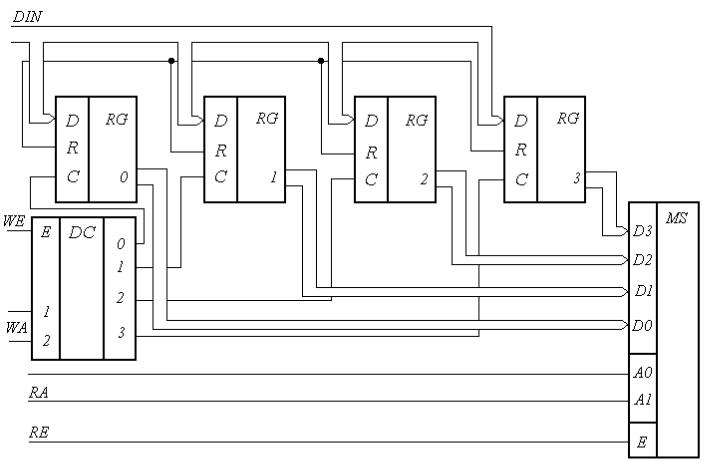

•Микросхемы регистровой памяти содержат несколько регистров. На рисунке показана структурная схема регистровой памяти 4 х 4 (4 регистра 4-разрядных данных). Кроме самих регистров, РС содержит:

На входе – дешифратор адреса записи: с его помощью выбирается по заданному адресу регистр, в который будут записаны данные;

На выходе – мультиплексор, передающий в выходную шину результат чтения данных с выбранного регистра.

Регистры

• Вход загрузки требуемого регистра выбирается дешифратором записи DC на основании адреса записи WA , т. е. кода номера загружаемого регистра. Запись данных, присутствующих на шине DIN, происходит в момент поступления сигнала разрешения записи WE.

• Выходы регистров мультиплексором MS подключаются к выходной шине DOUT. Номер регистра, с которого происходит чтение, определяет код адреса чтения RA. Выдачу данных в шину DOUT разрешает сигнал RE. Поскольку дешифрация адреса записи и адреса чтения производится двумя независимыми узлами, имеющими автономные адресные входы WA и RA, регистровая память может одновременно записывать число в один из регистров и читать число из другого.

Описанная структура использована в кристалле отечественных микросхем К155РП1, ИР11 и ИР12 серий К561 и К564.

Микросхемы регистровой памяти легко наращиваются по разрядности и допускают наращивание по числу регистров. Они разработаны для построения блоков регистров общего назначения (РОН), предназначенных для временного хранения исходных данных и промежуточных результатов в микропроцессорах.

Регистры

•Регистры сдвига, кроме функций, выполняемых регистрами памяти, позволяют осуществлять сдвиг информации вправо и влево под воздействием тактовых импульсов. Если в регистры хранения двоичное слово записывается параллельным кодом, то в регистры сдвига – последовательным.

•Регистры сдвига реализуются, как правило, на синхронных D- или JK-триггерах со статическим или динамическим управлением. Такие регистры имеют информационный вход, вход тактовых импульсов и установочный вход (сброса в 0). Выходы в регистре сдвига могут быть с триггера каждого разряда для считывания информации параллельным кодом или только с последнего разряда для считывания информации последовательным кодом.

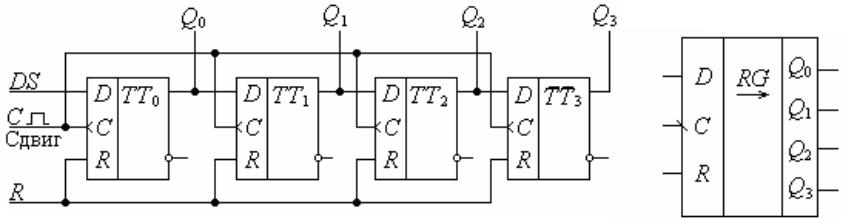

•Схема 4-разрядного регистра сдвига вправо на синхронных двухтактных D-триггерах с входом синхронизации С:

Регистр обеспечивает запись информации по входу DS последовательным кодом и ее считывание как в последовательном, так и в параллельном коде с выходов Q0…Q3. Регистр имеет вход тактирующих импульсов сдвига C и вход асинхронной установки R всех разрядов в состояние логического 0.

Стрелка под обозначением регистра RG в основном поле показывает направление сдвига информации.

Регистры

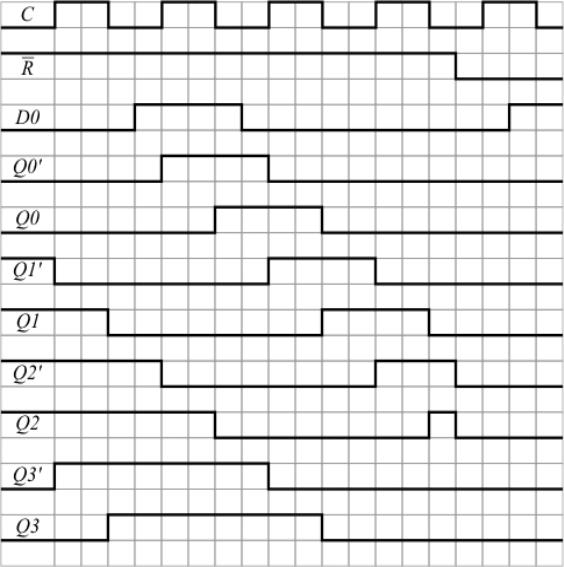

•Идеализированная временная диаграмма работы регистра сдвига на двухтактных D-триггерах. Начальное состояние регистра следующее: Q0=0, Q1=1, Q2=1, Q3=0.

•Работа регистра сдвига в каждом периоде сигнала синхронизации разбивается на две фазы: при высоком и при низком значении синхросигнала:

•При высоком уровне синхросигнала проводится запись значения выхода (i–1)-го разряда регистра в первую ступень i-го разряда Q0’…Q3’. Вторая ступень каждого разряда Q0…Q3 сохраняет свое прежнее значение. В этой фазе состояние первой ступени i-го триггера повторяет состояние второй ступени (i–1)-го триггера. Вторые ступени каждого триггера, а следовательно, и выходы регистра в целом, остаются неизменными.

•При низком уровне синхросигнала значение, записанное в первой ступени каждого триггера, перезаписывается в его вторую ступень. Запись в первую ступень триггера запрещена. В этой фазе состояния первой и второй ступеней каждого триггера становятся одинаковыми.

•Поступление сигнала R низкого уровня вне зависимости от значения сигнала на входе синхронизации C и сигнала на последовательном входе D0 устанавливает все разряды регистра в нулевое состояние.