9201_Рауан_ЛР1

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра МВЭ

ОТЧЕТ

по лабораторной работе №1

по дисциплине «Основы проектирования электронной компонентной базы»

Тема: «: «Основные приёмы работы с программой AIM-Spice»

Студент гр. 9201 |

|

Рауан М. |

Преподаватель |

|

Шевченко С.А. |

Санкт-Петербург

2022

Задание №0-1

Пример 1

Рисунок 1 - Моделирование диода

Рисунок 2 - ВАХ диода

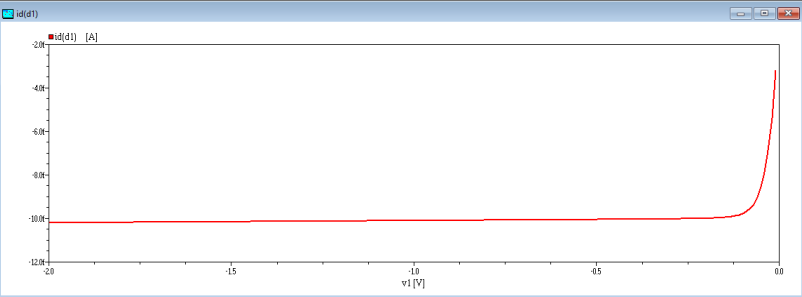

Рисунок 3 - Обратная ВАХ диода

Пример 2

Рисунок 4 - Моделирование схемы синусоидального генератора

Синусоидальный сигнал:

Рисунок 5 - Синусоидальный сигнал

Импульсный генератор:

Рисунок 6 - Импульсный сигнал

Рисунок 7 - Анализ схемы по постоянному току

Рисунок 8 - Анализ схемы малого сигнала

Задача 1:

Рисунок 9 - Схема задания

Рисунок 10 - Моделирование исходной схемы.

Рисунок 11 - ВАХ резистора RL.

Ответ: = 1.54 мА

= 1.54 мА

Задача 2:

Рисунок 12 - Исходная схема

Рисунок 13. Моделирование исходной схемы.

Рисунок 14. ВАХ резистора R3.

Таблица 2. Результат вычислений V2.

Ответ: V2=16.6

Задача 3:

Рисунок 15 - Исходная схема

А) Ток через R3 должен быть равен нулю, так как схема является Уитстона, соответственно:

Б) Последовательное соединение:

Рисунок 16 - Моделирование исходной схемы.

Рисунок 17 - ВАХ резистора R3.

При последовательном подключении можно получить нулевой ток при напряжении V2=4.58 В.

В) Параллельное соединение:

Рисунок 17 - ВАХ резистора R3.

При параллельном подключении получить нулевой ток невозможно.

ЗАДАНИЕ 3

Промоделируем работу двух SPICE-моделей МОП-транзистора Level 1 и Level 3: МОП-транзистор «Level 1»:

Рисунок 3.1. - Моделирование МОП-транзистора «Level 1»

МОП-транзистор «Level 3»:

Рисунок 3.2. - Моделирование МОП-транзистора «Level 3»

Level 1 result:

Рис. 3.3 - ВАХ моделируемого транзистора (Level 1)

Анализ:

В результате расчета модели получим выходные характеристики транзистора (рис. 3.3). В начале при подаче напряжения на сток наблюдается линейная зависимость тока от напряжения, транзистор ведет себя как резистор. При этом, чем большее напряжение на затворе, тем шире канал и меньше его сопротивление (больший ток при том же напряжении на стоке). При дальнейшем увеличении напряжение на стоке происходит перекрытие канала в области стока (увеличение его сопротивления), стоковый ток практически не растет.

Рис. 3.4. - ВАХ моделируемого транзистора (Level 3)

Вывод: в данной работе были рассмотрены две модели МОП-транзистора Level 1 и Level 3. Level 1- это модель Шихмана-Ходжеса (Shichman-Hodges), а Level 3- модель для МОП-транзисторов с коротким каналом (Semi-empirical short channel model).

Модель Level 1 (Шихмана-Ходжеса) имеет множество недостатков, к ним можно отнести то, что при расчетах не учитывается зависимость подвижности носителей от напряженности электрического поля, предпороговый режим, неоднородность легирования.

Модель Level 3 используется для расчета МОП-транзисторов с коротким каналом длина которого равна порядка 1-3 мкм. В ней для более точных вычислений используются эффекты второго порядка: модуляция длины канала, зависимость подвижности носителей заряда от вертикального поля, неоднородное легирование для транзисторов, изготовленных с применением ионной имплантации, распределение заряда обедненной области между стоком и истоком.

Отличительные параметры level 3 являются:

VMAX – максимальная скорость дрейфа для носителей с классическим значением 105 м/с; THETA – модуляция подвижности; DELTA – влияние размера транзистора на пороговое напряжение; ETA – статическая обратная связь; NFS(Fast surface state density) – плотность поверхностных состояний.

Остальные параметры есть как в модели level 3 так и в level 1:

VTO- Пороговое напряжение нулевого смещения; TOX- Толщина оксида затвора; U0- Подвижность на поверхности; LD- Боковая диффузия; RS- Сопротивление истока; RD- Сопротивление стока;

За счет дополнительных параметров модели МОП-транзистора level 3, на её выходной характеристике уменьшается пороговое напряжение Uds и ток насыщения. Насыщение тока стока при фиксированном напряжении на затворе связано с сужением проводящего канала со стороны стока и с сокращением его длины при увеличении Uds.

Из выше сказанного можно сделать вывод, что с переходом на новый «уровень», увеличивается количество параметров модели. Благодаря этому можно получить более точные характеристики, жертвуя временем на расчеты.

ЗАДАНИЕ 4

А) Рассчитаем передаточную характеристику для базового тока и выходную характеристику для коллекторного тока. Построим и сравним зависимости β(Ic) для двух моделей биполярного транзистора:

Рисунок 4.1. Моделирование схемы транзистора модели Эберса-Молла.

Рисунок 4.2. Моделирование схемы транзистора модели Гуммеля-Пуна.

Рисунок 4.3. Схема модели транзистора.

Рисунок 4.4. Зависимость коэффициента усиления по току от коллекторного тока.

Анализ: Схема модели Гуммеля-Пуна является более полной, так как она учитывает дополнительно следующие параметры: Ikf - ток начала спада зависимости h21э от тока коллектора в активном режиме. Vaf - напряжение Эрли (учитывает эффект модуляции ширины базы).

На

зависимости

модели

Гуммеля-Пуна можно выделить два основных

участка:

модели

Гуммеля-Пуна можно выделить два основных

участка:

- Спад в области малых токов связан с уменьшением коэффициента инжекции вследствие рекомбинации носителей в базо-эмиттерном переходе.

То есть часть электронов рекомбинируют с дырками (для npn)

- В области больших токов наблюдается спад коэффициента усиления вследствие действия следующих факторов: уменьшения удельного сопротивления базы и увеличения эффективной толщины базы. (Эффект Кирка)

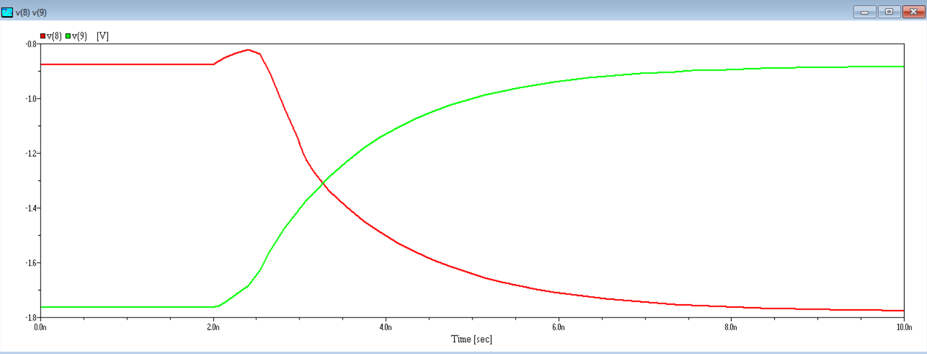

Б) Смоделируем эмиттерно-связанную логику. Нарисуем схему, и проведем расчёты передаточных характеристик для выходных напряжений V8 и V9 от напряжения на входе V12 (в диапазоне от -2 до 0 В), а также переходных характеристики для тех же напряжений:

Рисунок 4.5. Моделирование схемы эмиттерно-связанной логики.

Рисунок 4.6. Схема эмиттерно-связанной логики.

Рисунок 4.7. Переходная характеристика для выходных напряжений V9 и V8 и входного напряжения V1.

Рисунок 4.8. Передаточная характеристика для выходных напряжений V9 и V8 и входного напряжения V1.

Вывод: в ходе данной работы были исследованы две модели биполярного транзистора: Эберса-Молла и Гуммеля-Пуна. Для модели Гуммеля-Пуна спад зависимости коэффициента усиления от коллекторного тока начинается гораздо раньше и идет по экспоненте, что может объясняться рекомбинацией в базе при высокой инжекции носителей заряда

Такой ход кривой обеспечивается за счет учета эффектов второго порядка: эффекта Эрли (влияние расширения области объемного заряда на ток связи между эмиттером и коллектором, или другими словами, эффект модуляции ширины базы), эффект Кирка (расширение базы в область коллектора), рекомбинации в области объёмного заряда эмиттерного перехода при малых напряжениях смещениях эмиттер-база, снижения коэффициента усиления по току, которое наблюдается при больших токах. Модель Эберса-Молла стоит использовать только для начальной части зависимости коэффициента усиления от коллекторного тока (при низких значениях тока коллектора), т.к. далее она имеет сильные расхождения с практической зависимостью.

Также в работе была рассмотрена эмиттерно-связанной логика. Время переключения схемы на ЭСЛ составляет около 10 нс. Из этого можно сделать вывод, что данная схема логики имеет высокое быстродействие. К плюсам данная схемы логики можно отнести: работает не в режиме насыщения, возможность работы с низкоомной нагрузкой, высокая термостабильность, независимость потребления энергии от частоты переключения. Минусами являются высокое энергопотребление, сложность схем и трудность согласования с микросхемами ТТЛ.