ПиПИИЭ КР ЗАО

.docxМинистерство образования Республики Беларусь

Учреждение образования

БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ

ИНФОРМАТИКИ И РАДИОЭЛЕКТРОНИКИ

Факультет компьютерного проектирования

Кафедра электронной техники и технологии

Дисциплина: Проектирование и производство изделий интегральной электроники

КОНТРОЛЬНАЯ РАБОТА

Студент: гр. 990241 Петушок И.М.

Руководитель: преподаватель

Голосов Д. А.

Минск

2023

13. Расчёт и проектирование плёночных проводников и контактных площадок

Проводники, контактные площадки и иные токопроводящие элементы

на изображении платы подлежат штриховке (см. рис. 1). Допускается вычерчивать проводники сплошной утолщенной линией: а) если ширина проводника в изображении (с учетом масштаба изображения) не превышает 2 мм; б) действительная ширина проводника оговорена в технических требованиях на поле чертежа. Контактные площадки, примыкающие к проводникам, и промежутки между окружностями, имеющие размер до 2 мм, в этих случаях также не штрихуют.

Рис. 1. Табличный способ указания координат элементов на чертеже печатной платы

Участки платы, которые нельзя занимать проводниками, обозначают штрихпунктирными линиями с указанием размеров (см. рис. 1, зонаД).

Примеры выполнения чертежей печатных плат комбинированным способом простановки размеров и с указанием размеров в таблице координат приведены соответственно на рис. 8.32 и 8.34.

Чертеж печатной платы со стороны навесных элементов должен содержать сведения о маркировке элементов и их расположении относительно контактных площадок. Маркировкой вводят позиционные обозначения, присвоенные всем элементам, устройствам и функциональным группам изделия в соответствии с его принципиальной электрической схемой. Позиционное обозначение состоит из буквенного кода вида элемента (R — резистор, С — конденсатор, L — катушка индуктивности, V — прибор полупроводниковый, D — элемент логический двоичный, А — усилитель и общее обозначение устройств) и порядкового номера элемента в пределах данного вида, начиная с единицы. Порядковые номера проставляют слева направо сверху вниз по принципиальной электрической схеме.

Над или справа от изображения элемента или контактных площадок на плате указывают наименование (буквенное обозначение или символ) вывода прибора, имеющего направленное включение: для диодов — «+» (основание треугольника) и «— »; для транзистора — К (коллектор), Б (база) и Э (эмиттер).

Допускается размещать на главном виде печатной платы электрическую схему изделия. В этом случае чертеж платы со стороны навесных элементов не выполняется.

Чертежи многослойных печатных плат применяются для конструирования интегральных микросхем и других изделий функциональной микроэлектроники.

Интегральная микросхема (далее — ИС) — микроэлектронное изделие, выполняющее функции преобразования и обработки сигнала и имеющее высокую плотность упаковки электрически соединенных элементов и компонентов, изготовленных в едином технологическом цикле.

Элемент ИС — часть интегральной микросхемы, реализующая функцию какого-либо электрорадиоэлемента, выполненная неразделимо от подложки и не имеющая самостоятельного значения как изделие.

Полупроводниковая ИС — интегральная микросхема, все элементы и межэлементные соединения которой выполнены в объеме и на поверхности полупроводника.

Пленочная ИС — интегральная микросхема, все элементы и межэлементные соединения которой выполнены в виде пленок. Различают толстопленочные (Я свыше 1 до 25 мкм) и тонкопленочные (Я < 1 мкм) ИС. Методами пленочной технологии изготовляют резисторы, конденсаторы, катушки индуктивности, соединительные проводники и контактные площадки.

Гибридная ИС — интегральная микросхема, содержащая, кроме элементов пленочного исполнения, навесные компоненты в виде бес- корпусных микросхем, дискретных транзисторов и прочих микрокомпонентов.

Подложка ИС — заготовка, предназначенная для нанесения на нее элементов гибридных и пленочных ИС, межэлементных и межкомпонентных соединений, в том числе контактных площадок.

Плата ИС — часть подложки гибридной ИС, на поверхности которой выполнены пленочные элементы полупроводниковой микросхемы, межэлементные соединения и контактные площадки.

Кристалл ИС — часть полупроводниковой пластины, в объеме и на поверхности которой сформированы элементы полупроводниковой микросхемы, межэлементные соединения и контактные площадки.

Процесс проектирования гибридной ИС разделяется на следующие этапы: а) разработка принципиальной электрической схемы; б) определение типоразмеров навесных элементов; в) расчет формы и размеров пленочных элементов; г) определение размеров диэлектрической подложки и выбор типа корпуса; д) разработка топологических чертежей изделия.

В комплект конструкторской документации на изделие — гибридную тонкопленочную микросхему — входят: а) схема электрическая принципиальная; б) сборочный чертеж со спецификацией; в) чертеж совмещенной топологии (платы с изображением всех нанесенных на нее слоев); г) топологические чертежи отдельных слоев пленочных элементов; д) чертежи деталей (подложки, элементов корпусов, выводных контактов).

Топологические чертежи гибридных интегральных микросхем определяют ориентацию, состав и взаимное расположение элементов и контактов на подложке (плате), а также форму и размеры пленочных элементов и соединений между ними. Чертежи выполняют в соответствии с правилами ЕСКД и дополнительными требованиями отраслевых стандартов (Табл. 1).

За главный вид топологического чертежа на первом листе принимают чертеж совмещенной топологии (Рис. 2.) — изображение после нанесения последнего слоя с указанием всех элементов схемы и их электрических связей. Элементы схемы, расположенные в разных по глубине слоях, выделяют различной штриховкой. Резистивный слой изображают площадками с точечным фоном; проводники, контактные площадки и обкладки конденсаторов штрихуют тонкими линиями различного направления и частоты; диэлектрический и защитный слои показывают соответственно штрихпунктирной и штриховой линией без штриховки защищенных участков. Обозначение штриховки вносят в таблицу на поле чертежа (табл, на рис. 3.).

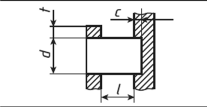

Таблица 1. Основные конструктивные требования и технологические ограничения изготовления гибридных интегральных микросхем (минимально допустимые размеры, мм)

Схема |

Требование или ограничение |

Обозначение |

Размер |

|

|

Расстояние от края платы до края отверстия |

а |

0,5 |

|

То же, до пленочного элемента |

Ь |

од |

|

|

Размеры контактных площадок |

с |

0,25 |

|

|

Для монтажа навесных элементов с жесткими выводами |

d |

од |

|

|

То же, для монтажа активных элементов с гибкими выводами: |

||||

при ручном монтаже |

с |

0,4x0,7 |

||

при автоматизированном монтаже |

» |

0,6x1,2 |

|

Схема |

Требование или ограничение |

Обозначение |

Разм |

|

|

|

|

Ширина проводника под пайку навесных элементов |

к |

0,4 |

|

|

|

То же, в зависимости от силы тока, А: |

|

|

|

|

|

|

до 0,3 |

» |

0,15 |

|

|

|

|

» 1,0 |

» |

0,30 |

|

|

|

|

» 2,0 |

» |

0,60 |

|

|

|

|

»3,0 |

» |

0,80 |

|

|

|

|

» 6,0 |

» |

1,0 |

|

|

|

|

|

Расстояние между пленочными элементами в разных слоях |

t |

0,4 |

|

|

|

|

Размеры резистора и его расположение относительно печатных проводников |

1 |

0,8 |

|

|

|

d |

0,8 |

|

|

|

||

t |

0,2 |

|

|

|

||

с |

0,2 |

|

|

|

||

|

Размеры взаимного положения слоев пленочного конденсатора |

а |

0,2 |

|

|

|

Ь |

0,3 |

|

|

|

||

|

Расстояние: |

|

|

|

|

|

от края активного элемента до края платы |

а |

1,0 |

|

|

|

|

от плено-чного луженого элемента до края навесного элемента |

Ь= 0,2 |

|||||

от края активного элемента |

d |

0,8 |

|

|

|

|

до контактной площадки (места пайки) |

1 |

2,5 |

|

|

|

|

от края активного элемента до контактной площадки навесного конденсатора |

с |

1,0 |

|

|

|

|

|

Расстоя-ние между соседними эле-ментами и контакт-ными площадками для элементов с гибкими выводами |

а |

0,2 |

|

|

|

с |

0,3 |

|

|

|

||

t |

0,2 |

|

|

|

||

То же между пленочными лужеными элементами с жесткими выводами при размерах элементов: |

|

|

|

|

|

|

до 1,85x1,85 мм |

t |

2,0 |

||||

свыше 1,85x1,85 мм |

t |

1,0 |

|

|

|

|

Рис. 2. Чертеж совмещенной топологии гибридной интегральной микросхемы (первый лист)

Рис. 3. Топологический чертеж резистивного слоя

Контактные площадки, располагаемые обычно по контуру платы, нумеруют от нижнего левого угла по направлению движения часовой стрелки. Внутренние площадки нумеруют в том же порядке последующими порядковыми номерами. Номера выводов на плате и принципиальной электрической схеме должны совпадать.

Для ориентирования при изготовлении и указания начала отсчета контактных площадок на плате предусматривают площадку «ключ» размером примерно 0,3x0,8 мм (см. Рис. 2.).

Допускается отдельные промежуточные слои, не используемые для монтажа микросхемы в изделии, на чертеже совмещенной топологии не изображать. В технических условиях, располагаемых на поле чертежа над основной надписью, делается в этом случае соответствующая запись.

Последующие листы топологических чертежей должны содержать изображение отдельных слоев изделия. На рисунке 3 показан чертеж резистивного слоя схемы по топологическому чертежу Рис. 2.

Каждая зона слоя (элемент в виде многоугольника) нумеруется: за начало отсчета координат принимают нижний левый угол платы. Вершины каждого многоугольника нумеруют, начиная с левого нижнего угла по часовой стрелке. К следующему многоугольнику переходят по направлению снизу вверх слева направо. Координаты всех точек записывают в таблице, размещаемой на поле чертежа.

Примеры построения типовых пленочных элементов показаны на Рис. 4.

Рис. 4. Структура типовых пленочных элементов интегральных микросхем:

а — резистор; б — конденсатор; в — индуктивность; 1 — проводник; 2 — защитный слой; 3 — резистивный слой; 4 — подложка; 5 — обкладка л-типа проводимости; 6 — диэлектрик; 7 — обкладка p-типа проводимости

Схемы оформления контактных площадок и выводов пленочных элементов даны на Рис. 5

Рис. 5 Конструктивные схемы контактных площадок и выводов пленочных элементов: 1 — плата (диэлектрик); 2 — проводник (металлизированный слой);

3 — вывод навесного элемента

Чертежи полупроводниковых ИС также разрабатываются в соответствии с принципиальной электрической схемой. Оформление этой схемы имеет следующие особенности: а) схема не сопровождается спецификацией или иным перечнем компонентов — номиналы элементов и другие данные указывают возле позиционных обозначений непосредственно на схеме; б) обязательным является указание внешних выводов; в) допускается совмещение на одном листе принципиальной и функциональной схем с указанием соответствующих параметров в виде таблиц или текстовой записи (Табл. 2).

На первом листе конструкторской документации помещают главный вид — чертеж совмещенной топологии (Рис. 6), изображающий подложку (кристалл) с координатной сеткой, со всеми нанесенными на нее слоями пленочных элементов и электрическими связями. Излагаются технические требования, приводятся типовая структура, обозначения и таблица характеристик слоев. Шаг координатной сетки выбирают из ряда, мм: 0,001; 0,005; 0,01; 0,025; 0,05; 0,1; 0,2. На чертеже совмещенной топологии также размещают фигуры совмещения, структура которых показана на Рис. 7, и сложный ступенчатый разрез через различные элементы и компоненты микросхем.

Рис. 6 Чертеж совмещенной топологии полупроводниковой интегральной микросхемы (первый лист)

Рис. 7 Структура фигур совмещения:

1 — поверхность кристалла; 2 — граница кристалла с оксидным покрытием; 3—1 — фигуры для топологии: разделительного слоя (3), базового слоя (4), эмитгерного слоя (5), контактных окон (6), слоя металлизации (7)

Таблица 2 Основные конструктивные требования и технологические ограничения изготовления полупроводниковых тонкопленочных интегральных микросхем (минимально допустимые размеры, мкм)

Схема |

Требо-вание или ограниче-ние |

Обозначение |

Способы изготовления |

|

|

|

|

|

||||||

масочный |

фотолитографический |

|

|

|

|

|

||||||||

|

Расстоя-ние пленочных элементов от края |

а |

500 |

200 |

|

|

|

|

|

|||||

Шаг располо-жения и размеры перифери-йных контакт-ных площадок |

ab |

625 |

1250;2500 и кратный 2,5 мм |

|

|

|

|

|

||||||

с |

400 |

1000x400 |

|

|

|

|

|

|||||||

Расстояние между элементами в одном слое |

d |

200 |

100 |

|

|

|

|

|

||||||

Ши-рина пленочных проводников |

к |

|

100 |

|

||||||||||

|

Размеры контактных пло- щадок и их расположение относительно пленочных элементов |

а |

|

200 |

||||||||||

Ь |

|

100 |

|

|

|

|

||||||||

с |

|

100 |

|

|

|

|

|

|||||||

I; к |

|

600 |

|

|

||||||||||

t;d |

|

350 |

|

|

|

|

|

|||||||

|

Размеры резисторов |

а |

100 |

100 |

|

|

|

|||||||

1 |

300 |

|

|

|

|

|

||||||||

Ь |

300 |

|

|

|

||||||||||

I* |

<10я |

|

|

|

|

|

||||||||

Схема |

Требование или ограничение |

Обо- значение |

Спо ГОТ( масочный |

собы из- звления фотолитографический |

|

Размеры пленочных конденсаторов |

а |

200 |

|

Ь |

100 |

|||

к |

200 |

|||

с |

300 |

|||

|

Размеры окон в защитном слое |

а |

100 |

|

Ь |

400 |

|

||