«Timing»

Рисунок 4.3 – Моделирование логического элемента 2И-НЕ в режиме

«Functional»

Из-за того, что в режиме работе «Timing» учитывает задержка на логических элементах, происходят выходы за границы интервала.

Также был написан код на языке описания аппаратуры SystemVerilog,

представленный на рисунке 4.4. Во второй строчке обозначены точки входа A

и B. В третьей строчке обозначена точка выхода C. Логический элемент 2И-

НЕ описывается четвертой строчкой после оператора «assign».

Рисунок 3.4 – Код на языке описания аппаратуры SystemVerilog логического элемента 2И-НЕ

11

5 УСТРОЙСТВО 2ИЛИ-НЕ

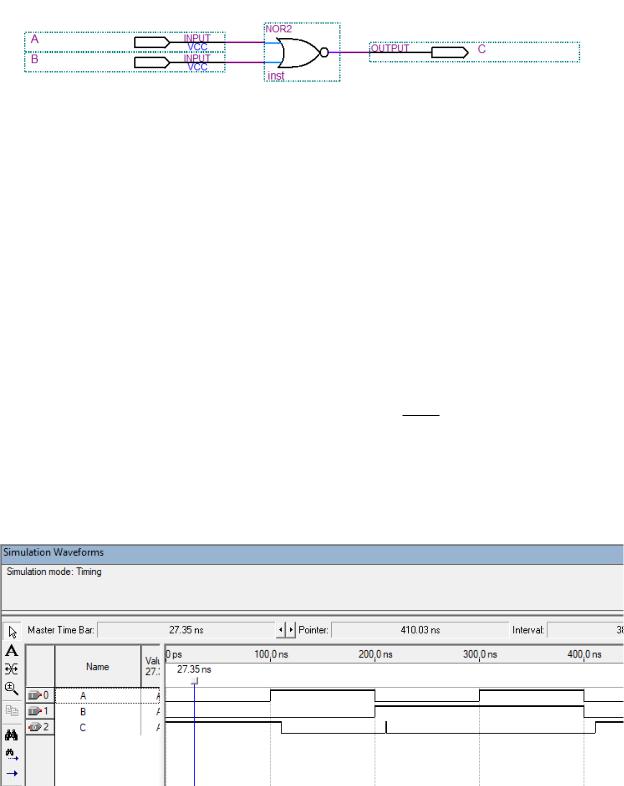

Для логического элемента 2ИЛИ-НЕ была собрана функциональная схема, представленная на рисунке 5.1.

Рисунок 5.1 – Функциональная схема логического элемента 2ИЛИ-НЕ Была составлена таблица истинности для логического элемента 2ИЛИ-

НЕ, представленная в таблице 5.1.

Таблица 5.1 - Таблица истинности для логического элемента 2ИЛИ-НЕ

|

Вход |

Выход |

|

A |

|

B |

C |

0 |

|

0 |

1 |

1 |

|

0 |

0 |

0 |

|

1 |

0 |

1 |

|

1 |

0 |

Формула схемы имеет следующий вид: C = A B

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional». Результат представлен на рисунках 5.2-5.3

соответственно.

Рисунок 5.2 – Моделирование логического элемента 2ИЛИ-НЕ в режиме

12

«Timing»

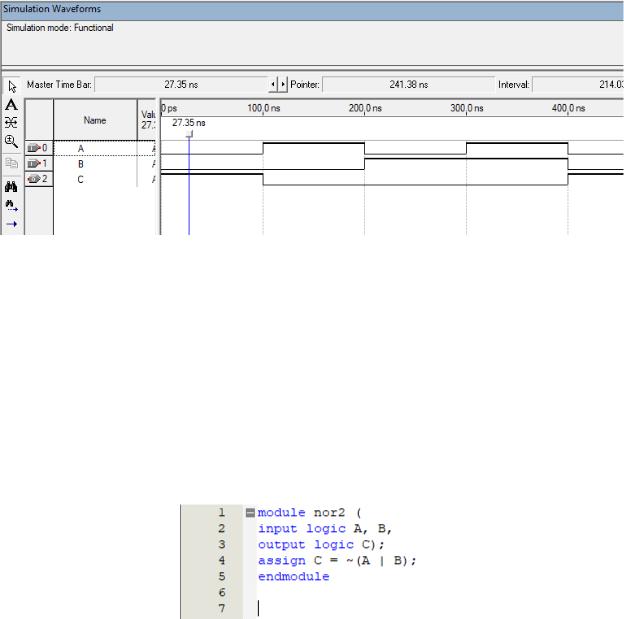

Рисунок 5.3 – Моделирование логического элемента 2ИЛИ-НЕ в режиме

«Functional»

Из-за того, что в режиме работе «Timing» учитывает задержка на логических элементах, происходят выходы за границы интервала.

Также был написан код на языке описания аппаратуры SystemVerilog,

представленный на рисунке 5.4. Во второй строчке обозначены точки входа A

и B. В третьей строчке обозначена точка выхода C. Логический элемент 2ИЛИ-

НЕ описывается четвертой строчкой после оператора «assign».

Рисунок 5.4 – Код на языке описания аппаратуры SystemVerilog логического элемента 2ИЛИ-НЕ

13

6 УСТРОЙСТВО 2искл.ИЛИ-НЕ

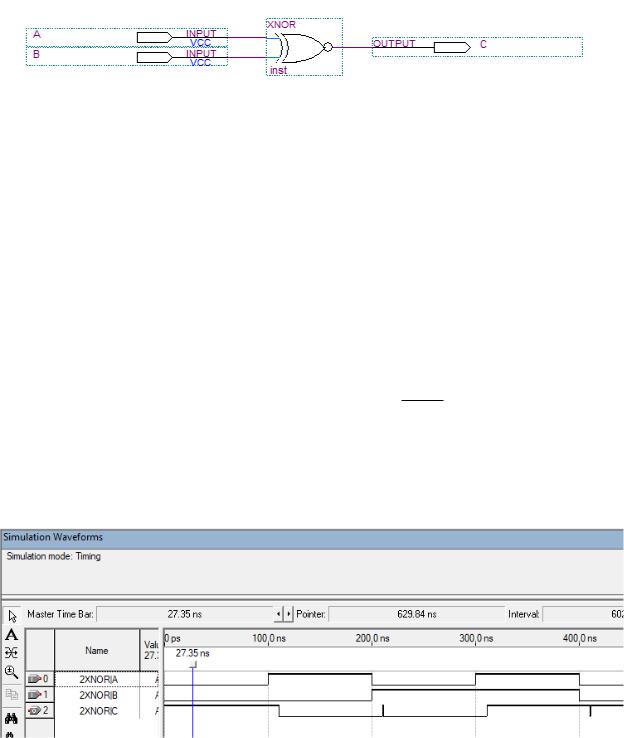

Для логического элемента 2искл.ИЛИ-НЕ была собрана функциональная схема, представленная на рисунке 6.1.

Рисунок 6.1 – Функциональная схема логического элемента 2искл.ИЛИ-НЕ Была составлена таблица истинности для логического элемента

2искл.ИЛИ-НЕ, представленная в таблице 6.1.

Таблица 6.1 - Таблица истинности для логического элемента 2искл.ИЛИ-НЕ

|

Вход |

Выход |

|

A |

|

B |

C |

0 |

|

0 |

1 |

1 |

|

0 |

0 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

Формула схемы имеет следующий вид: C = A B.

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional». Результат представлен на рисунках 6.2-6.3

соответственно.

Рисунок 6.2 – Моделирование логического элемента 2искл.ИЛИ-НЕ в режиме «Timing»

14

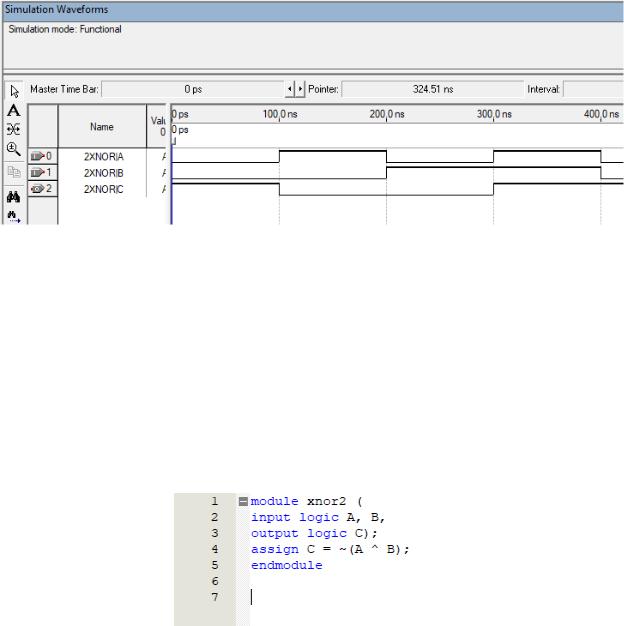

Рисунок 6.3 – Моделирование логического элемента 2искл.ИЛИ-НЕ в режиме «Functional»

Из-за того, что в режиме работе «Timing» учитывает задержка на логических элементах, происходят выходы за границы интервала.

Также был написан код на языке описания аппаратуры SystemVerilog,

представленный на рисунке 6.4. Во второй строчке обозначены точки входа A

и B. В третьей строчке обозначена точка выхода C. Логический элемент

2искл.ИЛИ-НЕ описывается четвертой строчкой после оператора «assign».

Рисунок 6.4 – Код на языке описания аппаратуры SystemVerilog логического элемента 2искл.ИЛИ-НЕ

15

7 УСТРОЙСТВО СОГЛАСНО ВАРИАНТУ 9

Функция согласно варианту №9 представлена на рисунке 7.1.

Рисунок 7.1 – Функция согласно варианту №9 Была составлена таблица истинности для данной функции,

представленная в таблице 7.1.

Таблица 7.1 - Таблица истинности для функции

|

Вход |

|

|

Выход |

|

w |

x |

|

y |

z |

F |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

1 |

1 |

0 |

|

1 |

1 |

1 |

1 |

1 |

|

0 |

0 |

0 |

1 |

1 |

|

0 |

1 |

1 |

1 |

1 |

|

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

0 |

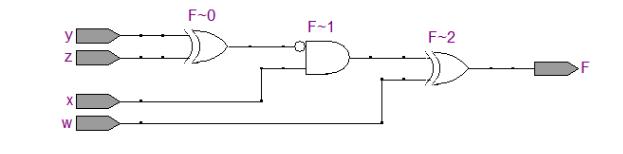

Для данной функции была собрана функциональная схема, представленная на рисунке 7.2.

Рисунок 7.2 –Составленная схема функции

16

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional». Результат представлен на рисунках 7.3-7.4

соответственно.

Рисунок 7.3 – Моделирование схемы функции в режиме «Timing»

Рисунок 7.4 – Моделирование схемы функции в режиме «Functional»

Из-за того, что в режиме работе «Timing» учитывается задержка на логических элементах, происходят выходы за границы интервала.

Также был написан код на языке описания аппаратуры SystemVerilog,

представленный на рисунке 7.5. В строчке 3 и 4 описаны порты внешнего взаимодействия: на 3 строчке четыре входа, а на 4 один выход F. Затем идет структура функции, описание которой представлено после оператора «assign».

Рисунок 7.5 – Код на языке описания аппаратуры SystemVerilog для функции

по варианту

17

Также была построена схема функции по написанному коду с помощью инструмента «RTL Viewer», представленная на рисунке 7.6

Рисунок 7.6 – Схема функции по написанному коду

18

Заключение

В результате лабораторной работы были изучены основные инструменты САПР QuartusII, приобретены навыки моделирования работы схем на основе простых логических элементов.

Были собраны логические элементы, а также смоделированы работы данных элементов. Также были описаны все элементы с помощью

SystemVerilog. Для каждого из логических элементов была составлена таблица истинности и результаты моделирования были сравнены с ней. Значения совпали.

Была собрана схема задания по варианту, а также смоделирована ее работа. Также она была описана с помощью SystemVerilog. Далее была составлена таблица истинности и результаты моделирования были сравнены с ней. Значения совпали. По описанию была собрана схема с помощью инструмента RTL Viewer.

При моделировании работы схем если запускать моделирование в режиме «Timing», то некоторые сигналы будут выходить из временного интервала. Из этого был сделан вывод, что в режиме «Timing» учитываются задержки логических элементов. Если же запускать моделирование в режиме

«Functional», таких задержек не будет, этот режим их просто исключает.

19