Министерство науки и высшего образования Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего образования

ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ (ТУСУР) Кафедра безопасности информационных систем (БИС)

КОМБИНАЦИОННЫЕ УСТРОЙСТВА

Отчет по лабораторной работе №2

по дисциплине «Электроника и схемотехника 2» Вариант №9

Студент гр. 731-2

_____________

14.05.2023

Руководитель Доцент каф. КИБЭВС, к.т.н., доцент

_________ _____________ А.Н. Мальчуков

14.05.2023

Томск 2023

|

ОГЛАВЛЕНИЕ |

|

Введение................................................................................................................... |

3 |

|

1 РЕАЛИЗАЦИЯ ЛОГИЧЕСКИХ ФУНКЦИЙ 6, 7, 8, 9 ..................................... |

5 |

|

1.1 |

Таблица истинности логических функций 6, 7, 8, 9................................... |

5 |

1.2 |

Функциональная схема.................................................................................. |

6 |

1.3 |

Моделирование функциональной схемы..................................................... |

7 |

1.4 |

Описание функциональных схем на HDL ................................................... |

8 |

2 ПРИОРИТЕТНЫЙ ШИФРАТОР 4-2 ............................................................... |

10 |

|

2.1 |

Таблица истинности приоритетного шифратора 4-2 ............................... |

10 |

2.2 |

Функциональная схема приоритетного шифратора 4-2........................... |

10 |

2.3 |

Моделирование схемы приоритетного шифратора 4-2 ........................... |

11 |

3 РЕАЛИЗАЦИЯ ЛОГИЧЕСКИХ ФУНКЦИЙ 9, 10, 11, 12 ............................. |

13 |

|

3.1 |

Таблица истинности логических функций 9, 10, 11, 12........................... |

13 |

3.2 |

Функциональная схема................................................................................ |

14 |

3.3 |

Моделирование функциональной схемы................................................... |

15 |

3.4 |

Описание функциональных схем на HDL ................................................. |

17 |

Заключение ............................................................................................................ |

20 |

|

2

Введение

Цель работы: научиться применять мультиплексоры, шифраторы и

дешифраторы.

Постановка задачи:

1. построить совмещенную таблицу, взяв из таблицы вариантов

лабораторной работы №1 4 функции, а именно свой вариант и еще три варианта на одну, две и три строки выше по таблице. Собственный вариант

̅̅̅̅̅̅̅̅̅ |

|

|

F9 = x y z w, вариант на одну строку выше F8 = x y z w, вариант |

||

на две строки выше F7 = |

̅̅̅̅̅̅̅ |

z w, вариант на три строки выше |

(x y) |

||

F6 = x y ̅̅̅̅̅̅̅̅̅̅̅.(z w)

2. собрать схему по формулам на холсте .bdf, реализовать одну на дешифраторе, одну на мультиплексоре, одну через формулы СКНФ/СДНФ, одну по формуле. Осуществить выбор результата функции согласно варианту №9, а именно с помощью lpm_mux. Промоделировать схему в двух режимах с подачей на каждую функцию две разные комбинации входных сигналов. Сверить результаты моделирования с составленной таблицей истинности в

п.1.

3. повторить пункт 2 используя HDL согласно варианту №9, а именно на

System Verilog.

4. построить совмещенную таблицу, взяв из таблицы вариантов лабораторной работы №1 4 функции, а именно свой вариант и еще три варианта на одну, две и три строки ниже по таблице. Собственный вариант

F9 = x ̅̅̅̅̅̅̅̅̅ w, вариант на одну строку ниже F10 = x y ̅̅̅̅̅̅̅̅̅̅,

y z z w

вариант на две строки ниже F11 = x ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅, вариант на три строки ниже

y z w

F12 = ̅̅̅̅̅̅̅x y z w.

5. построить таблицу истинности для приоритетного шифратора 4-2.

Составить формулы для каждого выхода и преобразовать их в базис согласно варианту №9, а именно в базис И-НЕ.

3

6.собрать схему приоритетного шифратора на холсте .bdf, согласно формулам в базисе И-НЕ, промоделировать работу схемы и сравнить полученный результат с таблицей истинности полученной в п.5. После создать символ для использования в дальнейшем.

7.собрать схему по формулам из п.4 на холсте .bdf, реализовать одну на дешифраторе, одну на мультиплексоре, одну через формулы СКНФ/СДНФ, одну по формуле. Выход схемы реализовать согласно варианту №9, а именно

сиспользованием tri_buf, а также используя символ полученный в п.6. Промоделировать схему в двух режимах с подачей на каждую функцию две разные комбинации входных сигналов. Сверить результаты моделирования с составленной таблицей истинности в п.4.

8.повторить пункты 5-7, только для описания устройств вместо схем, используя HDL согласно варианту №9, а именно на VHDL(v2).

9.написать выводы о проделанной работе.

4

1 РЕАЛИЗАЦИЯ ЛОГИЧЕСКИХ ФУНКЦИЙ 6, 7, 8, 9

1.1 Таблица истинности логических функций 6, 7, 8, 9

|

По условию задания была построена таблица истинности для функций: |

|||||||||

|

̅̅̅̅̅̅̅̅̅ |

|

|

|

|

|

̅̅̅̅̅̅̅ |

|

|

|

F9 = x y z w, F8 = x y z w, F7 = (x y) z w, F6 = x y |

||||||||||

̅̅̅̅̅̅̅̅̅̅̅ |

|

|

|

|

|

|

|

|

||

(z w), представленная в таблице 1.1. |

|

|

|

|

||||||

Таблица 1.1 – Совмещенная таблица истинности функций F9, F8, F7, F6 |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

|

Выходы |

|

||

|

|

|

|

|

|

|

|

|

|

|

w |

|

x |

|

y |

z |

|

F9 |

F8 |

F7 |

F6 |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

|

0 |

0 |

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

|

0 |

1 |

|

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

|

1 |

0 |

|

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

|

1 |

1 |

|

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

|

0 |

0 |

|

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

|

0 |

1 |

|

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

|

1 |

0 |

|

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

|

1 |

1 |

|

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

|

0 |

0 |

|

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

|

0 |

1 |

|

0 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

|

1 |

0 |

|

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

|

1 |

1 |

|

0 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

0 |

0 |

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

0 |

1 |

|

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

1 |

0 |

|

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

1 |

1 |

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

5

1.2 Функциональная схема

Функция F9 = x ̅̅̅̅̅̅̅̅̅ w реализуется с помощью дешифратора, так

y z

как в результате функции единиц меньше, чем нулей дешифратор выполнен «по единицам».

Функция F8 = x y z w реализуется с помощью мультиплексора.

Функция F7 реализуется по формуле СКНФ = (w x y z) (w x y̅ z) (w x y̅ z̅) (w x̅ y z) (w x̅ y z̅) (w x̅ y̅ z).

Функция F6 реализуется по формуле = x y ̅̅̅̅̅̅̅̅̅̅̅.

(z w)

Выбор результата функции осуществлен согласно варианту №9, а именно при помощи lpm_mux. Функциональная схема построенных устройств представлена на рисунке 1.1.

Рисунок 1.1 – Функциональная схема

6

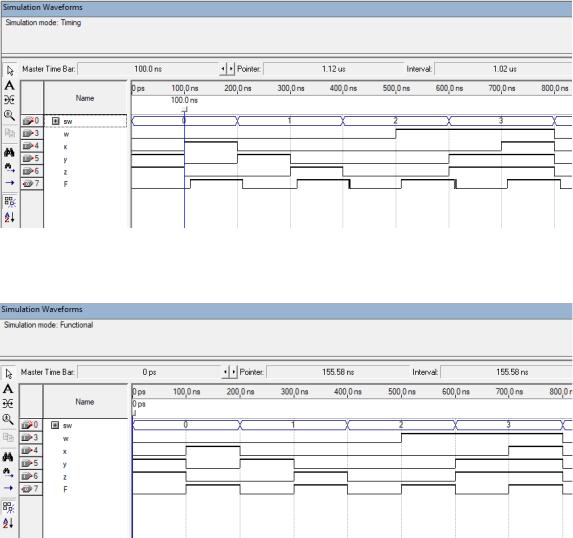

1.3 Моделирование функциональной схемы

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional». Комбинация значений w, x, y, z: для F9 –(0,0,1,1) и (0,1,0,0), F8 –(0,0,1,0) и (0,0,0,1), F7 –(0,0,0,0) и (1,0,0,0), F6 –(1,0,1,1) и (1,1,1,1). Результат представлен на рисунках 1.2 - 1.3 соответственно.

Рисунок 1.2 – Моделирование функциональной схемы в режиме «Timing»

Рисунок 1.3 – Моделирование функциональной схемы в режиме «Functional»

Из-за того, что в режиме работе «Timing» учитывается задержка на логических элементах, происходят выходы за границы интервала. Результат моделирования совпал с таблицей истинности.

7

1.4 Описание функциональных схем на HDL

Далее был составлен код описания схемы на HDL согласно варианту №9,

а именно на языке описания аппаратуры System Verilog, представленный на рисунке 1.4.

Рисунок 1.4 – Код на языке описания аппаратуры SystemVerilog

Входы и выходы описаны в строчках 2 – 4. В строчках 5 – 11

объявляются логические сигналы и описываются сами функции. В строчках

12 – 16 описывается выбор сигнала для выхода.

Для составленного кода была сформирована схема при помощи RTL Viewer, представленная на рисунке 1.5.

8

Рисунок 1.5 – Cформирована схема при помощи RTL Viewer

Также было произведено моделирование устройства, описанного при помощи System Verilog в режиме «Timing», представленное на рисунке 1.6.

Рисунок 1.6 – Моделирование устройства, описанного при помощи System Verilog в режиме «Timing»

Результат совпал с предыдущим моделированием, а также с таблицей истинности.

9

2ПРИОРИТЕТНЫЙ ШИФРАТОР 4-2

2.1Таблица истинности приоритетного шифратора 4-2

Таблица истинности приоритетного шифратора 4-2 представлена в таблице 2.1.

Таблица 2.1 – Таблица истинности приоритетного шифратора 4-2

|

Входы |

|

|

Выходы |

|

|

|

|

|

|

|

|

|

sw_in3 |

sw_in2 |

sw_in1 |

sw_in0 |

sw_out1 |

sw_out0 |

G |

|

|

|

|

|

|

|

1 |

X |

X |

X |

1 |

1 |

1 |

|

|

|

|

|

|

|

0 |

1 |

X |

X |

1 |

0 |

1 |

|

|

|

|

|

|

|

0 |

0 |

1 |

X |

0 |

1 |

1 |

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

Далее были составлены формулы для выходов - sw_out1 = sw_in3

̅̅̅̅̅̅̅̅̅ |

̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅ |

sw_in3 sw_in2; sw_out0 = sw_in3 |

sw_in3 sw_in2 sw_in1; G = sw_in4 |

sw_in3 sw_in2 sw_in1. |

|

После полученные формулы были преобразованы в базис согласно варианту №9, а именно в базис И-НЕ. Теперь формулы описаны в следующем

|

|

|

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|

|

виде: |

sw_out1 |

= |

̅̅̅̅̅̅̅̅̅ |

sw_out2 |

= |

sw_in3 sw_in2, |

|||||

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|

|

|||

̅̅̅̅̅̅̅̅̅ |

̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|

|

||

̅̅̅̅̅̅̅̅̅ |

̅̅ |

|

|

|

|

sw_in3 sw_in3 sw_in2 sw_in1 . |

|

|

|||

2.2 Функциональная схема приоритетного шифратора 4-2

Используя формулы приоритетного шифратора, преобразованные в базис И-НЕ, была составлена функциональная схема, представленная на рисунке 2.1.

10