Продолжение таблицы 2.1

|

|

Входы |

|

|

|

|

Выходы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x4 |

x3 |

x2 |

x1 |

x0 |

ST2 |

ST1 |

SP2 |

|

SP1 |

FB |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

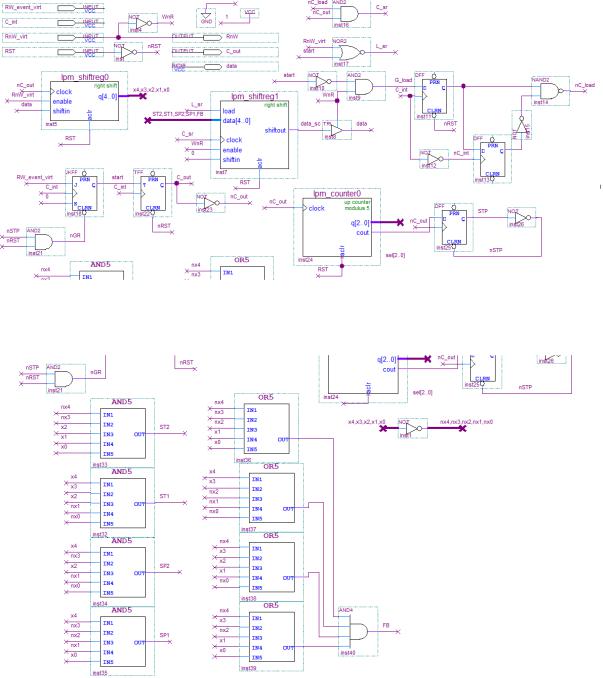

2.2 Функциональная схема

Функциональная схема реализации ведущего последовательной передачи данных младшими разрядами вперед на основе сдвигающего

регистра с асинхронным сбросом реализована с |

помощью формул |

||

СДНФ/СКНФ. Для выходов ST2, ST1, SP2, SP1 были составлены формулы |

|||

СДНФ, для выхода FB составлена формула СКНФ. x4 x3 x2 x1 x0 |

|||

|

|

̅̅̅̅ ̅̅̅̅ |

|

Формула СДНФ для выхода ST2 имеет вид: x2 x1 x0. |

|||

|

|

|

̅̅̅̅ ̅̅̅̅ |

Формула СДНФ для выхода ST1 имеет вид: x4 x3 x2 . |

|||

|

|

̅̅̅̅ |

̅̅̅̅ ̅̅̅̅ |

Формула СДНФ для выхода SP2 имеет вид: x4 x2 . |

|||

|

|

̅̅̅̅ |

̅̅̅̅ ̅̅̅̅ |

Формула СДНФ для выхода SP1 имеет вид: x4 x0. |

|||

|

|

̅̅̅̅ ̅̅̅̅ ̅̅̅̅ |

|

Формула СКНФ для выхода FB имеет вид: ( x1 x0) |

|||

̅̅̅̅ ̅̅̅̅ ̅̅̅̅ ̅̅̅̅ |

̅̅̅̅ ̅̅̅̅ |

̅̅̅̅ |

|

(x4 x3 ) ( x3 x2 x1 ) ( x3 x1 x0).

Функциональная схема построенных устройств представлена на рисунках 2.1 – 2.2.

11

Рисунок 2.1 – Первая часть функциональной схемы

Рисунок 2.2 – Вторая часть функциональной схемы

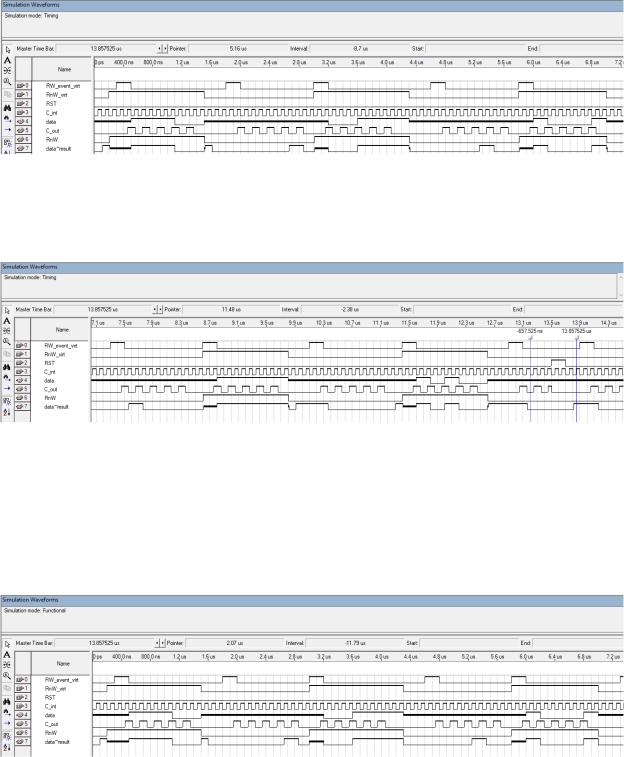

2.3 Моделирование функциональной схемы

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional». Комбинация входных значений x4, x3, x2, x1, x0 для моделирования были выбраны следующие: (1,1,1,0,0), (1,0,1,0,0), (1,1,1,1,1),

(1,0,0,0,1), (0,0,1,1,1).

12

Результат моделирования в режиме «Timing» представлен на рисунках

2.3 - 2.4.

Рисунок 2.3 – Первая часть моделирования функциональной схемы в режиме

«Timing»

Рисунок 2.4 – Вторая часть моделирования функциональной схемы в режиме

«Timing»

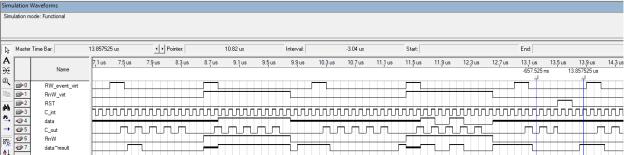

Результат моделирования в режиме «Functional» представлен на рисунках 2.5 - 2.6.

Рисунок 2.5 – Первая часть моделирования функциональной схемы в режиме

«Functional»

13

Рисунок 2.6 – Вторая часть моделирования функциональной схемы в режиме «Functional»

Из-за того, что в режиме работе «Timing» учитывается задержка на элементах, происходят выходы за границы интервала. Результат моделирования совпал со значениями из таблицы истинности.

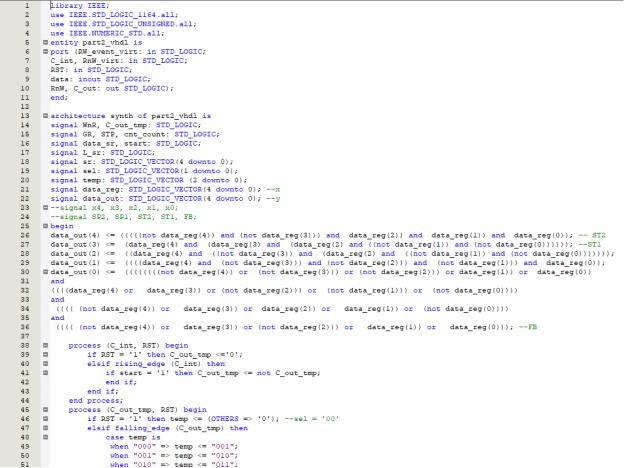

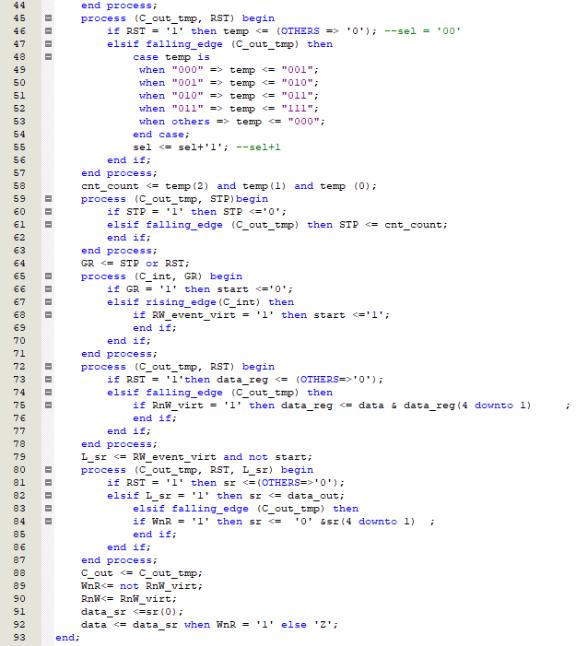

2.4 Описание функциональной схемы на HDL

Далее был составлен код описания схемы на HDL согласно варианту №9, а именно на языке описания аппаратуры VHDL. На рисунках 2.7 – 2.8

представлен код описания функциональной схемы.

14

Рисунок 2.7 – Первая часть кода функционально схемы

15

Рисунок 2.8 – Вторая часть кода функционально схемы

В строчках 6 – 10 описаны входы и выходы. В строчках 9 – 19

представлен сам код приоритетного шифратора. В строчках 14 – 22

объявляются логические сигналы. В строчках 26 – 30 описываются формулы СДНФ/СКНФ. В строчках 38 – 44 описывается формирователь синхроимпульса. В строчках 45 – 57 описывается ограниченный счетчик. В

строчках 80 – 87 описывается сдвигающий регистр. В строчках 88 – 92

описывается переприсвоение сигналов. 16

Для составленного кода была сформирована схема при помощи RTL Viewer, представленная на рисунке 2.9.

Рисунок 2.9 – Cформирована схема при помощи RTL Viewer

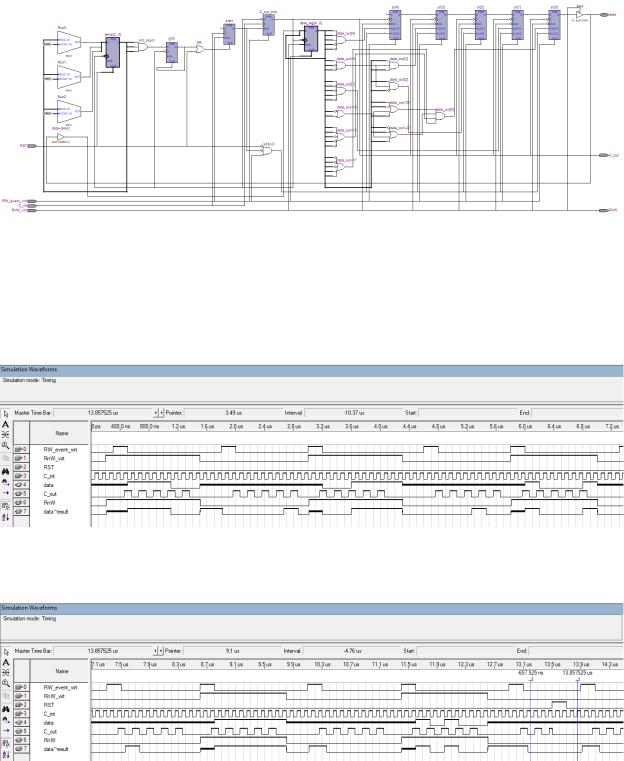

Также было произведено моделирование устройства, описанного при помощи VHDL в режиме «Timing», представленное на рисунках 2.10 – 2.11.

Рисунок 2.10 – Первая часть моделирования устройства, описанного при помощи VHDL в режиме «Timing»

Рисунок 2.11 – Вторая часть моделирования устройства, описанного при помощи VHDL в режиме «Timing»

17

Результат совпал с предыдущим моделированием, а также со

значениями из таблицы истинности.

18

Заключение

В результате лабораторной работы были приобретены навыки применения триггеров регистров и счётчиков.

Все задания выполнялись согласно варианту №9.

Были собраны схемы ведомого параллельной шины с синхронным сбросом для первой части работы, а также ведущего последовательной передачи данных младшими разрядами вперед на основе сдвигающего регистра с асинхронным сбросом для второй части работы. Для каждой части была использована таблица истинности согласно варианту, а именно таблица истинности для задачи №9. Для первой части работы, а именно при параллельной передаче данных, преобразование входных данных было выполнено с помощью дешифраторов, в то время как для второй части работы, а именно при последовательной передаче данных, преобразование входных данных было выполнено по формулам СДНФ/СКНФ.

Также были смоделированы работы данных схем. Для моделирования было выбрано 5 комбинаций входных сигналов. Результаты моделирования были сравнены с таблицей истинности. Результаты совпали.

Также были описаны схемы на языке HDL, а именно для первой части работы на SystemVerilog v2, для второй части работы на VHDL. По описанию были собраны схемы с помощью инструмента RTL Viewer.

Также были смоделированы работы данных описаний. Результаты совпали с предыдущими моделированиями, а также с таблицей истинности.

При моделировании работы схем если запускать моделирование в режиме «Timing», то некоторые сигналы будут выходить из временного интервала. Из этого был сделан вывод, что в режиме «Timing» учитываются задержки элементов схемы.

19