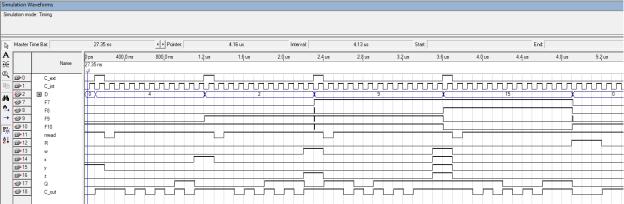

Рисунок 1.10 – Моделирование устройства, описанного при помощи System Verilog в режиме «Timing»

Результат совпал с предыдущим моделированием, а также с таблицей истинности.

11

Заключение

В результате лабораторной работы были приобретены навыки

совместного применения регистров и счётчиков.

Все задания выполнялись согласно варианту №9.

Была построена совмещенная таблица истинности для четырех функций

из лабораторной работы №1 согласно варианту №9. Таблица истинности

состояла из функций: F10 = x y ̅̅̅̅̅̅̅̅̅̅ F9 = x ̅̅̅̅̅̅̅̅̅̅ w, F8 = x y,

z w, F7 = ̅̅̅̅̅̅̅̅ z w.

( )

Были выполнены операции над полубайтом согласно варианту №9, а именно приём данных параллельным кодом, с синхронным сбросом и синхронизацией данных по нарастающему фронту и выдача данных последовательным кодом младшими разрядами вперед с синхронизацией по заднему фронту и активным уровнем сигнала «read» в 0.

Была собрана необходимая схема на холсте .bdf с использованием встроенного блока регистра согласно варианту №9, а именно lpm_dff.

Далее была промоделирована работа схемы в двух режимах, а также был проведен анализ и описаны результаты моделирования. Результаты моделирования совпали с таблицей истинности.

Далее была описана функциональная схема, используя заданный вариантом №9 HDL, а именно System Verilog. Для написанного кода была составлена схема при помощи RTL Viewer. Также была промоделирована работа кода. Результат моделирования совпал с таблицей истинности.

12