4 Семестр / Доп лаба 4 / ЭИС2 доп4лаб

.pdf

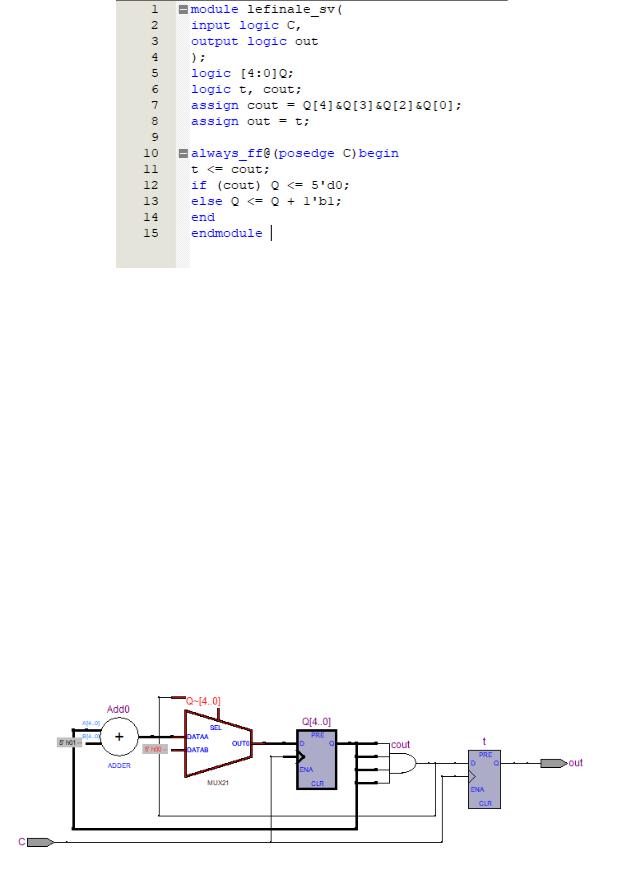

Рисунок 4.4 – Описание функциональной схемы на языке описания аппаратуры System Verilog

Входы и выходы описаны в строчках 2 – 3. В строчках 5 – 6 описываются используемые сигналы. В строчке 7 описывается рассчитанный модуль счета.

В строчках 10 - 14 описывается триггер, формирующий задержку по рассчитанному модулю счета.

4.5 Схема из RTL Viewer для кода HDL

Для составленного кода была сформирована схема при помощи RTL Viewer, представленная на рисунке 4.5.

Рисунок 4.5 – Сформированная схема при помощи RTL Viewer

21

4.6 Моделирование устройства, описанного кодом HDL

Было произведено моделирование устройства, описанного при помощи

System Verilog в режиме «Timing», представленное на рисунке 4.6.

Рисунок 4.6 – Моделирование устройства, описанного при помощи System Verilog в режиме «Timing»

Результат совпал с предыдущим моделированием, а также с расчётами.

22

Заключение

В результате лабораторной работы были изучены двоичные счётчики, их принципы построения и работы.

Все задания выполнялись согласно варианту №9.

Были составлены таблицы функционирования для схем согласно варианту №9, а именно для асинхронного вычитающего счетчика с модулем счета 25, построенного на D-триггерах, а также для синхронного суммирующего счетчика с асинхронным сбросом, с модулем счета 31, управляемого передним фронтом. Далее произведены расчеты для задачи деления частоты и организации задержки используя данные из варианта №9, а именно для задачи деления частоты выходная частота должна равняться 208333 Гц, в то время как для задачи организации задержки длительность задержки между импульсами должна равняться 0,58 мкс.

Были собраны необходимые схемы на холстах .bdf для заданных счетчиков, делителя частоты и задержки согласно варианту №9.

Далее была промоделирована работа схем в двух режимах, а также был проведен анализ и описаны результаты моделирования. Результаты моделирований совпали с таблицами истинности, а также с расчётами.

Далее были описаны функциональные схемы, используя заданный вариантом №9 HDL, а именно System Verilog. Для написанных кодов были составлены схемы при помощи RTL Viewer. Также была промоделирована работа кодов. Результат моделирований совпал с таблицами истинности и с расчётами.

23