ЦиМТ собеседование 2

.pdf

1.Параллельные порты МК51

2.Последовательный порт МК51

Имеется 4 восьмиразрядных квазидвунаправленных порта ввода/вывода Р0, Р1, Р2, Р3. (в методичке: Порт 0 является двунаправленным, а порты 1, 2 и З — квазидвунаправленными) Они обеспечивают обмен данными с внешними устройствами, каждый из портов может работать как порт общего назначения или выполнять специализированные альтернативные функции. Каждый порт имеет 8ми разрядный регистр, называемый фиксатором-защелкой.

Альтернативные функции портов.

Порт Р0:

1.Выводится младший байт адреса при работе с внешней памятью.

2.Реализуется обмен байтом данных при обращении к внеш памяти данных. Вывод младшего байта адреса и обмен байтом данных мультиплицируется во времени, млад байт адреса должен сохр во внеш регистре.

3.При программировании внутреннего ППЗУ (перепрограммируемые ПЗУ) вводятся данные(код прогр-мы).

4.При чтении содержимого внутреннего ПЗУ выводятся данные.

Порт Р1: Через Р1 задается младший байт адреса при программировании и чтении внутреннего ПЗУ. Порт Р2:

1.Выводится старший байт адреса при обращении к внешней памяти.

2.Задается старший байт адреса при программировании и чтении внутреннего ПЗУ.

Порт Р3: Каждая линия порта Р3 имеет свою альтернативную функцию. (Обозначение: Р3.0 – нулевой разряд порта Р3)

Р3.0 – RxD – вход последовательного порта, предназначен для ввода последовательного кода в приемник последовательного порта.

P3/1 – TxD – выход последовательного порта, используется для вывода данных из передачи для последовательного порта. (Р3.0 и Р3.1 – сдвиговые регистры)

Р3.2 - /INT0 (инверсия INT0) – нулевой вход внешнего запроса прерывания.

Р3.3 - /INT1 – первый вход внешнего запроса на прерывание.

Р3.4 - Т0 – счетный вход нулевого таймера счетчика (Т/С01)

Р3.5 – Т1 – счетный вход первого таймера счетчика (Т/С1). (Р3.4 и Р3.5 – счетные регистры, построены на Т-триггерах)

Р3.6 - /WR – строб чтения во внешнюю память данных, по этому сигналу байт данных записывается во внешнюю микросхему ОЗУ.

Р3.7 - /RD – строб чтения из внешней памяти данных, по этому сигналу внешняя микросхема ОЗУ выставляет содержимое запрашиваемой ячейки на ШД. Альтернативная функция любой из линий порта Р3 может быть реализована только в случае, если соответствующий разряд фиксатора-защелки записана 1

3.Память программ МК51

Все сериии МК8051 имеют гарвардскую архитектуру с раздельными адресными пространствами

Резидентная память данных представляет собой постоянное запоминающее устройство с байтовой организацией. Она доступна только для чтения и предназначена для хранения команд прикладной программы. Базовая модель МК8051 имеет емкость РПП 4 Кбайт. Область нижних адресов памяти занята векторами прерывания, которые представляют собой 8-байтовые области памяти для каждого. При запросе прерывания, автоматически передает управление на начальный адрес, соответствующего источнику вектора прерываний

4. Память данных МК51

Предназначена для хранения оперативных данных и переменных в процессе выполнения прикладной программы емкостью 128 бит. Младшие 32 байт РПД образуют подпространство регистровой памяти. Они сгруппированы в четыре банка регистров общего назначения, каждый из которых состоит из восьми регистров R0-R7. В любой момент времени программе доступен только один банк регистров, номер которого задается битами слова состояния программы

5. Стек МК 51

Стеком называется определяемая пользователем область памяти данных, запись и чтение в которую осуществляется по принципу «последним вошел – первым вышел». Восьмиразрядный регистр-указатель стека SP содержит адрес последнего байта, записанного в стек. Стек используется для передачи параметров между подпрограммами, для временного хранения переменных, хранения слова состояния во время выполнения программ обслуживания прерываний.

6. Таймер-счетчик МК51, режимы работы

Программируемые 16-битные таймеры/счетчики предназначены для подсчета внешних событий, организации программно-управляемых временных задержек и измерения временных интервалов

В состав таймеров/счетчиков входят следующие узлы:

-8-разрядный регистр режимов TMOD

-8-разрядный регистр управления/статуса TCON

-два 16-разрядных регистра таймеров/счетчиков T/C0 и T/C1

- схема управления

Режимы:

Режим 0. Таймер/счетчик представляет собой устройство на основе 13-разрядного регистра, состоящего из 8-разрядного регистра TH и пяти младших разрядов регистра TL. При работе таймера/счетчика в режиме счетчика внешних событий его содержимое увеличивается каждый раз при переключении из "1" в "0" сигнала на счетном входе микроконтроллера. При этом частота изменения сигналов на счетном входе должна быть как минимум в 2 раза ниже внешней частоты синхронизации микроконтроллера.

Режим 1. Аналогичен режиму 0, за исключением того, что в этом режиме таймер/счетчик представляет собой устройство на основе не 13-разрядного, а 16-разрядного регистра, состоящего из регистров THx и TLx. Логика работы таймера/счетчика в этом режиме полностью соответствует режиму 0

Режим 2. Таймер/счетчик представляет собой устройство на основе 8-разрядного регистра TL. При каждом переполнении регистра TL, кроме установки в регистре TCON флага TF, происходит автоматическая перезагрузка содержимого регистра TL из регистра TH. Логика работы таймера/счетчика в этом режиме также соответствует режиму 0

Режим 3. В режиме 3 T/C1 заблокирован и просто сохраняет свое состояние.

Таймер/счетчик T/C0 в режиме 3 представляет собой два независимых устройства на основе 8-разрядных регистров TH0 и TL0. Устройство на основе регистра TL0 может работать как в режиме таймера, так и в режиме счетчика внешних событий. За ним сохраняются все биты управления T/C0, оно реагирует на воздействия по входам T0 и INT0. При переполнении TL0 устанавливается флаг TF0. Устройство на основе регистра TH0 может работать только в режиме таймера. Оно использует бит включения TR1, при переполнении TH0 устанавливается флаг TF1. Установка T/C0 в режим 3 лишает T/C1 бита включения TR1. Поэтому T/C1 в режимах 0, 1, 2 при GATE1 = 0 всегда включен и при переполнении в режимах 0 и 1 T/C1 обнуляется, а в режиме 2 перезагружается, не устанавливая флаг, если IT/C0 находится в режиме 3. При работе в режимах 0, 1, 2 при переполнении T/C1 всегда вырабатывается импульс, который может использоваться для тактирования ПИ. Поэтому режим 3 для IT/C0 удобно применять тогда, когда требуется работа ПИ, тактируемого таймером/счетчиком 1, и двух таймеров/счетчиков или ПИ, таймера и счетчика.

7. Система прерываний МК51

МК51 имеет блок двухуровневого векторного прерывания от пяти источников: - два внешних прерывания INT0 и INT1, - два прерывания от таймеров/счетчиков TF0 и TF1, - прерывание последовательного порта TI или RI

Каждый источник прерывания выдает запрос на прерывание путем установки соответствующего ему флага запроса прерывания в регистре TCON или SCON

В системе прерываний МК51 предусмотрена возможность задания приоритетов прерываний, позволяющая присвоить каждому источнику прерывания один из двух уро вней приоритета – высокий или низкий. Задание приоритета для каждого источника производится с помощью регистра задания уровня приоритета IP.

Стартовавшее прерывание низкого уровня может быть прервано только высокоуровневым прерыванием, но не другим запросом прерывания низкого уровня. Стартовавшее высокоуровневое прерывание не может быть прервано никаким другим источником прерывания. Если одновременно поступают два запроса прерываний с разным приоритетом, обслуживаться будет запрос прерывания более высокого уровня. Когда одновременно поступают запросы от нескольких источников пр ерывания с одинаковым приоритетом, то используется аппаратная схема вторичного арбитража

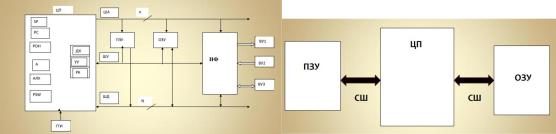

8-9. Характеристики Принстонской и Гарвардской архитектур

Архитектура МП – комплекс аппаратных и программных средств, используемых для построения МП

|

Пристонская (машина Фон-Неймана) |

|

|

Гарвардская архитектура МП |

|

|

Отличия |

|

|

1. |

Общее адресное пространство памяти – ОЗУ, ПЗУ, стек |

|

1. |

Физическое разделение ОЗУ, ПЗУ |

2. |

Общая системная шина (магистраль) |

|

2. |

Каждый вид памяти имеет свою системную магистраль |

|

|

Недостатки |

||

Последовательное обращение к памяти по одной системной магистрали |

|

Большое количество шин, фиксированный объем каждого вида памяти |

||

Вся серия МК семейства 8051 имеет гарвардскую архитектуру с раздельными адресными пространствами памяти программ и данных

10. Характеристика RISC и CISC архитектур

CISC (Complex instruction set computer – компьютер со сложным набором команд) |

RISC (Reduced instruction set computer – компьютер с уменьшенным набором команд) |

||

1. |

Большое количество команд >200 |

1. |

Ограниченное количество команд около 100 |

2. |

Разный размер команд от 1 до 6 байт |

2. |

Фиксированный размер команд до 4 байт |

3. |

Разное время выполнения команд |

3. |

Одинаковое время выполнения команд |

4. |

Количество РОНов 8-10 |

4. |

Количество РОНов 32-n100 |