Разные лабы / ЛР8_синхра_13

.docxФедеральное государственное автономное образовательное учреждение

высшего образования

«Национальный исследовательский университет

«Московский институт электронной техники»

Кафедра: Телекоммуникационные системы

Дисциплина: Синхронизация в высокоскоростных сетях передачи данных

ОТЧЕТ ПО ЛАБОРАТОРНОЙ РАБОТЕ №8

«Синхронизация методом параллельного поиска»

ВАРИАНТ №13

Москва 2021

Цель работы: Исследование принципов работы замкнутых схем синхронизации расширяющей последовательности.

Задание на лабораторную работу: Собрать модель схемы синхронизации расширяющей последовательности с параллельным поиском и протестировать ее работу.

Порядок выполнения работы

1. Собрать в среде Matlab Simulink модель цифровой системы связи с прямым расширением спектра.

2. Модель цифровой системы связи с прямым расширением спектра дополнить схемой синхронизации

3. Убедиться в корректности работы схемы в отсутствие шумов. Изменяя величину задержки, убедиться в том, что на одном из каналов демодулированный сигнал выделяется корректно с максимальной амплитудой.

4. Сделать выводы о работе схемы синхронизации расширяющей последовательности методом параллельного поиска.

Таблица 1. Вариант задания

Вариант |

Тактовая частота, кГц |

Частота следования чипов, кГц |

13 |

15 |

45 |

Выполнение.

Собрать в среде Matlab Simulink модель цифровой системы связи.

Соберём в среде Matlab Simulink модель цифровой системы связи с прямым расширением спектра (рисунок 1.1), состоящую из источника дискретных сообщений (Bernoulli Binary Generator) с тактовой частотой 15 кГц, генератора расширяющей последовательности (Repeating Sequence Stair) с частотой следования чипов 45 кГц и с двоичной последовательностью, представленной в приложении 1, и блока XOR, осуществляющего расширение спектра.

Рисунок 1.1 – Модель цифровой системы связи с прямым расширением спектра

В передатчике помимо двух генераторов представлены блок передискретизации на частоту 45 кГц×1024 = 46,08 МГц и фильтр нижних частот.

В канале связи установлена временная задержка, которая в процессе выполнения лабораторной работы будет найдена при помощи схемы синхронизации.

Приёмник состоит из фильтра нижних частот такого же, что и в передатчике, ограничителя амплитуды (ограничение от -2 до 2 В), смесителя с генератором расширяющей последовательности, фильтра нижних частот с такой частотой среза, которая будет выделять информационную частоту (чуть больше 15 кГц), и блока Sign, который преобразует полученный сигнал в последовательность 0 и 1.

Далее стоят два блока, которые посчитывают количество ошибок. Как видно из рисунка 1.1 на момент моделирования ошибок не наблюдалось, следовательно, в канале стоит слишком маленькая задержка, которая не искажает сигнал. Установим задержку больше и рассмотрим осциллограмму выходного и информационного сигналов (рисунок 1.2).

Рисунок 1.2 – Осциллограммы информационного (сверху) и выходного с приёмника (снизу) сигналов

Как видно из рисунка демодуляция происходит верно, однако наблюдается задержка.

Модель цифровой системы связи с прямым расширением спектра дополнить схемой синхронизации.

Добавим в модель цифровой системы связи с прямым расширением спектра канал со случайной задержкой (блок Variable Transport Delay) и схему синхронизации (рисунок 2.1). В качестве блоков перемножителей используем операцию XOR, производимую со сдвинутыми на целое число чипов копиями расширяющей последовательности. Для интегрирования использовать блоки Integrate and Dump с начальной задержкой, соответствующей задержке в данном подканале приема.

Рисунок 2.1 – Модель цифровой системы связи с прямым расширением спектра с каналом со случайной задержкой и схемой синхронизации

Убедиться в корректности работы схемы в отсутствие шумов. Изменяя величину задержки, убедиться в том, что на одном из каналов демодулированный сигнал выделяется корректно с максимальной амплитудой.

Схема синхронизации, представленная в предыдущем пункте, позволяет определить время задержки сигнала в канале. На рисунке 3.1 представлен результат имитационного моделирования из которого видно, что задержка составляет 3×10-5 с. Добавив данную задержку в приёмнике к М-последовательности, были получены результаты, представленные на рисунке 3.2.

Рисунок 3.1 – Осциллограммы информационного сигнала (сверху) и сигнала на выходе схемы синхронизации (снизу)

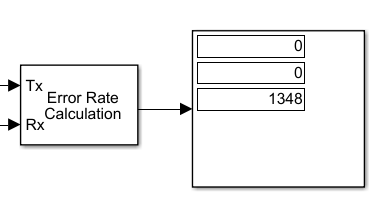

Как видно из рисунка 3.2 сигнал правильно демодулируется, а также найденная временная задержка позволяет правильно работать блокам подсчета ошибок (рисунок 3.3).

Рисунок 3.2 – Осциллограммы информационного сигнала (сверху) и выходного сигнала с приемника

Рисунок 3.3 – Дисплей после исправления временной задержки

Вывод

В данной лабораторной работе была собрана модель приемопередающего устройства с расширяющей последовательностью. Из-за временных задержек в канале возникла необходимость построения схемы синхронизации расширяющей последовательности. Данная схема была реализована методом параллельного переноса.