4 семестр / ЭиС Лаба 1

.docxМинистерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-вычислительных систем (КИБЭВС)

Логические элементы

Отчет по лабораторной работе №1

по дисциплине «Электроника и схемотехника 2»

Вариант №12

Студент гр. 711-2

_______Е. П. Толстолес

06.05.2023

Руководитель

преподаватель каф. КИБЭВС

_______ А.С. Семенов

06.05.2023

1 Введение

Цель работы – изучить основные инструменты САПР QuartusII и научиться моделировать в ней работу схем на основе простых логических элементов.

Постановка задачи.

Собрать на холсте или разных холстах .bdf и промоделировать работу схем 2И (AND), 2ИЛИ (OR), 2искл.ИЛИ (XOR), 2И-НЕ (NAND), 2ИЛИ-НЕ (NOR) и 2искл.ИЛИ-НЕ (XNOR) по аналогии с примером в методических указаниях в двух режимах.

Описать логические элементы из п.1 на HDL согласно варианту задания, в одном или разных модулях, в зависимости от того, как выполнялся п.1, и промоделировать эти схемы.

Собрать схему на отдельном холсте .bdf для выражения из таблицы согласно варианту 12.

Промоделировать её работу в двух режимах. Сделать предположение, из-за чего возникает разница в результатах моделирования разных режимов и почему.

Выполнить пп. 3-4 только с помощью HDL согласно варианту.

Составить таблицу истинности для выражения из таблицы согласно варианту 12. Сверить результаты моделирования с составленной таблицей истинности.

Написать выводы о проделанной работе.

2 Ход работы

2.1 Первоначальная настройка программы

На рисунке 2.1 показаны настройки создаваемого проекта в QuartusII.

Рисунок

2.1 – Настройки проекта

Рисунок

2.1 – Настройки проекта

На рисунке 2.2 показан графический редактор.

Рисунок

2.2 – Работа с графическим редактором

Рисунок

2.2 – Работа с графическим редактором

2.2 Работа с логическими элементами и сборка схем

Сборка схемы 2И (and) показана на рисунке 2.3.

Рисунок

2.3 – Схема 2И

Рисунок

2.3 – Схема 2И

Результаты моделирования с задержкой представлены на рисунке 2.4.

Рисунок

2.4 – Результаты моделирования с задержкой

Рисунок

2.4 – Результаты моделирования с задержкой

Результаты

моделирования без задержки представлены

на рисунке 2.5.

Результаты

моделирования без задержки представлены

на рисунке 2.5.

Рисунок 2.5 - Результаты моделирования без задержки

Код HDL описан на рисунке 2.6.

Рисунок 2.6 - HDL код 2И

Сборка схемы 2ИЛИ (or) показана на рисунке 2.7.

Рисунок

2.7 – Сборка схемы 2ИЛИ

Рисунок

2.7 – Сборка схемы 2ИЛИ

Результаты моделирования с задержкой представлены на рисунке 2.8.

Рисунок

2.8 – Результаты моделирования с задерж кой

кой

Результаты

моделирования без задержки представлены

на рисунке 2.9.

Рисунок 2.9 - Результаты моделирования без задержки

Код HDL описан на рисунке 2.10.

Рисунок 2.10 - HDL код 2ИЛИ

Сборка

схемы 2искл. ИЛИ (xor)

показана на рисунке 2.11.

Сборка

схемы 2искл. ИЛИ (xor)

показана на рисунке 2.11.

Рисунок 2.11 – Сборка схемы 2искл. ИЛИ

Результаты моделирования с задержкой представлены на рисунке 2.12.

Рисунок 2.12 - Результаты моделирования с задержкой

Результаты

моделирования без задержки представлены

на рисунке 2.13.

Результаты

моделирования без задержки представлены

на рисунке 2.13.

Рисунок 2.13 - Результаты моделирования без задержки

Код

HDL описан на рисунке 2.14.

Код

HDL описан на рисунке 2.14.

Рисунок 2.14 - HDL код 2иксл. ИЛИ

Сборка

схемы 2И-НЕ

(nand)

показана на рисунке 2.15.

Сборка

схемы 2И-НЕ

(nand)

показана на рисунке 2.15.

Рисунок 2.15 – Сборка схемы 2И-НЕ

Результаты

моделирования с задержкой представлены

на рисунке 2.16.

Результаты

моделирования с задержкой представлены

на рисунке 2.16.

Рисунок 2.16 - Результаты моделирования с задержкой

Результаты

моделирования без задержки представлены

на рисунке 2.17.

Результаты

моделирования без задержки представлены

на рисунке 2.17.

Рисунок 2.17 - Результаты моделирования без задержки

Код

HDL описан на рисунке 2.18.

Код

HDL описан на рисунке 2.18.

Рисунок 2.18 - HDL код 2И-НЕ

Сборка

схемы 2ИЛИ-НЕ (nor) показана

на рисунке 2.19.

Сборка

схемы 2ИЛИ-НЕ (nor) показана

на рисунке 2.19.

Рисунок 2.19 – Сборка схемы 2ИЛИ-НЕ

Результаты

моделирования с задержкой представлены

на рисунке 2.20.

Результаты

моделирования с задержкой представлены

на рисунке 2.20.

Рисунок 2.20 - Результаты моделирования с задержкой

Результаты

моделирования без задержки представлены

на рисунке 2.21.

Результаты

моделирования без задержки представлены

на рисунке 2.21.

Рисунок 2.21 - Результаты моделирования без задержки

Код

HDL

описан на рисунке 2.22.

Код

HDL

описан на рисунке 2.22.

Рисунок 2.22 - HDL код 2ИЛИ-НЕ

Сборка

схемы 2искл.ИЛИ-НЕ (xnor)

показана на рисунке 2.23.

Сборка

схемы 2искл.ИЛИ-НЕ (xnor)

показана на рисунке 2.23.

Рисунок 2.23 – Сборка схемы 2искл.ИЛИ-НЕ

Результаты

моделирования с задержкой представлены

на рисунке 2.24.

Результаты

моделирования с задержкой представлены

на рисунке 2.24.

Рисунок 2.24 - Результаты моделирования с задержкой

Результаты

моделирования без задержки представлены

на рисунке 2.25.

Результаты

моделирования без задержки представлены

на рисунке 2.25.

Рисунок 2.25 - Результаты моделирования без задержки

Код HDL описан на рисунке 2.26.

Рисунок 2.26 - HDL код 2искл.ИЛИ-НЕ

2.3 УСТРОЙСТВО СОГЛАСНО ВАРИАНТУ 12

Таблица

2.1 – таблица истинности для функции F

=

⊕z⊕w

⊕z⊕w

x |

y |

z |

w |

⌐(x&y) |

⌐(x&y)⊕z |

⌐(x&y)⊕z⊕w |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

Функциональная

схема варианта 12 представлена на рисунке

2.27.

Рисунок 2.27 – Функциональная схема варианта

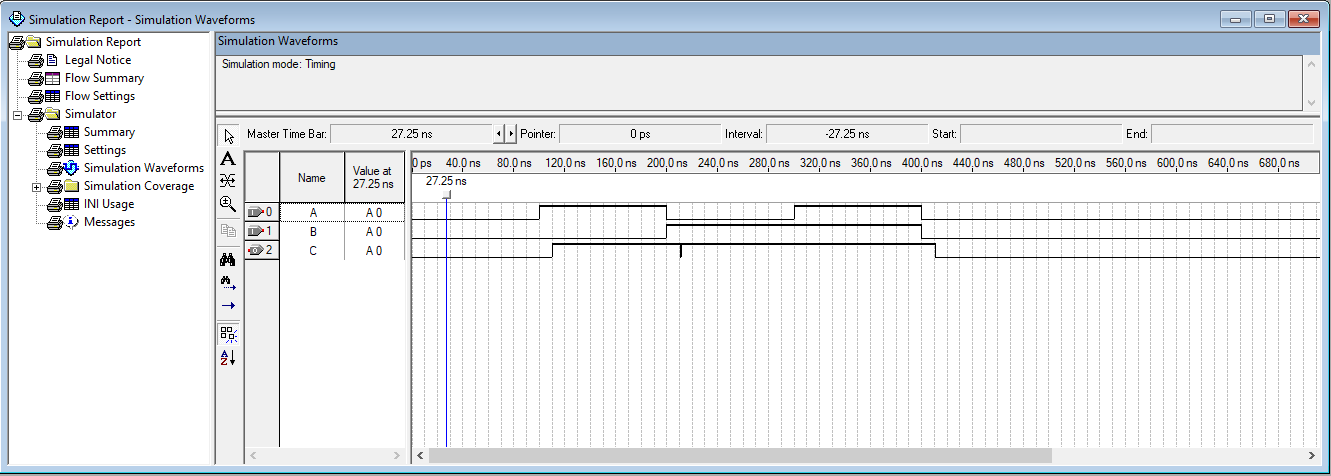

Результаты

моделирования с задержкой представлены

на рисунке 2.28.

Рисунок 2.28 - Результаты моделирования с задержкой

Результаты

моделирования без задержки представлены

на рисунке 2.29.

Рисунок 2.29 - Результаты моделирования без задержки

Код

VHDL

описан на рисунке 2.26.

Код

VHDL

описан на рисунке 2.26.

Рисунок 2.26 - HDL код для функции по варианту

3 Заключение

В результате проделанной работы были изучены основные инструменты САПР QuartusII, приобретены навыки моделирования работы схем на основе простых логических элементов.

В ходе моделирования работы схем была замечена интересная деталь, если запускать моделирование в режиме “Timing”, то некоторые сигналы будут немного выходить из временного интервала. Из этого был сделан вывод, что в режиме “Timing” учитываются задержки логических элементов. Однако, если запускать моделирование в режиме “Functional”, таких задержек не будет, этот режим их просто исключает.

Также было проведено сравнение таблиц истинностей логических элементов с их результатами моделирования, как и ожидалось, их результаты совпали.

Томск 2023