4 семестр / ЭиС Лаба 3

.docxМинистерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-вычислительных систем (КИБЭВС)

ПОСЛЕДОВАТЕЛЬНОСТНЫЕ УСТРОЙСТВА

Отчет по лабораторной работе №3

по дисциплине «Электроника и схемотехника 2»

Вариант №12

Студент гр. 711-2

_______Е. П. Толстолес

23.05.2023

Руководитель

преподаватель каф. КИБЭВС

к.т.н., доцент

_______ А.С. Семенов

23.05.2023

1 Введение

Цель работы: научиться применять триггеры, регистры и счётчики.

1. Взять таблицу истинности из задачи согласно таблице вариантов. Определить каким способом будет реализовано преобразование входных данных согласно задаче из варианта: по формулам СДНФ/СКНФ, с помощью мультиплексора или дешифратора.

2. Соберите схему на холсте .bdf согласно варианту устройства передачи данных по параллельной шине, типу сброса (см. расшифровки под таблицей вариантов, в том числе ссылки на конкретные рисунки с примерами) и выбранному способу реализации задачи.

3. Промоделировать работу схемы в двух режимах. При моделировании работы схемы необходимо подать на неё минимум 4-ре различные комбинации входные комбинации согласно таблице истинности задачи. Сделать предположение, из-за чего возникает разница в результатах моделирования разных режимов и почему.

4. Сверить результаты моделирования с таблицей истинности задачи.

5. Повторить пп. 2-4, только для описания устройств вместо схем на холстах .bdf используйте заданный вариантом HDL.

6. Определить каким способом будет теперь реализовано преобразование входных данных согласно задаче из варианта (он должен отличаться от предыдущего): по формулам СДНФ/СКНФ, с помощью мультиплексора или дешифратора.

7. Собрать схему на холсте .bdf согласно варианту устройства последовательной передачи данных, направлению передачи, типу сброса (см. расшифровки под таблицей вариантов, в том числе ссылки на конкретные рисунки с примерами) и вновь выбранному способу реализации задачи.

8. Промоделировать работу схемы в двух режимах. При моделировании работы схемы необходимо подать на неё минимум 4-ре различные комбинации входные комбинации согласно таблице истинности задачи. Сделать предположение, из-за чего возникает разница в результатах моделирования разных режимов и почему.

9. Сверить результаты моделирования с таблицей истинности задачи.

10. Повторите пп. 7-9, только для описания устройств вместо схем на холстах .bdf используйте заданный вариантом HDL.

11. Напишите выводы о проделанной работе.

2 Ход работы

2.1 Первая часть задания

Задача N12:

Разработать схему преобразователя МТК-2 кода в двоичный код. При несовпадении входного символа с таблицей установить выход FB=1.

Таблица 2.1 – Таблица истинности варианта 12.

Значение |

Входы |

Выходы |

|||||||||

Х4 |

Х3 |

Х2 |

Х1 |

Х0 |

У3 |

У2 |

У1 |

У0 |

FB |

||

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

2 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

|

3 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

4 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

|

5 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

|

6 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

|

7 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

|

8 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

9 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

|

Возврат каретки |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

|

Перевод строки |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

|

Буквы латинские |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

|

Цифры |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

|

Пробел |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

|

Буквы русские |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

|

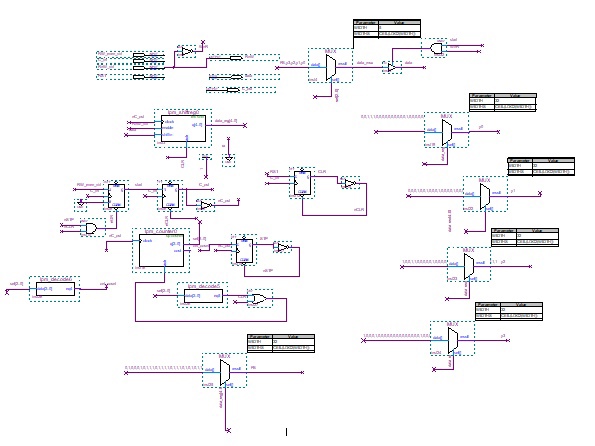

На

рисунке 2.1 представлена общая bdf

схема для таблицы истинности. На рисунках

2.2 – 2.6 представлены каждая схема по

отдельности (реализованы на декодере) .

.

Рисунок 2.1 – общая bdf схема.

Рисунок 2.2 – bdf схема для первого выхода.

Рисунок 2.3 – bdf схема второго выхода.

Рисунок 2.4 – bdf схема для третьего выхода.

Рисунок 2.5 – bdf схема четвёртого выхода.

Рисунок

2.6 – bdf

схема пятого выхода.

Рисунок

2.6 – bdf

схема пятого выхода.

На рисунках 2.7 и 2.8 представлено моделирование схем в двух режимах.

Рисунок 2.7 – Моделирование в режиме Timing.

Рисунок

2.8 – Моделирование в режиме Functional.

Рисунок

2.8 – Моделирование в режиме Functional.

На рисунке 2.9 представлено описание устройство на VHDL.

Рисунок

2.10 – Код на VHDL.

Рисунок

2.10 – Код на VHDL.

На

рисунке 2.11 представлена схема из RTL

viewer для кода на VHDL.

На

рисунке 2.11 представлена схема из RTL

viewer для кода на VHDL.

Рисунок 2.11 – RTL схема по коду VHDL.

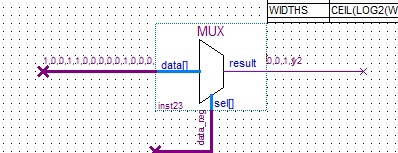

На рисунке 2.12 представлена общая bdf схема для таблицы истинности. На рисунках 2.13 – 2.17 представлены каждая схема по отдельности (реализованы на MUX).

Рисунок

2.12 – Общая bdf

схема.

Рисунок

2.12 – Общая bdf

схема.

Рисунок 2.13 – bdf схема для первого выхода.

Рисунок

2.14 – bdf

схема для второго выхода.

Рисунок

2.14 – bdf

схема для второго выхода.

Рисунок 2.15 – bdf схема для третьего выхода.

Рисунок 2.16 – bdf схема для четвёртого выхода.

Рисунок 2.17 – bdf схема для пятого выхода.

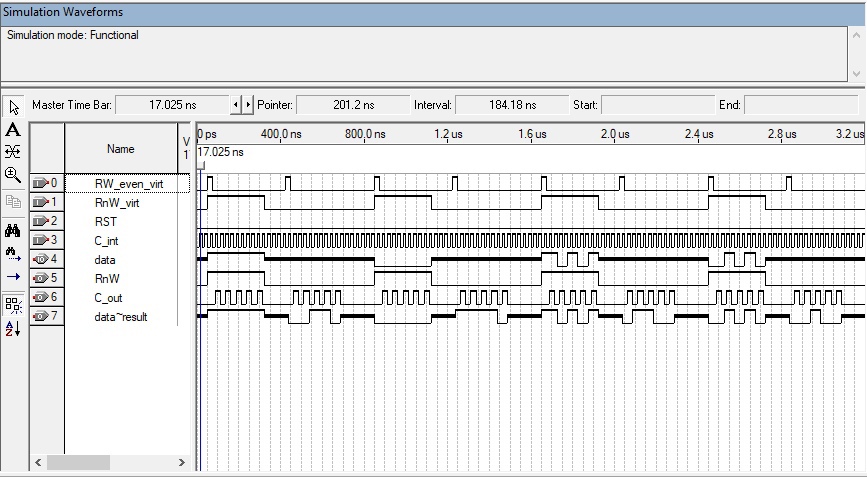

На

рисунках 2.18 и 2.19 представлено моделирование

схем в двух режимах.

На

рисунках 2.18 и 2.19 представлено моделирование

схем в двух режимах.

Рисунок 2.18 – Моделирование в режиме Timing.

Рисунок

2.19 – Моделирование в режиме Functional.

Рисунок

2.19 – Моделирование в режиме Functional.

На рисунке 2.20 представлено описание устройство на SV.

Рисунок

2.20 – Код на SV.

Рисунок

2.20 – Код на SV.

На рисунке 2.21 представлена схема из RTL viewer для кода на SV.

Рисунок

2.21 –

RTL диаграмма.

Рисунок

2.21 –

RTL диаграмма.

ЗАКЛЮЧЕНИЕ

Результаты каждого моделирования соответствуют таблице истинности

функций. Значит схемы и само моделирование были верными. Для каждой схемы составлены коды и RTL схемы.

Отчёт оформлен согласно ОС ТУСУР 2021.

Томск 2023