СхТ_ЛР_3_Цуканова_0363

.docxМИНОБРНАУКИ РОССИИ

САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ

ЭЛЕКТРОТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

«ЛЭТИ» ИМ. В.И. УЛЬЯНОВА (ЛЕНИНА)

Кафедра САПР

ОТЧЕТ

по лабораторной работе №3

по дисциплине «Схемотехника»

Тема: Шифратор и дешифратор

Студент гр. 0363 |

__________________________ |

Цуканова П.А. |

Преподаватель |

__________________________ |

Фахми Ш. С. |

Санкт-Петербург

2021

ЛАБОРАТОРНАЯ РАБОТА 3. ШИФРАТОР И ДЕШИФРАТОР

Цель работы

Спроектировать в среде разработки шифратор и дешифратор, проверить их работоспособность.

Техническое задание

Шифратор — логическая

схема, имеющая

входов

входов

и n выходов

и n выходов

.

Если на

.

Если на

-ый

вход

-ый

вход

подать 1, а на остальные входы — 0, то

выходы

подать 1, а на остальные входы — 0, то

выходы

будут кодировать число i.

будут кодировать число i.

Рисунок 1 - Схема шифратора

Дешифратор — логическая схема, имеющая

n входов

и

выходов

и

выходов

.

На все выходы подаётся 0, кроме выхода

.

На все выходы подаётся 0, кроме выхода

,

на который подаётся 1, где

— число, которое закодировано входами

.

,

на который подаётся 1, где

— число, которое закодировано входами

.

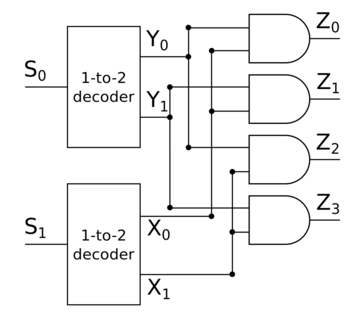

Рисунок 2 - Схема дешифратора

Теоретическая подготовка

Принцип работы шифратора заключается

в том, что выходы

кодируют один из входов

в двоичной системе счисления. Очевидно,

что если подать на несколько входов

значение 1, то такая схема будет работать

некорректно. В качестве примера рассмотрим

шифратор 4-to-2. Если

в двоичной системе счисления. Очевидно,

что если подать на несколько входов

значение 1, то такая схема будет работать

некорректно. В качестве примера рассмотрим

шифратор 4-to-2. Если

,

то

,

то

,

если же

,

если же

,

то

,

то

и

и

.

Остальные случаи разбираются аналогичным

образом.

.

Остальные случаи разбираются аналогичным

образом.

Суть дешифратора заключается в том, что с помощью n входов s0, s1, …, sn−1 можно задавать выход, на который будет подаваться 1. Для того, чтобы лучше понять, как работает дешифратор, рассмотрим в качестве примера дешифратор 2-to-4 (это значит, что у этого дешифратора есть два входа s0 и s1 и четыре выхода z0, z1, z2 и z3). Если s0=s1=0, то на выходе z0 будет значение 1, на остальных выходах будет 0. Если же s0=1, s1=0, то на выходе z1 будет 1, на остальных выходах будут 0. Если s0=0, s1=1, то на выходе z2 будет 1, а на остальных входах будет 0. Если же s0=s1=1, то на выходе z3 будет 1, а на других — 0.

Код программы:

Шифратор:

`timescale 1ns / 1ps

module encoder(a, sel);

input wire[7:0]a;

output reg[2:0]sel;

always @(a)

begin

case(a)

8'b00000001: sel=3'b000;

8'b00000010: sel=3'b001;

8'b00000100: sel=3'b010;

8'b00001000: sel=3'b011;

8'b00010000: sel=3'b100;

8'b00100000: sel=3'b101;

8'b01000000: sel=3'b110;

8'b10000000: sel=3'b111;

default: sel=3'b000;

endcase

end

endmodule

Дешифратор:

`timescale 1ns / 1ps

module decoder(a, sel);

input wire[2:0]a;

output reg[7:0]sel;

always @(a)

begin

case(a)

3'b000: sel=8'b00000001;

3'b001: sel=8'b00000010;

3'b010: sel=8'b00000100;

3'b011: sel=8'b00001000;

3'b100: sel=8'b00010000;

3'b101: sel=8'b00100000;

3'b110: sel=8'b01000000;

3'b111: sel=8'b10000000;

endcase

end

endmodule

Временная диаграмма реализации схемы

Шифратор:

Дешифратор:

Вывод

В результате выполнения лабораторной работы мы спроектировали шифратор и дешифратор в среде Quartus и проверили их работоспособность.