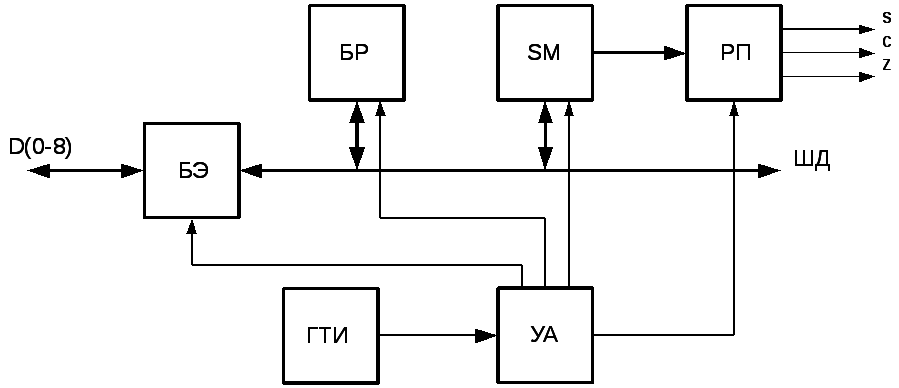

- •2.1 Описание структуры устройства

- •2.2.1 Описание работы устройства по функциональной схеме

- •2.2.2 Описание функционирования операционного блока по функциональной схеме

- •2.4 Разработка принципиальной схемы устройства

- •2.4.1 Описание функционирования управляющего автомата по принципиальной схеме

- •2.4.2 Описание функционирования операционного автомата по принципиальной схеме

- •4 Моделирование схемы устройства

- •Заключение

Российский Государственный Университет

Инновационных Технологий и Предпринимательства

Факультет«Системы защиты и безопасности»

Курсовая работа

тема:

Спецпроцессор

Выполнила студентка группы 10К2

Стензя Татьяна

Проверил преподаватель:

Долотин А.И.

Пенза, 2011

Содержание

Содержание

Введение

1 Анализ требований к устройству

2 Разработка устройства

2.1 Описание структуры устройства

2.2 Разработка функциональной схемы устройства

2.3 Выбор элементов для реализации устройства

2.4 Разработка принципиальной схемы устройства

3 Расчет периода синхросигналов

4 Моделирование схемы устройства

Заключение

Список используемой литературы

Приложение А

Введение

Введение

Вычислительная техника вместе с системами и средствами связи представляет собой техническую базу информатизации общества. Информатизация — это процесс существенного изменения роли информации в жизни общества и его хозяйственной деятельности. Превращение информационного продукта в товар приводит к глубоким изменениям в обществе. Оно трансформируется из индустриального в информационное.

В настоящее время цифровые вычислительные машины (компьютеры) применяются повсеместно, практически во всех сферах деятельности человека. Современные тенденции развития вычислительной техники — универсализация вычислительных устройств, их интеграция в системы бытовой техники, технологическое оборудование и т.п. Современный компьютер может выполнять самые различные действия, что является следствием развития технологии программного управления.

Но для создания специфических или узкоспециализированных устройств зачастую невозможно или непродуктивно использовать современные вычислительные машины. Поэтому наиболее часто, для таких целей разрабатываются специальные устройства, выполняющие некоторые, заранее определённые операции.

Целью данного курсового проекта является разработка спецпроцессора, предназначенного для выполнения заданного набора логических и арифметических микроопераций

1 Анализ требований

к устройству

1 Анализ требований

к устройству

Для реализации схемы сопроцессора необходимо наличие следующих элементов:

трех 8-разрядных регистров с синхронным входом записи информации и тремя состояниями на выходе для подключения выходов регистров к общей шине;

8-разрядного сумматора;

8-разрядного регистра с тремя состояниями на выходе, предназначенного для хранения кодов чисел, полученных с сумматора;

8-разрядные схемы OR и AND для выполнения соответствующих логических функций;

8-разрядные буферные элементы для обеспечения подключения шины данных спецпроцессора к внешней магистрали данных и подключения схем спецпроцессора к внутренней магистрали;

схема формирования признаков результата;

схема формирования сигналов управления.

2Разработка устройства

2Разработка устройства

2.1 Описание структуры устройства

Для выполнения требуемых микроопераций разрабатываемое устройство можно представить в виде совокупности следующих блоков:

- Блок регистров (БР) состоит из трех восьмиразрядных регистров с тремя состояниями на выходе. Они предназначены для записи входных кодов, поступающих с шины данных при поступлении соответствующего управляющего сигнала. Эти регистры обеспечивают хранение данных и их передачу на сумматор.

Сумматор SMпредназначен для выполнения арифметических операций.

Трехразрядный регистр признаков результата предназначен для хранения признаков s, с, z.Состояние регистра может изменяется при выполнении арифметических и логических операций.

- Буферный элемент, который предназначен для обмена данными между внешней магистралью и шиной данных спецпроцессора.

- Схема управления и синхронизации осуществляет управление работой всех других блоков устройства путем генерации соответствующих управляющих сигналов.

Как видно из вышесказанного, предлагаемое решение схемы сопроцессора предполагает выполнение всех арифметических операций в сумматоре, выполнение операций сдвига на регистрах, а выполнение логических операций на отдельных комбинационных элементах. Это несколько увеличит время выполнения микроопераций, но позволяет упростить схему и свести выполнение всех микроопераций к выполнению стандартных простейших действий. Упрощенная структурная схема спецпроцессора представлена на рисунке 1.

БЭ – буферный элемент;

ШД – шина данных;

БР – блок регистров;

SM – сумматор;

РП – регистр признаков;

УА – управляющий автомат;

ГТИ – генератор тактовых импульсов.

Рисунок 1-Схема спецпроцессора

2.2 Разработка функциональной схемы устройства

Схема электрическая функциональная устройства представлена в приложении А. Она содержит следующие основные блоки.

- Блок входных регистров БВР состоит из трех 8-разрядных регистров хранения с тремя состояниями на выходе. Входы и выходы регистров подключены к 8-разрядной шине данных (D0-D7). Причем, если регистрR3 представляет собой регистр хранения, то регистрыR1 иR2 является сдвигающими регистрами.

- 8-разрядное буферное устройство предназначено для обмена данными между шиной данных спецпроцессора и входной магистралью данных. Сумматор предназначен для выполнения арифметических операций и представляет собой комбинационную схему и регистр RSM. Регистр RSM предназначен для для хранения результата вычислений. Управляющий автомат, предназначенный для формирования сигналов управления (y), реализован на 8-разрядном двоичном счетчике и дешифраторе.

Ниже представлен список сигналов, формируемых управляющим автоматом.

y1 Разрешение работы магистрального усилителя MA1

у2 Разрешение работы магистрального усилителя MA2

у3 Выбор режима работы регистра R1

у4 Разрешение работы буферного элемента BF5

у5 Разрешение работы буферного элемента BF8

у6 Выбор режима работы регистра R2

у7 Разрешение работы буферного элемента BF6

у8 Разрешение работы буферного элемента BF7

у9 Считывание содержимого R3

у10 Разрешение работы буферного элемента BF1

у11 Разрешение работы буферного элемента BF2

у12 Разрешение работы буферного элемента BF3

у13Формирование бита переноса сумматора

у14 Разрешение работы буферного элемента BF4

у15 Выбор режима работы регистра RSM

у16 Разрешение работы буферного элемента BF9

у17 Запись данных в регистр R1

у18 Запись данных в регистр

R2

у19 Запись данных в регистр R3

у20 Запись данных в регистры RSM и PSW

у21Сброс триггера пуска