часть 1 № 15-18

.doc№15

В позиционных системах счисления один и тот же числовой знак (цифра) в записи числа имеет различные значения в зависимости от того места (разряда), где он расположен. Изобретение позиционной нумерации, основанной на поместном значении цифр, приписывается шумерам и вавилонянам; развита была такая нумерация индусами и имела неоценимые последствия в истории человеческой цивилизации. К числу таких систем относится современная десятичная система счисления, возникновение которой связано со счётом на пальцах. В средневековой Европе она появилась через итальянских купцов, в свою очередь заимствовавших её у мусульман.

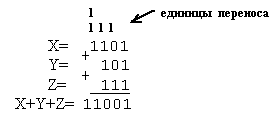

Под

позиционной системой счисления обычно

понимается b-ричная

система счисления, которая определяется

целым

числом

![]() ,

называемым основанием

системы счисления. Целое число x

в b-ричной

системе счисления представляется в

виде конечной линейной

комбинации

степеней числа b:

,

называемым основанием

системы счисления. Целое число x

в b-ричной

системе счисления представляется в

виде конечной линейной

комбинации

степеней числа b:

,

где

,

где

![]() —

это целые числа, называемые цифрами,

удовлетворяющие неравенству

—

это целые числа, называемые цифрами,

удовлетворяющие неравенству

![]() .

.

Каждая

степень

![]() в

такой записи называется весовым

коэффициентом разряда.

Старшинство разрядов и соответствующих

им цифр определяется значением показателя

k

(номером разряда). Обычно для ненулевого

числа x

требуют, чтобы старшая цифра

в

такой записи называется весовым

коэффициентом разряда.

Старшинство разрядов и соответствующих

им цифр определяется значением показателя

k

(номером разряда). Обычно для ненулевого

числа x

требуют, чтобы старшая цифра

![]() в

его b-ричном

представлении была также ненулевой.

в

его b-ричном

представлении была также ненулевой.

Если не возникает разночтений (например, когда все цифры представляются в виде уникальных письменных знаков), число x записывают в виде последовательности его b-ричных цифр, перечисляемых по убыванию старшинства разрядов слева направо:

![]()

Например, число сто три представляется в десятичной системе счисления в виде:

![]()

Наиболее употребляемыми в настоящее время позиционными системами являются:

-

1 — единичная[1] (счёт на пальцах, зарубки, узелки «на память» и др.);

-

2 — двоичная (в дискретной математике, информатике, программировании);

-

3 — троичная;

-

8 — восьмеричная;

-

10 — десятичная (используется повсеместно);

-

12 — двенадцатеричная (счёт дюжинами);

-

16 — шестнадцатеричная (используется в программировании, информатике);

-

60 — шестидесятеричная (единицы измерения времени, измерение углов и, в частности, координат, долготы и широты).

При цифровом кодировании дискретной информации используются два вида кодов:

а) потенциальные коды, когда для представления информационных единиц и нулей применяется только значение потенциала сигнала, а его перепады во внимание не принимаются;

б) импульсные коды, когда двоичные данные представляются либо импульсами определенной полярности, либо перепадами потенциала определенного направления.

К способам цифрового кодирования дискретной информации при использовании прямоугольных импульсов для представления двоичных сигналов предъявляются такие требования:

- обеспечение синхронизации между передатчиком и приемником;

- обеспечение наименьшей ширины спектра результирующего сигнала при одной и той же битовой скорости (так как более узкий спектр сигналов позволяет на линии с одной и той же полосой пропускания добиваться более высокой скорости передачи данных);

- возможность распознавания ошибок в передаваемых данных;

- относительно низкая стоимость реализации.

Средствами физического уровня осуществляется только распознавание искаженных данных (обнаружение ошибок), что позволяет экономить время, так как приемник, не ожидая полного помещения принимаемого кадра в буфер, сразу его отбраковывает при распознавании ошибочных битов в кадре. Более сложная операция – коррекция искаженных данных – выполняется протоколами более высокого уровня: канального, сетевого, транспортного или прикладного.

Правила выполнения арифметических действий над двоичными числами задаются таблицами двоичных сложения, вычитания и умножения.

|

Таблица двоичного сложения |

Таблица двоичного вычитания |

Таблица двоичного умножения |

|

0+0=0 0+1=1 1+0=1 1+1=10 |

0-0=0 1-0=1 1-1=0 10-1=1 |

0 |

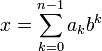

При сложении двоичных чисел в каждом разряде производится сложение цифр слагаемых и переноса из соседнего младшего разряда, если он имеется. При этом необходимо учитывать, что 1+1 дают нуль в данном разряде и единицу переноса в следующий.

Пример. Выполнить сложение двоичных чисел: а) X=1101, Y=101;

Результат 1101+101=10010.

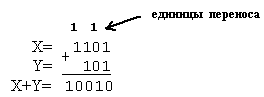

б) X=1101, Y=101, Z=111;

Результат 1101+101+111=11001.

При вычитании двоичных чисел в данном разряде при необходимости занимается 1 из старшего разряда. Эта занимаемая 1 равна двум 1 данного разряда.

Пример. Заданы двоичные числа X=10010 и Y=101. Вычислить X-Y.

Результат 10010 - 101=1101.

Умножение двоичных чисел производится по тем же правилам, что и для десятичных с помощью таблиц двоичного умножения и сложения.

Пример.

1001![]() 101=?

101=?

Результат

1001![]() 101=101101.

101=101101.

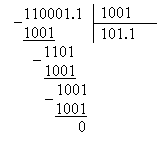

Деление двоичных чисел производится по тем же правилам, что и для десятичных. При этом используются таблицы двоичного умножения и вычитания.

Пример. 1100.011 : 10.01=?

Результат 1100.011 : 10.01=101.1.

Из аксиом видно, что наименьшим элементом является 0, наибольшим является 1, а дополнение ¬a любого элемента a однозначно определено. Для всех a и b из A верны также следующие равенства:

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

дополнение 0 есть 1 и наоборот |

|

|

|

законы де Моргана |

|

|

|

инволютивность отрицания |

[править] Основные тождества

В данном разделе повторяются свойства и аксиомы, описанные выше с добавлением ещё нескольких.

Сводная таблица свойств и аксиом, описанных выше:

|

|

|

1 коммутативность переместительность |

|

|

|

2 ассоциативность сочетательность |

|

3.1 конъюнкция

относительно дизъюнкции

|

3.2 дизъюнкция

относительно конъюнкции

|

3 дистрибутивность распределительность |

|

|

|

4 комплементность дополнительность (свойства отрицаний) |

|

|

|

5 законы де Моргана |

|

|

|

6 законы поглощения |

|

|

|

7 Блейка-Порецкого |

|

|

|

8 Идемпотентность |

|

|

|

9 инволютивность отрицания |

|

|

|

10 свойства констант |

|

|

|

|

|

дополнение 0 есть 1

|

дополнение 1 есть 0

|

|

|

|

|

11 Склеивание |

№16

Аналогично механическим ключам (рубильникам), естественно характеризовать электронный ключ сопротивлением в открытом и закрытом состоянии, предельными значениями коммутируемого тока и напряжения, временными параметрами, описывающими скорость переключения из одного состояния в другое. Следует отметить, что электронные ключи, в отличие от механических, чаще всего не являются двунаправленными, т.е. коммутируют ток и напряжение одного знака.

Следует различать аналоговые электронные ключи, предназначенные для передачи аналогового сигнала с минимальными искажениями, и цифровые ключи, обеспечивающие формирование бинарных сигналов. Аналоговые ключи лежат в основе всевозможных коммутаторов сигналов, нашедших широкое применение в технике аналого-цифрового преобразования. Несмотря на сходство в функциональном плане между цифровыми и аналоговыми ключами, требования к последним существенно отличаются от требований к цифровым ключам, что приводит совершенно к другим соображениям, по которым следует разрабатывать аналоговые ключи.

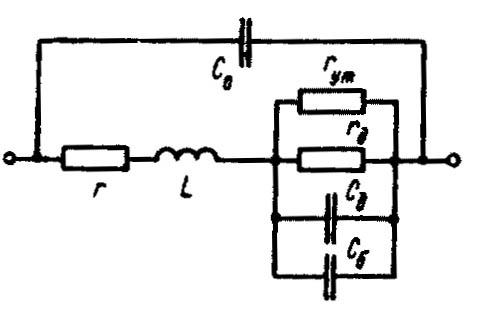

Эквивалентная схема диода представлена на рис.1. Инерционность ключа определяется процессами накопления неосновных носителей в области p-n перехода, емкостью p-n перехода, емкостью между выводами и индуктивностью выводов. Основным справочным параметром, определяющим быстродействие диода, является время восстановления обратного сопротивления.

|

|

rуm - сопротивление утечки; С0 - емкость между выводами диода; L - индуктивность выводов; СД - диффузионная емкость p-n перехода при прямом смещении; СБ - барьерная емкость p-n перехода при обратном смещении |

|

Рисунок 1 -Эквивалентная схема диода |

|

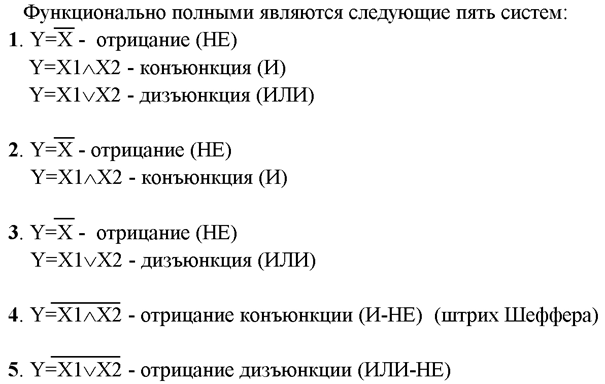

В теории цифровых устройств комбинационной логикой (комбинационной схемой) называют логику функционирования устройств комбинационного типа. У комбинационных устройств состояние выхода однозначно определяется набором входных сигналов. Это отличает комбинационную логику от секвенциальной логики, в рамках которой выходное значение зависит не только от текущего входного воздействия, но и от предыстории функционирования цифрового устройства. Другими словами, секвенциальная логика предполагает наличие памяти, которая в комбинационной логике не предусмотрена. Комбинационная логика используется в вычислительных цепях для формирования входных сигналов и для подготовки данных, которые подлежат сохранению. На практике вычислительные устройства обычно сочетают комбинационную и секвенциальную логику. Например, компьютерное Арифметическое Логическое Устройство (АЛУ) для математических вычислений содержит комбинационные узлы. Математику комбинационной логики обеспечивает Булева алгебра. Базовыми операциями являются: конъюнкция , дизъюнкция и отрицание (инверсия) или . В комбинационных схемах используются логические элементы: конъюнктор (И), дизъюнктор (ИЛИ), инвертор (НЕ), а также производные элементы: И-НЕ, ИЛИ-НЕ и «Равнозначность». Наиболее известные комбинационные устройства — этосумматор, полусумматор, шифратор, дешифратор, мультиплексор и демультиплексор

№17

Последовательностные устройства – это устройства с памятью. В них выходной сигнал определяется не только текущим состоянием входа, но и рядом предыдущих значений. Простейшее последовательностное устройство – это триггер. Его особенностью является способность бесконечно долго находится в одном из двух устойчивых состояний. Приняв одно состояние за ноль, другое за единицу, можно считать, что триггер хранит один бит информации.

Триггеры

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений). Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

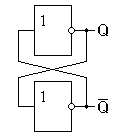

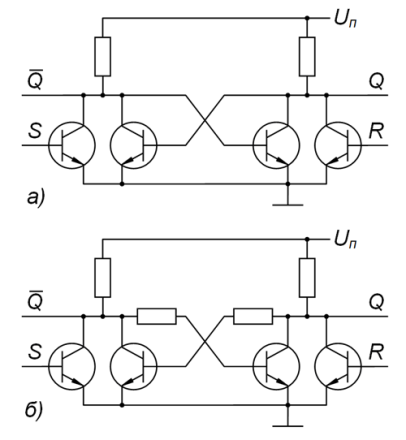

Простейшая схема, позволяющая запоминать двоичную информацию, может быть построена на двух инверторах, охваченных положительной обратной связью. Эта схема приведена на рисунке 1.

Рисунок 1. Схема простейшего триггера, построенного на инверторах.

В этой схеме может быть только два состояния - на выходе Q присутствует логическая единица и на выходе Q присутствует логический ноль. Если логическая единица присутствует на выходе Q, то на инверсном выходе будет присутствовать логический ноль, который после очередного инвертирования подтверждает уровень логической единицы на выходе Q. И наоборот, если на выходе Q присутствует логический ноль, то на инверсном выходе будет присутствовать логическая единица.

Такая ситуация будет сохраняться до тех пор пока включено питание. Но вот вопрос - а как записывать в такой триггер информацию? Нам потребуются входы записи нуля и записи единицы.

Триггеры подразделяются на две большие группы — динамические и статические. Названы они так по способу представления выходной информации.

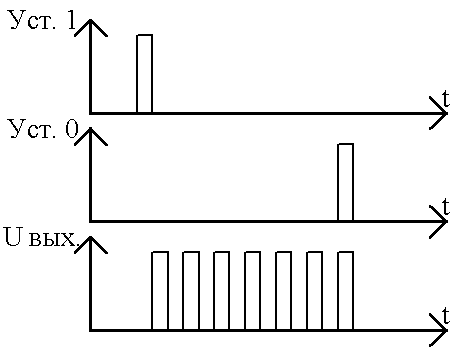

Динамический триггер представляет собой управляемый генератор, одно из состояний которого (единичное) характеризуется наличием на выходе непрерывной последовательности импульсов определённой частоты, а другое (нулевое) — отсутствием выходных импульсов. Смена состояний производится внешними импульсами (рис. 3). Динамические триггеры в настоящее время используются редко.

К статическим триггерам относят устройства, каждое состояние которых характеризуется неизменными уровнями выходного напряжения (выходными потенциалами): высоким — близким к напряжению питания и низким — около нуля. Статические триггеры по способу представления выходной информации часто называют потенциальными.

Статические (потенциальные) триггеры, в свою очередь, подразделяются на две неравные по практическому значению группы — симметричные и несимметричные триггеры. Оба класса реализуются на двухкаскадном двухинверторном усилителе с положительной обратной связью, а названием своим они обязаны способам организации внутренних электрических связей между элементами схемы.

Симметричные триггеры отличает симметрия схемы и по структуре, и по параметрам элементов обоих плеч. Для несимметричных триггеров характерна неидентичность параметров элементов отдельных каскадов, а также и связей между ними.

Симметричные статические триггеры составляют основную массу триггеров, используемых в современной радиоэлектронной аппаратуре. Схемы симметричных триггеров в простейшей реализации (2х2ИЛИНЕ) показаны на рис. 4.

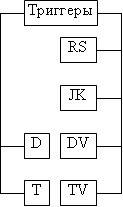

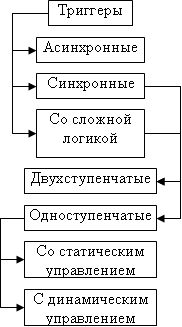

Основной и наиболее общий классификационный признак — функциональный — позволяет систематизировать статические симметричные триггеры по способу организации логических связей между входами и выходами триггера в определённые дискретные моменты времени до и после появления входных сигналов. По этой классификации триггеры характеризуются числом логических входов и их функциональным назначением (рис. 5).

Вторая классификационная схема, независимая от функциональной, характеризует триггеры по способу ввода информации и оценивает их по времени обновления выходной информации относительно момента смены информации на входах (рис. 6).

Каждая из систем классификации характеризует триггеры по разным показателям и поэтому дополняет одна другую. К примеру, триггеры RS-типа могут быть в синхронном и асинхронном исполнении.

Асинхронный триггер изменяет своё состояние непосредственно в момент появления соответствующего информационного сигнала(ов), с некоторой задержкой равной сумме задержек на элементах составляющих данный триггер.

Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на так называемом входе синхронизации С (от англ. clock). Этот вход также обозначают термином «такт». Такие информационные сигналы называют синхронными. Синхронные триггеры в свою очередь подразделяют на триггеры со статическим и с динамическим управлением по входу синхронизации С.

Триггеры со статическим управлением воспринимают информационные сигналы при подаче на вход С логической единицы (прямой вход) или логического нуля (инверсный вход).

Триггеры с динамическим управлением воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход). Также встречается название «триггер управляемый фронтом».

Одноступенчатые триггеры (latch, защёлки) состоят из одной ступени представляющей собой элемент памяти и схему управления, бывают, как правило, со статическим управлением. Одноступенчатые триггеры с динамическим управлением применяются в первой ступени двухступенчатых триггеров с динамическим управлением. Одноступенчатый триггер на УГО обозначают одной буквой - Т.

Двухступенчатые триггеры (flip-flop, шлёпающие) делятся на триггеры со статическим управлением и триггеры с динамическим управлением. При одном уровне сигнала на входе С информация, в соответствии с логикой работы триггера, записывается в первую ступень (вторая ступень заблокирована для записи). При другом уровне этого сигнала происходит копирование состояния первой ступени во вторую (первая ступень заблокирована для записи), выходной сигнал появляется в этот момент времени с задержкой равной задержке срабатывания ступени. Обычно двухступенчатые триггеры применяются в схемах, где логические функции входов триггера зависят от его выходов, во избежание временны́х гонок. Двухступенчатый триггер на УГО обозначают двумя буквами - ТТ.

Триггеры со сложной логикой бывают также одно- и двухступенчатые. В этих триггерах наряду с синхронными сигналами присутствуют и асинхронные. Такой триггер изображён на рис. 1, верхний (S) и нижний (R) входные сигналы являются асинхронными.

Триггерные схемы классифицируют также по следующим признакам:

-

числу целочисленных устойчивых состояний (основанию системы счисления) (обычно устойчивых состояний два, реже — больше, см. двоичный триггер, троичный триггер, четверичный триггер[8], …, десятичный триггер, …, n-ичный триггер, …);

-

числу уровней — два уровня (высокий, низкий) в двухуровневых элементах, три уровня (положительный, ноль, отрицательный) в трёхуровневых элементах[9], …, N-уровней в N-уровневых элементах, … ;

-

по способу реакции на помехи — прозрачные и непрозрачные. Непрозрачные, в свою очередь, делятся на проницаемые и непроницаемые.

-

по составу логических элементов (триггеры на элементах И-НЕ, ИЛИ-НЕ и др.).

№18

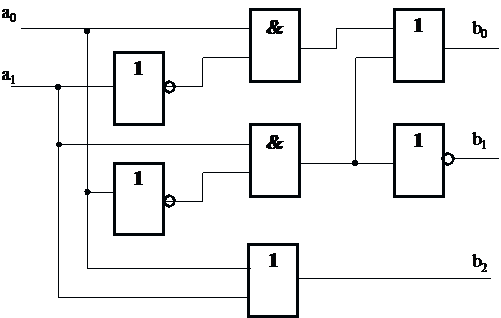

Под преобразованием кодов понимается преобразование n-разрядных двоичных чисел, представляющих информацию в одном заданном коде, в m-разрядные двоичные числа, представляющие эту информацию в другом коде. Наиболее распространены следующие два подхода к построению преобразователей кодов.

Первый подход - синтез m независимых одновыходных функций по заданной таблице истинности – таблице соответствия кодов.

Допустим, имеется таблица истинности преобразователя 2-х разрядного двоичного кода в 3-х разрядный:

|

a1 |

a0 |

|

b2 |

b1 |

b0 |

|

0 |

0 |

|

1 |

0 |

0 |

|

0 |

1 |

|

0 |

0 |

1 |

|

1 |

0 |

|

0 |

1 |

1 |

|

1 |

1 |

|

0 |

0 |

0 |

Считая b0, b1 и b2 независимыми одновыходными функциями, запишем для каждой из них булевые выражения.

b0 = `a1 a0 + a1`a0 ,

b1 = a1`a0 ,

b2 =`a1`a0 .

Используя приведенные булевы выражения с учетом того, что инверсии некоторых переменных и произведение a1`a0 встречаются не в одной функции, составляем схему преобразователя с применением (где это возможно) одних и тех же логических элементов:

Второй подход - построение преобразователя кодов по методу "дешифратор-шифратор".

В этом случае по заданной таблице истинности составляется таблица соответствия десятичных цифр. В рассмотренном примере эта таблица запишется следующим образом

|

A |

B |

|

0 |

4 |

|

1 |

1 |

|

2 |

3 |

|

3 |

0 |

Метод построения преобразователя заключается в следующем.

Сначала строится схема преобразователя двоичного кода в унарный, т.е. такой код, когда "1" может быть только на одном из N выходов преобразователя, номер которого совпадает с числом, представленным входным двоичным кодом. (такой преобразователь называется дешифратором). Число выходов дешифратора равно N = 2n , где n – число разрядов входного кода дешифратора.

Затем строится схема преобразователя, осуществляющего обратную операцию, т.е. преобразование унарного кода в двоичный. Число входов такого преобразователя, который называется шифратором, равно M = 2m , где m – число разрядов выходного кода шифратора.

В зависимости от формы представления информации различают сумматоры аналоговые и цифровые.[1]

По способу реализации

-

механические

-

электромеханические

-

электронные

-

пневматические

По архитектуре

-

четвертьсумматоры — бинарные (двухоперандные) сумматоры по модулю без разряда переноса, характеризующиеся наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на котором реализуется их арифметическая сумма по модулю;[5][неавторитетный источник?][6][неавторитетный источник?]

-

полусумматоры — бинарные (двухоперандные) сумматоры по модулю с разрядом переноса, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма по модулю в данном разряде, а на другом — перенос в следующий (старший разряд);

-

полные сумматоры — тринарные (трёхоперандные) сумматоры по модулю с разрядом переноса, характеризующиеся наличием трёх входов, на которые подаются одноимённые разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма по модулю в данном разряде, а на другом — перенос в следующий (более старший разряд). Такие сумматоры изначально ориентированы только на показательные позиционные системы счисления.[источник не указан 464 дня]