- •Достоинства и недостатки динамической памяти.

- •50. Однотранзисторная ячейка флэш-памяти

- •51. Устройство памяти с nor

- •52. Устройство памяти с nand

- •57. Разделы жесткого диска

- •Виды разделов Первичный (основной) раздел

- •Расширенный (дополнительный) раздел

- •58. Устройство лазерного принтера и принцип работы

- •59. Принцип работы манипулятора «мышь»

- •60.Принцип работы струйного принтера

- •61.Принцип работы ж/к монитора

- •62.Классификация программного обеспечения эвм

- •63.Операционные системы

- •64.Классификации и функции ос

- •65.Системы программирования

- •66. Юридическая классификация программного обеспечения эвм

- •68. Классификации вирусов

- •69. Файловые и загрузочные вирусы

- •70. Макровирусы и сетевые вирусы

- •71. Стелс вирусы и Полиморфные вирусы

- •72. Троянские программы и руткиты

Информатика как наука.Информатика-наука, изучающая закономерности получения, хранении, передачи и обработки информации. Направление информатики: а). Архитектура вычислительных систем(вычисление комплексное, каналы связи между комплексами); б). Интерфейс: программный, аппаратный(различные компоненты, взаимосвязанные друг с другом);в). Программирование(разработка приемов, средств и методов разработки программ(алгоритмические языки, средства разработки программ)). Программы: редакторы(используются для набора программы), трансляторы(используются для преобразования программы, написанной на алгоритмическом языке последовательности команд, процесса), редакторы связей(устанавливают связь между модулями программы и формируют файл).г). Решение научно-технических задач; д). Разработка приемов и методов преобразования данных без их искажения(сохраняя их постоянности); е). Защита информации(разработка приемов и методов защиты информации(разработка алгоритмов шифрования данных, средств ограниченного доступа к данным, средств с несанкционированным доступом к данным));ж). Автоматизация(разработка приемов и методов функционирования программно-аппаратных средств участия человека);з). Стандартизация(обеспечение совместимости между форматами предоставлениями данных, относящихся к различными типам вычислительных систем).

Понятие информации и её диалектическое единство с данными. Информация- продукт взаимодействия данных и адекватных методов их обработки. Информация- сообщение, которое передается и представляет из себя сведенья, отображающие свойства того или иного объекта(предмета).Диалектическое единство с данными: а). динамический характер информации меняется в момент взаимодействия данных и методов их обработки. Если взаимодействия нет, информация хранится в качестве данных. Информационный процесс- промежуток времени обработки данных, он связан с функционированием информационной системы. Источник информации

Передатчик

Передатчик Канал связи

Канал связи Приемник

Приемник Получатель

информации. Данные

объективные, методы

субъективны, т.е.

свойство информации,

объединенное взаимодействие

объективного и субъективного.

Получатель

информации. Данные

объективные, методы

субъективны, т.е.

свойство информации,

объединенное взаимодействие

объективного и субъективного.Свойства информации и её измерение. Свойства: 1). Объективности; 2). Адекватность(правильное отражение сути); 3). Полнота(достаточность данных для принятия правильного решения).4). Доступность(доступность данных и метолов обработки); 5). Актуальность(информация должна соответствовать моменту времени).Информация-уменьшение неопределенности об объекте.Бит- наименьшая мера информации(1 Бит содержит информацию о том, что произошло одно из двух событий «Да» или «Нет»). 1 байт-8 бит. 1Кбайт-1024 бит. 1 Мб-1024 Кб. 1 ГБ-1024 Мб. 1ТБ-1024 ГБ.

Понятие данных и их носителей. Данные- зарегистрированные сигналы. Носители данных: 1). Бумага; 2). Магнитная лента; 3). Магнитные диски(винчестеры). Данные характеризуются: 1). Разрешающая способность(определяется плотностью данных);2). Динамический диапазон(определяет отношение); 3). Скорость ранзакции(определяет скорость чтения(записи)). Чтобы носитель сохранял данные, скорость должна быть равна скорости информации. Доступ к данным: последовательный и прямой. Последовательный- через все предыдущие к нужному месту. Носители данных определяют полноту, достоверность и доступность информации.

Операции с данными. Обработка данных включает в себя: 1). Сбор данных(накопление информации для обеспечения ее полноты); 2). Формализация данных(приведение данных к одной форме для сопоставления их между собой позволяет повысить их доступность). 3). Фильтрация(позволяет из многообразия данных выбрать необходимые для принятия определенного решения, позволяет повысить адекватность информации); 4). Сортировка(их упорядочивание по определенному признаку позволяет повысить доступность информации); 5). Защита(комплекс мер, направленных на предотвращение утраты и модификацию данных, позволяет повысить достоверность информации); 6). Транспортировка( перевод данных из одной формы в другую, может произойти их потеря или искажение).

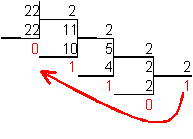

Кодирование числовых и символических данных. Символьные данные обычно хранятся на носителях информации, хранятся в виде значений целых чисел. Эти значения определяют их в системах кодировки. Кодировки: 1). ASCII-коды-1 байтовая кодировка, которая была введена наtxt, например, на начальном этапе развития техники; 2). 125i- кодировка используется вMicrosoftдо128 знаков какASCII, после128 знаков не совпадает; 3).UNICODE- современная система кодировки2х байтовая, которая позволяет хранить коды65506 символов. Не совместима с предыдущими. Целочисленные данные хранятся в ЭВМ в виде дополнительного кода, для их реализации используется двоичная система счисления. Дополнительный код образуется из обратного путем прибавления. Обратный ход преобразуем0

1,

а1

1,

а1 0.

0.

7. Кодирование графических данных. Существует два вида кодирование: векторный и растровый. Векторный- графические данные разбиваются на примитивные элементы и описываются с помощью математической зависимости(графики, таблицы, чертежи). «+»-сы: Простота редактирования; качество изображения не зависит от масштаба; высокая точность контуров изображения; размер файла не зависит от размера объекта.«-»-сы: неуниверсальность; отсутствие аппаратных средств оцифровки; сложность реализации. Растровые- изображения кодируются в виде точек(пикселей) (триада: красный, зеленый, синий), отражающих цвет, яркость, прозрачность. «+»-сы: универсальность; наличие аппаратных средств оцифровки. «-»-сы: сложность редактирования; качество изображения зависит от масштабирования; более низкая точность передачи; размер файла зависит от размеров изображения; аппаратная зависимость.

8. Кодирование звука. -Аналоговые: «+»-сы: возможность редактирования; долговечность хранения; возможность восстановления данных. «-»-сы: тяжесть редактирования; недолговечность носителя; не очень высокое качество.

-Цифровое: частотная модуляция; частота дискретизации; волновые таблицы. (Ребзя, дальше идет картинка, ее спишите с Машиной фотографии).Достоинство волновых таблиц- звук более ярче. Семплы–элементарные звуки волновой таблицы.

9.

Статические данные: память распределяется, значение не может измениться в процессе обработки данных

+ обратный доступ к ним

- нерациональное использование оперативной памяти

Константы- данные, значения которых нельзя изменить в процессе обработки данных

Переменные-данные, значения которых могут измениться в процессе обработки данных

Массивы организованная последовательность данных одного типа,занимающая,непрерывную область памяти. Массивы: одномерные,многомерные

Размерность-колличество видов и размеров массива

Динамические данные-данные память под каторые может выделяться в процессе их обработки.

10. Постоянные, переменные, массивы.Постоянные данные- данные, значение которых нельзя изменить в процессе обработки данных. Массивы- организованная исследовательность данных одного типа, занимающая непрерывную область памяти. Массивы: одномерные и многомерные. Размерность- количество изменений массива. Переменные- данные, значения которых может измениться в процессе обработки данных.

11. Списки.

Бывают разомкнутые и замкнутые, односвязные и двухсвязные.

Списки- связанные объекты.

Там таблица есть-также просмотрите ее у Маши.

«+»-сы односвязных:

1). Простая реанимация;

2). Занимают меньше памяти, чем двухсвязные.

«-»-сы:

1). Позволяют организовать движение в одном направлении;

2). Обладают меньшей надёжностью.

«+»-сы двухсвязных:

1). Надёжность;

2). Возможность двигаться в двух направлениях.

«-»-сы:

1). Сложная реанимация;

2). Больше памяти, занятой объектом. В односвязном разомкнутом списке последний адрес= 0. В односвязном замкнутом списке последний адрес- адрес первого элемента. В двухсвязном: разомкнутый, если первый адрес первого элемента хранит адрес последнего элемента, второй адрес последнего хранит адрес первого элемента. По способу формирования списки: Очереди, стеки, деки. Очередь- добавление элемента в конец списка, а удаление из начала. Стеки- добавление и удаление с конца. Деки- удаление и добавление с начала и с конца.

12.Графы

Граф – сложная, нелинейная, многосвязная, динамическая структура, отображающая свойства и связи сложно объекта.

Свойства

объекта

Свойства

объекта

Многосвязная

область

Многосвязная

область

Адрес

Классификация графов

По направлению связи: ориентированные, неориентированные, смешанные

Ориентированные – определено направление перемещения.

По форме:

Планарные (без пересечения связи)

Пространственные

Могут быть

Взвешенные

Невзвешенные (связь имеет весовую характеристику)

13Система счисле́ния — символический метод записи чисел, представление чисел с помощью письменных знаков.

Все системы счисления делятся на позиционные(ПСС) и непозиционные(НПСС)

Позиционная система счисления-представление чисел ,в котором последовательные числовые разряды являются последовательными целыми степенями некоторого целого числа,называемого основанием системы счисления

Основание системы счисления- отношение соседних разрядов числа

ПСС используют ограниченный набор символов, называемых цифрами, и величина числа зависит не только от набора цифр, но и от того, в какой последовательности записаны цифры т.е. от позиции, занимаемой цифрой

НПСС для записи числа используют бесконечное множество символов, и значение символа не зависит от того места ,которое он занимает в числе(пример:римская система счисления)

14Двоичная система счисления — позиционная система счисления с основанием 2. Благодаря непосредственной реализации в цифровых электронных схемах на логических вентилях, двоичная система используется практически во всех современных компьютерах и прочих вычислительных электронных устройствах.

![]()

![]()

15. Шестнадцатеричная система счисления (шестнадцатеричные числа) — позиционная система счисления по целочисленному основанию 16.

Правила перевода смотри учебник Шапорева стр 10!!!!!

16

Этапы развития ЭВМ

1642 г – Б. Паскаль изобрел арифмометр (сложение, вычитание)

1673 г – Лейбниц ввел двоичную систему счисления (+,-,*,/) 1823– Ч. Беббидж разработал структуру вычислительной машины:

Вычислительная машина должна иметь:

а)вычислительное устройство управления

б)память

в)устройство ввода и вывода данных

Начало 40-х – разработка атомной бомбы развитие вычислительной техники. Машины на основе реле: Konrad Zuse (IBM), Howard Iken (ASCC)

1946 г – изобретение ламп. Первая машина ENIAC просчитала ядерную реакцию

50-60-е годы полупроводниковые ЭВМ

60-70-е Джек Килби. Машины на больших интегральных схемах

70-е Схемы высокой интеграции

17

Классификация ЭВМ

По принципу действия:

а)Аналоговые

б)Цифровые

в)Гибридные

По размеру и мощности:

-Супер ЭВМ (10-ки миллиардов операций в секунду) – расчет ядерных реакций; моделирование атмосферы; расчет траектории движения космических кораблей

-Большие ЭВМ (миллиарды операций в секунду)

-Средние ЭВМ (10-100 миллионов операций в секунду) HP, Dell. Моделирование, прогнозирование задач средней сложности

-Мини ЭВМ (ПК, Intel)

-Микро ЭВМ

По назначению:

а)Универсальные – решение задач

б)Специализированные – управление и контроль

18.Архитектура ЭВМ

Архитектура ЭВМ включает в себя структуру, отражающую состав ПК, так и программно-математическое обеспечение. Структура ЭВМ- совокупность элементов и связей между ними. Основным принципом построения всех современных ЭВМ является программное управление.

К архитектуре относятся следующие принципы построения ЭВМ:

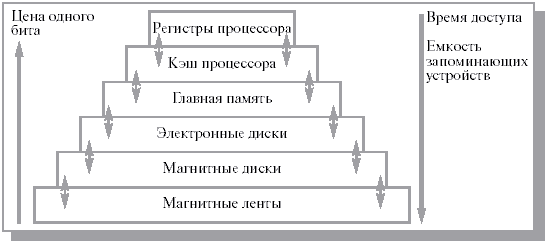

1)Структура памяти

1-регистр процессора

Быстрое

Действие

Объем

Памяти

19

Виды архитектуры ЭВМ

Концептуальная структура вычислительной машины, определяющей проведение обработки информации и включающая методы информации в данные и принципы взаимодействия технических средств и программного обеспечения.

Неймановская архитектура

Арифметико-логическое устройство

Устройство управления

Запоминающее устройство

Устройство ввода

Устройство вывода

память

АЛУ

УУ

У ввода

У вывода

Совместное использование памяти (для размещения данных и программ)

Команды и данные обрабатываются послежовательно

Гарвардская архитектура

Отличие от Неймановской:

Раздельное использование памяти

Позволяет одновременно обрабатывать данные и команды

+ :быстрая, надежная

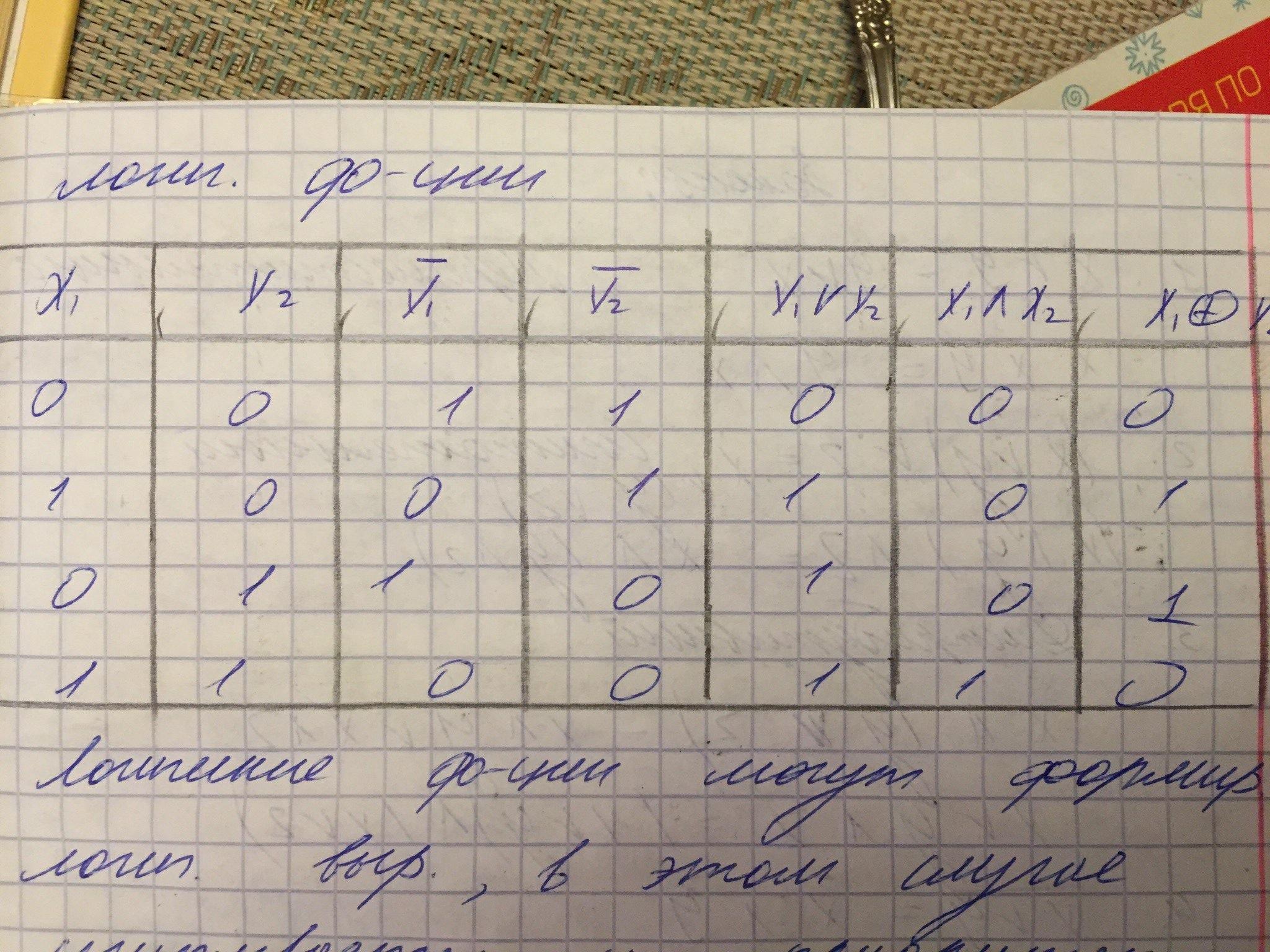

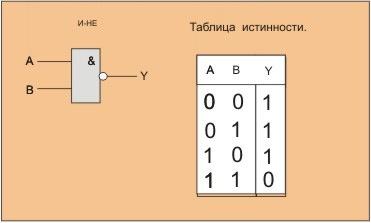

:сложная, дорогая 21.Логические основы работы ЭВМ

Для описания логики функции ЭВМ используется алгебра логики

Оперирует логическими элементами: истина и ложь. Одни и те же устройства ЭВМмогут использоваться так и для логических операций. Совокупность логических элементов- набор переменных, эти переменные используют логические функции. Логическая функция-функция, которая может принимать только 2 значения: 1 или 0 (истина или ложь)

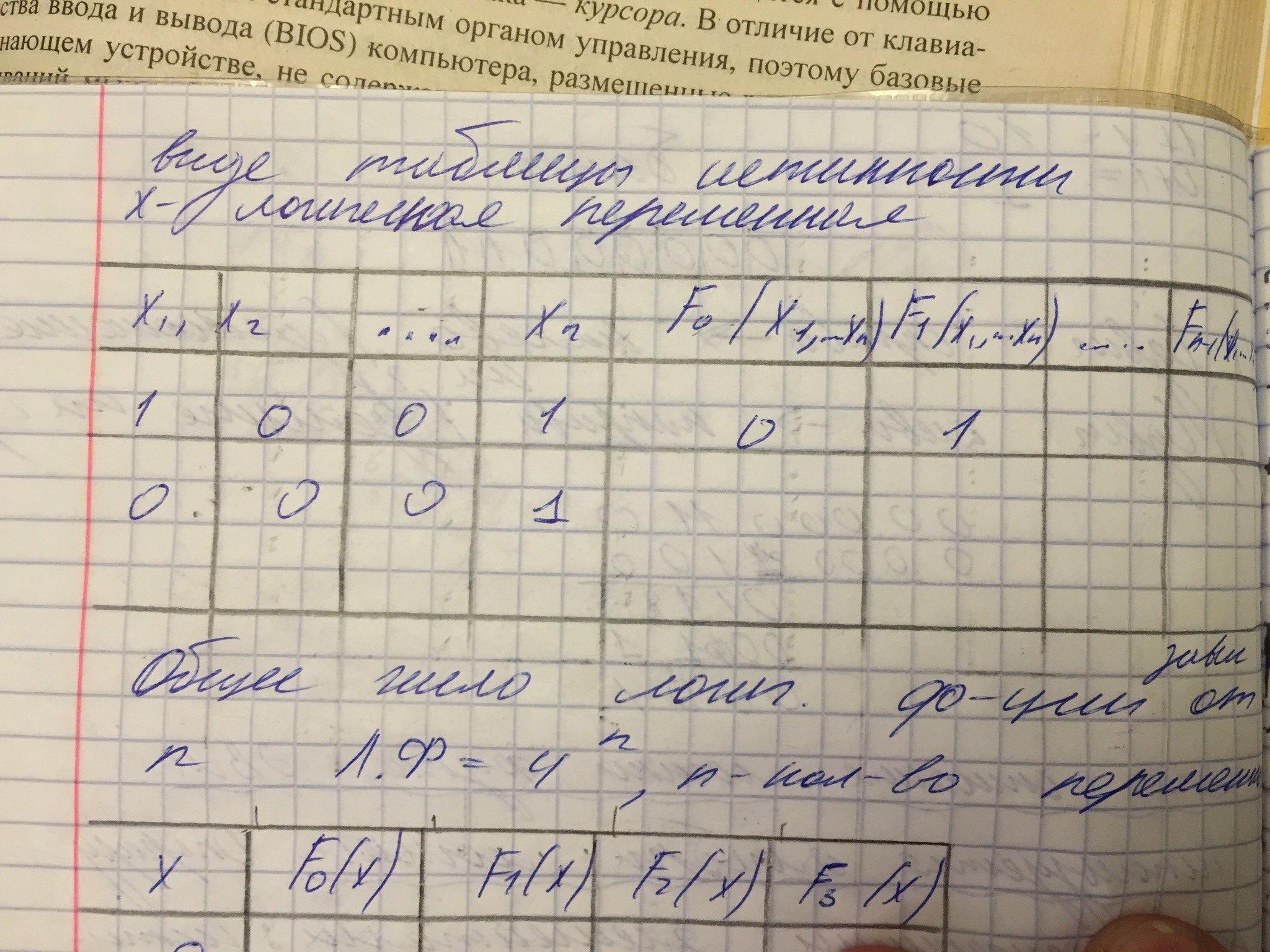

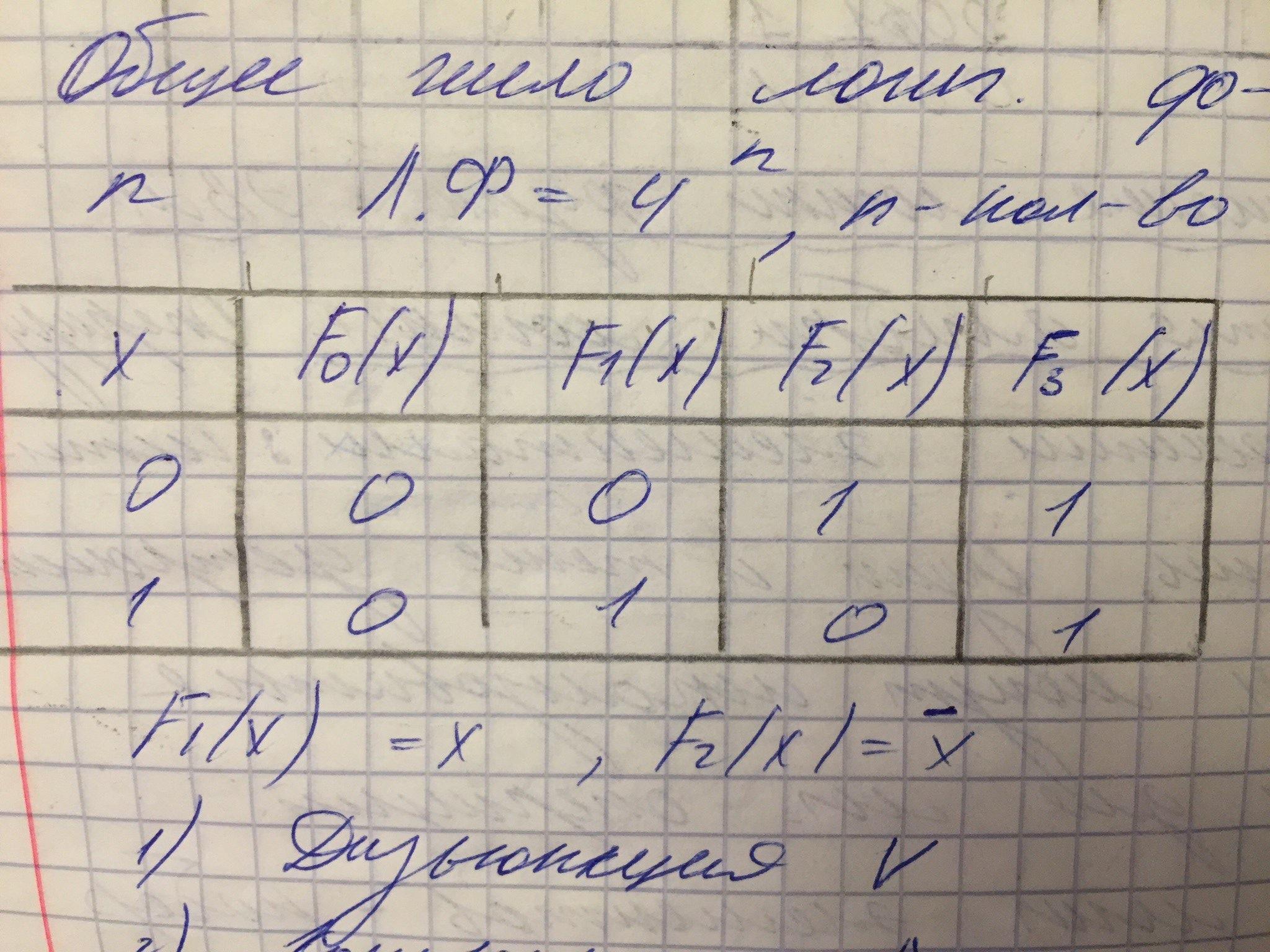

Логические функции задаются в виде таблицы. Х-логическая переменная.

Общие число логических функций зависит от n, Лог.ф.=4n, n-кол-во переменных.

F1(x)=x, F2(x)=x

1)Дизьюнкция

1)Дизьюнкция

2)Коньюнкция

2)Коньюнкция

3) Исключение или +

4)Инверсия

4)Инверсия

Эти 4 функции образуют систему элементарных функций , с помощью которых описываются более сложные логические функции.

Логические функции могут формировать логические выражения, в этом случае учитывается их приоритет

Самые высокий- инверсия, затем коньюнкция, исключение, дизьюнкция.

22

23

25.архитектура

ЦП

22

23

25.архитектура

ЦП

Контроллер памяти C\D C\D C\D CD CD CD CD L C4 C3 C\D C2 C1 C\D Видео

ядро HD

600

Haswell

Ядро

Ядро

команды

32KB

CASH

L1

команды

32KB

CASH

L1

32KB

КЭШ

данные

КЭШ

данные

Самый быстрый

интерфейс

256KB

CASH

L3

интерфейс

256KB

CASH

L3

6\8 MB

CASH

L3

6\8 MB

CASH

L3

команды\данные

Частота

памяти

Частота

памяти

Синхронизация с оперативной памятью

26

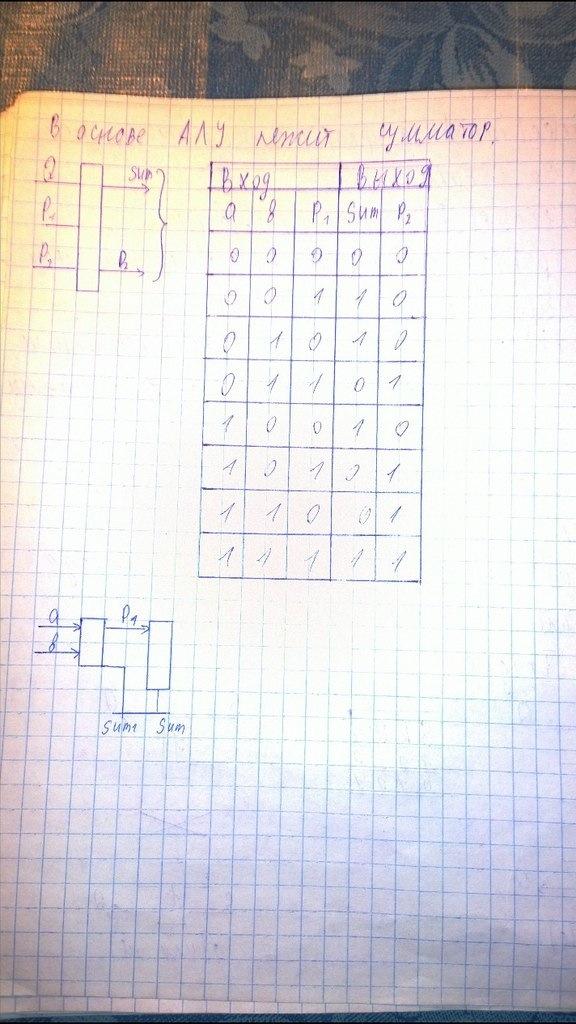

31. АЛУ ядра процессора (структурная схема-это уже сами, принцип работы).

Арифметико-логическое

устройство (АЛУ)-

блок процессора,

который

под управлением устройства

управления (УУ)

служит

для выполнения арифметических и

логических преобразований (начиная

от элементарных)

над

данными,

называемыми

в этом случае операндами.

Разрядность

операндов обычно называют размером машинного

слова.

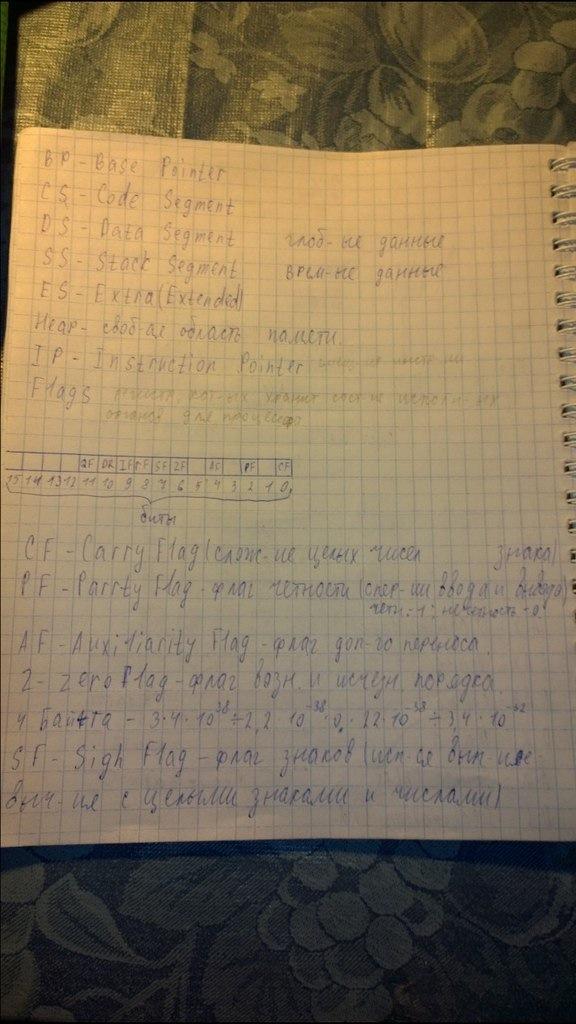

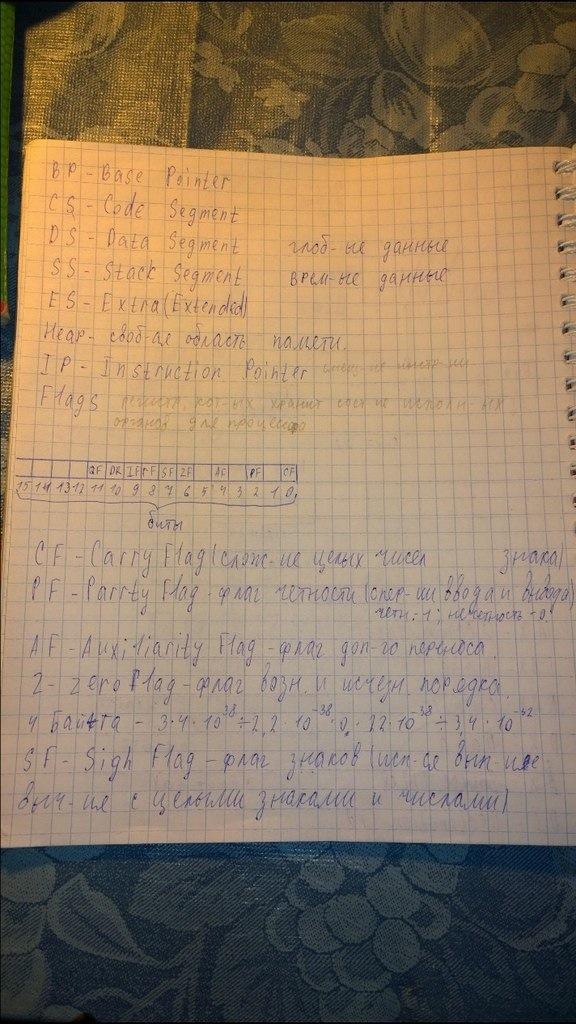

32. Система и формат команд ядра процессора. Систем команд: RISC и CISC. Группа команд: 1). Работа с памятью; 2). Обработка данных. Itanium и Alpha DEC- процессоры для малых ЭВМ. CISC- характеризуется многообразием форматов. Формат команды: Команды: 1). По функциональному назначению- передача данных- обработка данных- передача управления- дополнительные; 2). Количество адресов- Безадресный- 1 адресные- 2 адресные- 3 адресные.

33. Классификация команд ядра процессора. Команды: 1). По способу кодирования- 1 байтовые и 2 байтовые; 2). По длине команд- 1-2 байтовые и многобайтовые; 3).по способу адресации: регистр-решение, регистр-память, память-память. Также команды бывают общего назначения и взаимодействующие с памятью. Расширенная система команд: 1. NMX- обработка аудио и видео; 2. SSEx1- обработка вещественных чисел, SSEx2- обработка вещественных чисел с двойной точностью, SSEx3- команды для оптических работ с регистрами, SSEx4- работа с видеопотоками для обработки двухбайтных символов команды векторной обработки данных.

34.

Память ЭВМ (назначение,

логическая и физическая

организация).Память

ЭВМ-часть электронной вычислительной машины, предназначенная для приема, хранения и

выдачи информации (данных), образуется из одного или нескольких запоминающих устройств (ЗУ).

К основным способам логической

организации памяти относятся адресная,

ассоциативная и стековая организации.

В случае адресной организации

размещение и поиск информации в ЗМ

основаны на использовании адреса

хранения слова-

номера ячейки ЗМ.

Ассоциативная.

Поиск производится не по адресу

ячейки, а по ее

содержимому(по

ассоциативному признаку).

Поиск при этом производится

параллельно во всех ячейках ЗМ.

Менее универсальная(гибкая)

организация, но

за счет совмещения операций выборки из

памяти с логическими операциями можно

ускорить обработку данных(например

в базах данных).

Стековая. Как

и ассоциативная-

безадресная стековая память-

одномерный массив ячеек.

Запись/выборка

производится по дисциплине “последний

пришел- первым

обслужен”(LIFO).

Основная оперативная память

вычислительной машины обычно является

адресной. Это

значит, что

каждой хранимой в памяти единице

информации(слову,

байту) ставится

в соответствие специальное число-

адрес, определяющий

место ее хранения в памяти.

Физическая организация памяти ЭВМ:

35.

Статическая память ЭВМ (структурная

схема и принцип работы).

Статическая

память- SRAM (Static

Random Access Memory), как и следует из ее

названия, способна

хранить информацию в статическом режиме- то есть сколь

угодно долго при отсутствии обращений(но при наличии

питающего напряжения).

Ячейки статической памяти реализуются

на триггерах-

элементах с двумя устойчивыми

состояниями. По

сравнению с динамической памятью эти

ячейки более сложны и занимают больше

места в кристалле,

однако они проще в управлении и не

требуют регенерации.

Быстродействие и энергопотребление

статической памяти определяется

технологией изготовления и схемотехникой

запоминающих ячеек.

Достоинства:

высокая скорость работы;

нет необходимости регенерации ячеек.

Недостатки:

высокая цена;

низкая плотность упаковки;

небольшой объем;

высокое энергопотребление.

В связи с перечисленными выше достоинствами и недостатками, область применения статической памяти ограничивается, в основном, использованием ее в качестве КЭШ-памяти, что позволяет при небольшом увеличении стоимости уменьшить влияние недостатков динамической памяти на производительность ЭВМ. Однако, это все лишь компромисс, позволяющий несколько сгладить разрыв в производительности процессора и памяти, и все вытекающие отсюда последствия.

Требуется кардинальное решение проблемы существующей с момента зарождения вычислительной техники. Существует множество экспериментальных разработок, позволяющих получить быструю и дешевую оперативную память, но многие из них пока существуют только в виде лабораторных образцов, многие имеют недостаточную надежность и так далее. Наиболее перспективный путь развития оперативной памяти – это использование магниторезистивной памяти, получающей все большее распространение.

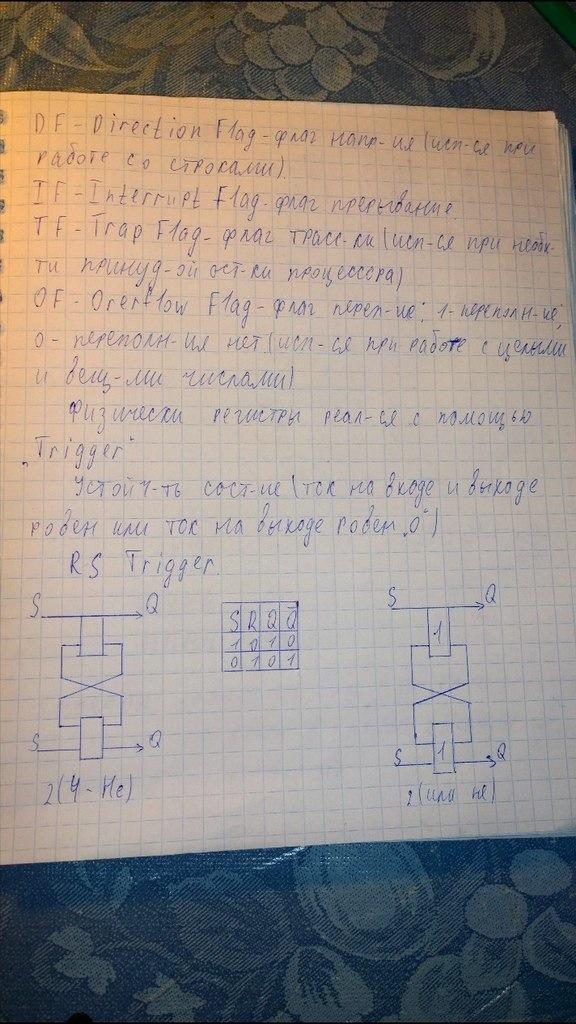

36-37.

Триггер И-НЕ

и Триггер ИЛИ-НЕ.Триггер

– это электронное устройство, которое

предназначается для записи и хранения

информации. Обычно он имеет два выхода:

прямой и инверсный; и некоторое количество

входов, в зависимости от выполняемой

задачи. Под действием входных сигналов,

изменяется состояние выходов. Напряжение

на выходах изменяется резко –

скачкообразно. Для изготовления триггеров

обычно используютсябиполярные, униполярные

транзисторы (полупроводниковые приборы).

Триггер И-НЕ:

Триггер

ИЛИ-НЕ

38. Динамическая память ЭВМ.Динамическая память - это оперативная память ЭВМ, предоставляемая Турбо-Паскалевой программе при её работе, за вычетом сегмента данных (64 К), стека (обычно 16 К) и собственно тела программы. По умолчанию размер динамической памяти определяется всей доступной памятью ЭВМ и, как правило, составляет не менее 200 - 300 Кбайт.

Динамическую память обычно используют при: 1. обработке больших массивов данных; 2. разработке САПР; 3. временном запоминании данных при работе с графическими и звуковыми средствами ЭВМ. Типы динамической памяти: FTM (Fast Page Mode) – режим быстрого страничного обмена. Преимущество данного режима заключается в экономии времени за счет исключения фазы выдачи адреса строки из циклов, следующих за первым, что позволяет повысить производительность памяти. EDO (Extended Data Out) DRAM. Эта память содержит регистр-защелку выходных данных, что обеспечивает некоторую конвейеризацию работы для повышения производительности при чтении. Регистр прозрачен при низком уровне сигнала CAS#, а по его подъему фиксирует текущее значение выходных данных до следующего его спада. Отличие этого режима от стандартного заключается в подъеме импульса CAS# до появления действительных данных на выходе микросхемы. Считывание выходных данных может производится внешними схемами вплоть до спада следующего импульса CAS#, что позволяет экономит время за счет сокращения длительности импульса CAS#. BEDO (Burst EDO) DRAM. В микросхемах данного типа кроме регистра-защелки выходных данных, содержится еще и внутренний счетчик адреса колонок для пакетного цикла, а во 2-й, 3-й и 4-й передачах импульсы CAS# только запрашивают очередные данные. В результате удлинения конвейера выходные данные отстают на один такт CAS#, зато следующие данные появляются без тактов ожидания процессора. SDRAM (Synchronous DRAM) – быстродействующая синхронная динамическая память, работающая на частоте системной шины без тактов ожидания внутри пакетного цикла. От обычной динамической памяти, у которой все внутренние процессы инициируются только сигналами RAS#, CAS# и WE#, память SDRAM отличается использованием постоянного присутствующего сигнала тактовой частоты системной шины. Это позволяет создавать внутри микросхемы высокопроизводительный конвейер на основе ячеек динамической памяти с обычным временем доступа (50-70нс). Микросхемы SDRAM являются устройствами с программируемыми параметрами, со своим набором команд и внутренней организацией чередования банков.

Достоинства и недостатки динамической памяти.

Преимущества динамической памяти:

низкая себестоимость;

высокая степень упаковки, позволяющая создавать чипы памяти большого объема.

Недостатки динамической памяти:

относительно невысокое быстродействие, так как процесс зарядки и разрядки конденсатора, пусть и микроскопического, занимает гораздо больше времени, чем переключение триггера;

высокая латентность, в основном, из-за внутренней шины данных, в несколько раз более широкой, чем внешняя, и необходимости использования мультиплексора/демультиплексора;

необходимость регенерации заряда конденсатора, из-за его быстрого саморазряда, ввиду микроскопических размеров.

39. Структурная схема и принцип работы ячейки динамической памяти.Рассмотрим структурную схему ячейки динамической оперативной памяти. Её можно представить из трёх элементов: – транзистора, выполняющего роль ключа; – конденсатора, который хранит информацию; – устройства регенерации, которое регенерирует заряд конденсатора или информацию на нужных конденсаторах;

На самом деле, отдельного конденсатора нет, его роль выполняет ёмкость между затвором и истоком транзистора. Но для простоты изложения ёмкость выделена как бы в отдельный элемент.

Поскольку ёмкость достаточно маленькая и имеет место достаточно быстрый её разряд, т.е. потеря информации, в случае, если была записана «1», возникает необходимость в регенерации между разрядами. Кроме того, при считывании из ячейки оперативной памяти информации, заряд также исчезает, поэтому и в этом случае необходима регенерация. Устройство регенерации и осуществляет постоянные циклы регенерации или восстановления информации.

Работу ячейки памяти можно представить таким образом. Конденсатор можно представить в виде ёмкости, в которую наливается вода. Транзистор в виде ключа или крана, который открывает или перекрывает трубу, по которой течёт вода в ёмкость, а устройство регенерации в виде источника воды. В нужный момент кран открывается и это служит признаком того, что необходимо пополнить ёмкость водой. Конечно, рассматривая работу ячейки памяти таким образом, можно представить, что ёмкость с водой немного дырявая. Это утверждение имеет под собой основание, так как конденсатор, в случае хранения «1» и до тех пор, пока она записана, должен постоянно подзаряжаться схемой регенерации.

Ячейка памяти хранит в себе один бит информации, для того чтобы динамическая память хранила бы в себе мегабайты, а сейчас уже и гигабайты данных, необходимо чтобы все эти элементарные по объёму ячейки памяти объединялись между собой в большие массивы, накопители или матрицы памяти. Организация динамической оперативной памяти на этом уровне будет описана в следующей статье.

40.

41.Принцип работы динамической памяти при чтении при наличии заряда на конденсаторе;

Рассмотрим случай, когда в конденсаторе нет заряда (ячейка памяти хранит бит со значением «1»): Ток, создаваемый входным напряжением Uп, пойдет по линии AЕ, так как транзистор VT2 будет закрыт. Следовательно, на входе Q1 «Буфера данных» будет ток, что означает – с ячейки памяти считана единица. Информация о считанном бите с первого столбца будет записана в «Буфер данных». Так как в конденсаторе заряда не было, то и подзаряжать его надобности нет. Следовательно, с блока регенерации ток пойти не должен. Так как на выходе Q1 ток есть, то он поступает и в «Блок регенерации». Следовательно, на нижний вход элемента L3 (логическое «И») подается логическая единица. Так как мы рассматриваем случай чтения данных, то сигнала записи V1 и данных для записи D1 в «Блок регенерации 1» подаваться не будет. Так же в остальные блоки регенерации, соответствующие сигналы D1-Dm и V1-Vm так же подаваться не будут. Следовательно, на входе элемента L1 (логическое «НЕ») будет логический ноль, а на выходе – логическая «1». Таким образом, на входах элемента L3 (логическое «И») будут две логические единицы. В результате, на выходе получим так же логическую единицу. На выходе логического элемента L2 (логическое «И») будет логический ноль, так как на обоих его входах напряжение отсутствует, так как от контроллера памяти нет команд на запись и данных для записи. В результате, на входах элемента L4 (логическое «ИЛИ-НЕ») будет логический ноль и логическая единица, а, соответственно, на его выходе будет логический ноль, то есть напряжение будет отсутствовать. Так как напряжение отсутствует, то ни один из конденсаторов первого столбца матрицы памяти подзаряжаться не будет. 5. Параллельно с чтением и регенерацией данных первого столбца происходит по такому же алгоритму чтение данных с остальных столбцов. В результате, в буфер данных будет записано значение всех ячеек памяти первой строки. 6. С контроллера памяти на дешифратор адреса столбца выдаются номера столбцов для считывания. За один такт номера считываются сразу с нескольких столбцов. Количество столбцов для считывания определяется разрядностью процессора и способом его взаимодействия с памятью. Для 32-разрядных процессоров минимальной порцией является считывание данных с 32 столбцов. 7. С дешифратора адреса столбцов номера столбцов передаются в «Буфер данных», откуда соответствующие данные считываются и передаются в процессор.

42. Принцип работы динамической памяти при чтении при отсутствии заряда на конденсаторе;

Ток создается входным напряжением пойдет не по линии AE . т.к. Т2 замкнут Q1- идет ток=> в ячейку памяти 1. Информация о считанном бите 1го столбца данных. С блока регенерации ток не поступает так как к линии Q – ток есть. Он поступает в блок L1-л1. По линии V1 и D1 – не подается ( как и вдругие блоки регенерации).

На входе элемента L1-л0 т.о на выходах элемента L3- будут 2 логические единицы => на выходе Л0

На выходе лог. Элемента L2 –ЛО так как на обоих входах нет напряжения => Л0. В результате на входах элемента L4 будет Л0 и Л1.

5)Параллельно с чтением и регенерацией данных 1 столбца происходит чтение данных с остальных => в буфере данных будут значения всех ячеек памяти 1 строки.

6)Дешифратор адреса столбцов номера столбцов передается в буфер данных, откуда данные передаются в процессор.

43. Принцип работы динамической памяти при записи данных;

1) Контроллер памяти получает команду на запись данных и адрес, куда нужно записать данные

2)Контроллер памяти преобразует адрес на две составляющие:

Номер строки и номер столбца

Данные поступают в блок работы с данными

3) Дешифратор адреса номера строки подает сигнал в соответствующую строку матрицы памяти

4)Подается сигнал с блока работы данных

5)Напряжение поданное на строкуS1 откроет транцисторыT1 иT3

6)Если в линие границе сь со значением0, то ток создаваемый напряжением О2*nпойдет по линииAB , иначе по линииAD

С выхода элемента L3 блока регенерации будет идти логически О т.к. в дешифраторы столбцов проходит сигналлинииL1 на запись данных в1 столбец. В результате на выходеL1-n1, а на выходе – лог0.

Соответственно на верхнем входе Lз тогда имеем лог0 , что означает независимость от значения в конечном входе. На выходеL3

-лог0. на нижнем входе –л1 т.к дешифратор адреса столбцов подается сигнал, а на верхнем входе будет либо0 либо1 в зависимости от того в каком значении записывает информацию бит1 имеет2 еденицы на Входе на выходе- лог0 -> на входеL4-n1 иn0. В результате на выход – лог0-> Заряд конденсатора идти не будет, если до этого конденсатор содержал заряд, то через несколько секунд он разрядится, пропускается ток по линииAB.

44.Тайминги динамической памяти;

Тайминг — это задержка между отправкой команды контроллера памяти и её выполнением, измеренная в тактах шины памяти(т.е. сколько тактов пропускает шина в ожидании выполнения команды).

В основе динамической памяти (DRAM)лежат ячейки, объединенные в двумерные массивы. Такую структуру можно представить в виде решетки с ячейками в её узлах. Чтобы обратиться к одной из них, контроллеру надо знать её адрес. Он состоит из двух компонентов: номера строки и номера столбца. Массивы ячеек с одинаковым количеством строк и столбцов объединяются в банки. Контроллер выбирает необходимый банк и посылает ему адрес строки(сигналRAS). Доступ к нужной строке занимает некоторое время, т.е таймингRAS to CAS Delay. Затем посылается адрес столбца(сигналCAS)и опять ожидается ответ — задержка(тайминг)CAS Latency. ТаймингRAS Prechargeпоказывает время между командой закрытия и повторной активацией строки.Active to Precharge Delay— между командой активации и командой закрытия. И наконец,Command Rate— это минимальное время между подачей любых двух команд.

45.ПамятьDDR;

DDR SDRAM - синхронная динамическая память с произвольным доступом и удвоенной скоростью передачи данных) — тип компьютерной памяти, используемой в вычислительной технике в качестве оперативной и видеопамяти. Пришла на смену памяти типа SDRAM. При использовании DDR SDRAM достигается удвоенная скорость работы, нежели в SDRAM, за счёт считывания команд и данных не только по фронту, как в SDRAM, но и по спаду тактового сигнала. За счёт этого удваивается скорость передачи данных без увеличения частоты тактового сигнала шины памяти. Таким образом, при работе DDR на частоте 100 МГц мы получим эффективную частоту 200 МГц (при сравнении с аналогом SDR SDRAM). В спецификации JEDEC[1] есть замечание, что использовать термин «МГц» в DDR некорректно, правильно указывать скорость «миллионов передач в секунду через один вывод данных».Специфическим режимом работы модулей памяти является двухканальный режим.

Спецификация чипов памяти

DDR200: память типа DDR SDRAM, работающая на частоте 100 МГц DDR266: память типа DDR SDRAM, работающая на частоте 133 МГц DDR333: память типа DDR SDRAM, работающая на частоте 166 МГц DDR400: память типа DDR SDRAM, работающая на частоте 200 МГц

46.ПамятьDDR2;

DDR2 SDRAM - синхронная динамическая память с произвольным доступом и удвоенной скоростью передачи данных, второе поколение) — это типоперативной памяти, используемой ввычислительной техникев качестве оперативной и видеопамяти. Пришла на смену памятиDDR SDRAM. Как и DDR SDRAM, DDR2 SDRAM использует передачу данных по обоим срезам тактового сигнала, за счёт чего при такой же частоте шины памяти, как и в обычной SDRAM, можно фактически удвоить скорость передачи данных (например, при работе DDR2 на частоте 100 МГц эквивалентная эффективная частота для SDRAM получается 200 МГц). Основное отличие DDR2 от DDR — вдвое большая частота работы шины, по которой данные передаются в буфер микросхемы памяти. При этом, чтобы обеспечить необходимый поток данных, передача на шину осуществляется из четырёх мест одновременно. Итоговые задержки оказываются выше, чем для DDR.Внешнее отличие модулей памяти DDR2 от DDR — 240 контактов (по 120 с каждой стороны)

Тип чипа Частота памяти, МГц Частота шины, МГц Эффективная частота,МГц DDR2-400 100 200 400

DDR2-533 133 266 533

DDR2-667 166 333 667

DDR2-800 200 400 800

DDR2-1066 266 533 1066

47.ПамятьDDR3;

DDR3 SDRAM - синхронная динамическая память с произвольным доступом и удвоенной скоростью передачи данных, третье поколение)— это типоперативной памяти, используемой ввычислительной техникев качестве оперативной и видеопамяти. Пришла на смену памяти типаDDR2 SDRAM, увеличив размер предподкачки с4 бит до8 бит.

У DDR3 уменьшено потребление энергии по сравнению с модулями DDR2, что обусловлено пониженным (1,5 В, по сравнению с 1,8 В для DDR2 и 2,5 В для DDR) напряжением питания ячеек памяти.[3][4] Снижение напряжения питания достигается за счёт использования более тонкого техпроцесса (в начале 90-нм, в дальнейшем 65, 50, 40 нм) при производстве микросхем и применения транзисторов с двойным затвором Dual-gate (что способствует снижению токов утечки).

Существует вариант памяти DDR3L (L означает Low) с ещё более низким напряжением питания, 1,35 В, что меньше традиционного для DDR3 на 10 %.[5]

В 2012 году было сообщено о выходе памяти DDR3L-RS для смартфонов.[6]Микросхемы памяти DDR3 производятся исключительно в корпусах типа BGA.

48.ПамятьDDR4;

DDR4 SDRAM - новый тип оперативной памяти, являющийся эволюционным развитием предыдущих поколений DDR (DDR, DDR2, DDR3). Отличается повышенными частотными характеристиками и пониженным напряжением питания.

Основное отличие DDR4 заключается в удвоенном до 16 числе банков, что позволило вдвое увеличить скорость передачи — до 3,2 Гбит / с. Пропускная способность памяти DDR4 достигает 34,1 ГБ / c (в случае максимальной эффективной частоты 4 266 МГц, определённой спецификациями). Кроме того, повышена надёжность работы за счёт введения механизма контроля чётности на шинах адреса и команд. Будет поддерживать эффективные частоты от 2 133 до 4 266 МГц. Следует учесть, что эффективная частота отличается от частоты тактирования. Под эффективной частотой понимается защелкивание данных по переднему и заднему фронтам. В связи с этим, реальная тактовая частота работы памяти в два раза меньше относительно эффективной частоты.В массовое производство вышла во 2 квартале 2014 года. Старт продаж начался в Японии, а в июле эта память появилась в странах Европы.

49. Flash память.Это полупроводниковая, электрически перепрограммируемая память. Основное достоинство- энергозависимость (не нужно электричество для хранения данных). Считывать информацию можно бесконечное количество раз. Количество записи ограничено. Элементарная ячейка хранения данных флэш памяти- транзистор с плавающим затвором. Особенности его в том, что он может удерживать заряд. Используют два типа ячеек памяти:MLCиSLC.MLC- многоуровневые ячейки памяти (более емкие и дешевые, большее время доступа и меньшее количество циклов записи примерно 10000).SLC-одноуровневые ячейки памяти (меньшее время доступа и большее количество циклов записи примерно 100000). Флэш память бывает двух типов:NANDиNOR. Принцип работы флэш памяти основан на изменении и регистрации электрического заряда в области полупроводниковой структуры. Изменение заряда (запись, стирание) выполняется приложение между затвором и истоком потенциала. Чтобы напряженность электрического поля в тонком диэлектрике между каналом транзистора и изолированной областью оказалось достаточно для возникновения тоннельного эффекта. Для усиления эффекта тоннелирования электронов при записи применяется ускорение электронов путем пропускания электронов через канал полевого транзистора (П.Т.). Чтение выполняет ПТ, для которого канал выполняет роль затвора, потенциал ПТ, что регистрирует. Эта конструкция снабжается элементами, которые позволяют ей работать в таком же массиве ячеек. Существуют ячейки с одним или с двумя транзисторами.