ЭВМ ответы

.docxТипы АЦП:

-

АЦП последовательного счета

-

АЦП поразрядного кодирования

-

АЦП параллельного действия

Цифро-аналоговые преобразователи.

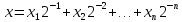

ЦАП – преобразует цифровую информацию в аналоговую в виде напряжения (иногда тока)

ЦАП состоит

в том, что для входного n-разрядного кода

сначала получают ток Ix,

пропорциональный числу x,

а затем преобразуют его в выходное

напряжение.

сначала получают ток Ix,

пропорциональный числу x,

а затем преобразуют его в выходное

напряжение.

Классификация ЦАП:

-

По принципу действия

-

Со сложением токов

-

С делением напряжения

-

Со сложением напряжения

-

-

По виду выходного сигнала

-

Полярность выходного сигнала

-

Элементная база

Основные характеристики ЦАП:

-

Количество разрядов

-

Быстродействие

-

Точность преобразования

-

Потребляемая мощность

-

Статические параметры

-

Разрешающая способность

-

Погрешность преобразования

-

Диапазон значений выходного сигнала

-

Напряжение смещения нуля

-

Погрешность в конечной точке шкалы

-

Нелинейность

-

-

Динамические характеристики

-

Время установления выходного сигнала – интервал времени от момента подачи входного кода до момента вхождения выходного сигнала в заданные пределы

-

Максимальная частота преобразования – наибольшая частота дискретизации при которой все параметры ЦАП соответствуют заданным значениям

-

Динамическая погрешность

-

ЦАП со взвешенными резисторами.

ЦАП с матрицей R-2R

Способы сжатия программного кода (циклические программы)

При написании программы часто встречаются последовательности команд, которые отличаются только участвующими в них данными. Такие последовательности можно заменить циклической программой. Это может значительно сократить число команд в программе, т.е. объем занимаемой ею памяти, но время выполнения программы увеличивается.

|

Адрес |

Код |

Метка |

Команда |

Примечание |

|

8000 8001 |

00 |

Start: |

MVI A, 0 |

A=0 |

|

8002 |

|

Loop: |

INR A |

A=A+1 |

|

8003 8004 |

|

|

CPI 10 |

A==10 |

|

8005 8006 8007 |

00 80 |

|

JZ Start |

Переход на метку Start |

|

8008 8009 800A |

02 80 |

|

JMP Loop |

Переход на метку Loop |

Способы сжатия программного кода (подпрограммы)

В большинстве программ некоторые последовательности команд, выполняющие определенную функцию, встречаются несколько раз, но оперируют с различными данными. Такую последовательность удобно включить в программу 1 раз, и в нужных точках вызывать ее для выполнения с другими данными. Такая последовательность команд называется подпрограммой.

Подпрограмма представляет собой законченный сегмент программы, который можно вызывать любое число раз.

Достоинства:

-

Разделение сложной программы на простые блоки

-

Каждую подпрограмму можно отладить отдельно

-

Сокращает длину программы, т.е. объем занимаемой памяти

Недостаток:

-

Вызов подпрограммы и возврат из нее связаны с потерями времени МП.

-

Нарушается порядок следования команд.

CALL – вызов подпрограммы

RET – возврат из подпрограммы

Для запоминания в стеке содержимого регистров используется команда PUSH, а для извлечения POP

Организация памяти

Совместно используемая память. Пропускная способность шины ограничивает число ядер до 32. Дальнейшее увеличение ядер ведет к снижению производительности.

Выбор зависит от способа организации основной памяти. Если она является совместно используемой, то применяется вариант с общей шиной. В случае распределенной основной памяти коммуникацию может обеспечить лишь сеть.

КЭШ-память 2-ого уровня может быть либо индивидуальной для каждого ядра, либо общей для группы ядер (обычно на пару ядер). В новейших многоядерных процессорах присутствует КЭШ-память 3-его уровня.

Управление 7-сегментным индикатором (вывод статического слова)

|

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

h |

g |

f |

e |

d |

c |

b |

a |

|

|

Р |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

73 |

|

А |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

77 |

|

d |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

5E |

|

У |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

6E |

|

Г |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

31 |

|

Адрес |

Код |

Метка |

Команда |

Примечание |

|

8000 8001 |

73 |

|

MVI A, 73h |

|

|

8002 8003 8004 |

F8 83 |

|

STA 83F8h |

|

|

8005 8006 |

77 |

|

MVI A, 77h |

|

|

8007 8008 8009 |

F9 83 |

|

STA 83F9h |

|

|

800A 800B |

5E |

|

MVI A, 5Eh |

|

|

800C 800D 800E |

FA 83 |

|

STA 83FAh |

|

|

800F 8010 |

6E |

|

MVI A, 6Eh |

|

|

8011 8012 8013 |

FB 83 |

|

STA 83FBh |

|

|

8014 8015 |

31 |

|

MVI A, 31h |

|

|

8016 8017 8018 |

FC 83 |

|

STA 83FCh |

|

|

8019 801A |

0 |

|

MVI A, 0 |

|

|

801B 801C 801D |

FD 83 |

|

STA 83FDh |

|

|

801E 801F |

0 |

|

MVI A, 0 |

|

|

8020 8021 8022 |

FE 83 |

|

STA 83FEh |

|

|

8023 8024 |

0 |

|

MVI A, 0 |

|

|

8025 8026 8027 |

FF 83 |

|

STA 83FFh |

|

|

8028 |

|

|

HLT |

|

Семейство микроконтроллеров MCS-32 (8051 AH)

Это однокристальные системы, ориентированные на выполнение ф-й управления различными устройствами и процессами, поэтому они называются микроконтроллеры. Ранее они назыались однокристальными ЭВМ.

Сферы применения

-

Бытовая техника

-

Сложные системы управления технологическими процессами

-

Робототехнические комплексы

Архитектура МК

-

Совокупность внутренних и внешних ресурсов

-

Система команд

-

Система прерываний

-

Функции ввода/вывода

-

Протоколы обмена по магистралям

Конкретный МК семейства представляет собой определенную комбинацию модулей, основой которой является операционное ядро, общее для всех представителей семейства.

8051 AH – первый МК, выполненный на основе динамических элементов. Требует постоянной подачи напряжения. При пропадании напряжения питания структура микросхемы разрушается.

80C51/52/54/58 – выполнены с использованием комплементарной MOS-технологии – позволяет уменьшить рассеиваемую мощность при обычной работе и ввести особые режимы, снижающие энергопотребление.

80C51/FA/FB/FC – введен модуль PCA (программируемая вычислительная матрица) и сторожевой таймер WDT (обеспечивает перезагрузку процессора или зависание)

80С51 GB – встроенный АЦП

Состав МК:

-

8-разрядный процессор

-

Внутренняя ОЗУ 128Кб

-

Внутренняя ПЗУ 4 Кб

-

Два 16-разрядных таймера-счетчика, работающих в двух режимах

-

Счетчик – подсчитывает число импульсов, поступающих на его вход

-

Таймер – изменение и задание временных интервалов длительности импульсов

-

-

Четыре 8-разрядных порта ввода/вывода

-

Последовательный порт ввода/вывода

Структурная схема МК 8051 AH

Организация памяти МК 8051 AH

Организация памяти

Одной из основных особенностей однокристальных микроконтроллеров, отличающих их от других типов микропроцессорных БИС, является так называемая "гарвардская архитектура", при которой память программ и память данных физически и логически отделены друг от друга.

Память данных

Память данных, расположенная на кристалле (внутренняя память данных), имеет емкость 128 байт с адресами 00h-7Fh. Она может быть расширена до 64 Кбайт за счет подключения блоков внешней памяти данных.

Помимо возможности использования ОЗУ в качестве массива оперативной памяти, отдельные ее области имеют самостоятельное значение. Часть ОЗУ применяется в качестве регистров общего назначения, часть имеет прямоадресуемый доступ к отдельным битам, образуя так называемую битовую память. В ОЗУ располагается также и область стека.

Младшие 32 байта внутреннего ОЗУ данных сгруппированы в 4 банка по 8 регистров общего назначения в каждом (БАНК 0-БАНК 3). Определение рабочего в данный момент банка, то есть банка регистров, к которому обращается программа при использовании имен R0-R7, осуществляется установкой битов RS0 и RS1 в регистре слова состояния PSW.

ОЗУ данных с адресами 20h-2Fh образует область ячеек, к которым возможен побитный доступ. Система команд МК-51 содержит значительное количество инструкций, позволяющих работать с отдельными битами, используя при этом прямую адресацию. 128 бит, составляющие рассматриваемую область внутреннего ОЗУ данных, имеют адреса бит 00h-7Fh и предназначены для работы с такими инструкциями. Ячейки памяти с адресами 30h-7Fh используются как обычная оперативная память. Во внутреннем ОЗУ данных размещается также область стека. Ее положение не фиксировано, а определяется значением указателя стека SP. Адресное пространство внутренней памяти данных с адресами 80h-FFh отведено под указание регистров специальных функций микропроцессора. Область регистров специальных функций содержит регистры-защелки портов ввода-вывода, регистры таймеров/счетчиков, регистры управления и т. п. Эти регистры допускают только прямую адресацию. Все ячейки внутреннего ОЗУ данных могут адресоваться с использованием прямой и косвенной адресации. Обращение к регистрам специальных функций допускается с применением только прямой адресации. К внешней памяти данных можно обращаться только на запись или чтение с помощью специальных команд. Эти команды осуществляют обмен информацией между внешней памятью данных и аккумулятором микроконтроллера и не влияют на внутреннюю память данных МК. Таким образом, в системе могут одновременно присутствовать внутренняя память данных с адресами 00h-0Fh и внешняя память данных с адресами 0000h-FFFFh.

Память программ

В зависимости от модификации, различные типы БИС МК-51 имеют разное распределение внутренней и внешней памяти программ (см.табл. 14.1)), оставляя неизменной максимально допустимую общую емкость в 64 Кбайт. Память программ адресуется с помощью 16-разрядной адресной шины с использованием счетчика команд (program counter -PC), который вырабатывает 16-разрядные адреса. Она имеет байтовую организацию и доступна только для чтения.

Обращение к внутренней или внешней памяти программ происходит автоматически с применением аппаратных средств МК. При этом в зависимости от состояния управляющего входа DEMA микроконтроллера вся память трактуется либо как только внешняя (при DEMA = 0), либо как внутренняя, занимающая младшие адреса адресного пространства, и внешняя, занимающая адреса от старшего адреса внутренней памяти 8000h до максимально допустимого FFFFh. С точки зрения программиста имеется только один массив памяти программ емкостью 64 Кбайт.

Таймер-счетчик МК 8051 AH, устройство и режимы работы.

Два 16-разрядных таймера-счетчика: таймер 1 и таймер 0. Выбор режима работы таймер/счетчик производится битами C/TX (x=0 или 1) регистра TMOD (регистра режима)

|

GATE1 |

C/T1 |

M1.1 |

M1.0 |

GATE0 |

C/T0 |

M0.1 |

M0.0 |

GATEx – бит управления таймера x.

C/Tx – бит выбора режима работы.

Mx.0, Mx.1 – определяют режим работы таймера x.

TCON управляет режимом работы таймера-счетчика

|

TF1 |

TR1 |

TF0 |

TR0 |

IE1 |

IT1 |

IE0 |

IT0 |

TFx – флаг переноса таймера

TRx – бит запуска таймера

IEx – флаг запроса прерывания по входу INTx

ITx – бит выбора активного сигнала на входе

Работа таймеров-счетчиков

|

Mx.1 |

Mx.0 |

Режим |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

2 |

|

1 |

1 |

3 |

Система прерываний МК 8051 AH

Источники прерывания

-

Внешние (входы INT0, INT1)

-

Внутрение (два таймера счетчика и последовательный порт)

Адрес перехода соответствует вектору прерываний, т.е. адресу области памяти, куда передается управление.

По адресам может располагаться короткая процедура или команда JMP на область, где записана более длинная процедура.

|

Приоритет |

Источник |

Адрес |

|

Высший |

INT0 |

0003h |

|

|

Таймер 0 |

000Bh |

|

|

INT1 |

0013h |

|

|

Таймер 1 |

001Bh |

|

Низший |

Послед. порт |

0023h |

Когда запрос прерывания принят на обслуживание, то выполняется следующая последовательность действий:

-

Текущая команда выполняется до конца

-

Формируется внутренняя команда LCALL, которая сохраняет текущее значение счетчика команд PC в стеке. Это позволяет после завершения процедуры обслуживания прерываний вернуться в прерванную программу

-

LCALL загружает в счетчик PC адрес-вектор прерывания

-

Процедура обслуживания прерывания заканчивается процедурой RET

Обработка прерываний производится двумя регистрами

TE – регистр разрешения прерывания

|

EA |

- |

- |

ES |

ET1 |

EX1 |

ET0 |

EX0 |

ES – запрет прерывания от последовательного порта ввода/вывода

EA – от всех источников

ETx – от таймера x

EXx – от INTx

IP – регистр приоритетов прерываний

|

- |

- |

- |

PS |

PT1 |

PX1 |

PT0 |

PX0 |

PS – для последовательного порта

PTx – для таймера x

PXx – для INTx

Развитие семейства МК 8051 AH

8051 AH – первый МК, выполненный на основе динамических элементов. Требует постоянной подачи напряжения. При пропадании напряжения питания структура микросхемы разрушается.

80C51/52/54/58 – выполнены с использованием комплементарной MOS-технологии – позволяет уменьшить рассеиваемую мощность при обычной работе и ввести особые режимы, снижающие энергопотребление.

80C51/FA/FB/FC – введен модуль PCA (программируемая вычислительная матрица) и сторожевой таймер WDT (обеспечивает перезагрузку процессора или зависание)

80С51 GB – встроенный АЦП

Таймер счетчик T2 (режим работы)

Данные для перезагрузки хранятся в ргистрах PCAP2H (старший) и PCAP2L (младший). Управляется T2CON.

Режим работы:

-

Режим захвата текущего значения счетчика

-

Режим прямого счета с автоперезагрузкой исходного значения

-

Режим задающего генератора для последовательного порта

Развитие системы прерываний МК 8051 AH

Добавление нового регистра IPH

IP – регистр определения приоритета

|

- |

- |

PT2 |

PS |

PT1 |

PX1 |

PT0 |

PX0 |

IPH

|

- |

- |

PT2H |

PSH |

PT1H |

PX1H |

PT0H |

PX0H |

PTx – приоритет таймера x

PS – приоритет последовательного порта

PXx – приоритет входа INTx

IE – регистр разрешения запроса

|

EA |

- |

ET2 |

ES |

ET1 |

EX1 |

ET0 |

EX0 |

EA – запрещение запроса прерывания от всех источников

ETx – от таймера x

ES – от последовательного порта ввода/вывода

EXx – от входа INTx

Блок PCA (программируемая вычислительная матрица)

Состоит из 16-разрядного таймера-счетчика и 5 16-разрядных модулей фиксации сравнения. Таймер-счетчик является источником временной базы и счетчиком событий, значения его текущего отсчета передаются в модули фиксации сравнения.

Счетный регистр таймера счетчика состоит из пары регистров CH-CL, а значения зафиксированные модулями хранятся в 5 парах регистров CCAPxH-CCAPxL. Управление работой и режимами таймера-счетчика осуществляется при помощи регистра режима CMOD и регистра управления CCON.

CCON

|

CF |

CR |

- |

CCF4 |

CCF3 |

CCF2 |

CCF1 |

CCF0 |

CF – флаг переполнения PCA

CR – бит включения таймера счетчика PCA

CCFx – флаг прерывания модуля x

CMOD

|

CIDL |

WDTE |

- |

- |

- |

CPS1 |

CPS0 |

ECF |

CIDL – бит разрешения работы PCA в режиме Idle

WDTE – ф-ии сторожевого таймера модуля 4

CPSx – бит выбора источника синхросигнала

ECF – бит разрешения прерывания блока PCA

Методы повышения быстродействия ЭВМ (конвейер команд, суперконвейер)

Конвейеризация этапов машинного кода.

Машинный цикл – действие по извлечению данных из внешней памяти на выполнение.

Этапы цикла:

-

Выборка команды

-

Декодирование команды

-

Вычисление исполнительных адресов

-

Выборка операндов

-

Исполнение операции

-

Запись результата

-

Формирование адреса следующей команды

Если соединить все устройства, используемые на разных этапах, получится стандартный конвейер команд.

Возможны конфликтные ситуации, поэтому такого идеального конвейера не существует. Оптимизирующий компилятор пытается создать такой код, чтобы между конфликтными командами находилось несколько нейтральных команд.

Суперконвейер позволяет повысить производительность за счет повышения частоты, а команды подаются на конвейер и перемещаются по нему. Медленные ступени разделяются на более мелкие, чтобы быстрей обработать. Приводит к увеличению числа регистров в конвейере.

Методы повышения быстродействия ЭВМ (скалярный процессор)

Ввод в вычислительный процесс различных уровней параллелизма.

Скалярный процесс – процесс, выполняющий одновременно более одной скалярной команды.

В ЦП включаются несколько самостоятельных функциональных блоков, каждый из которых отвечает за свой класс операций и может присутствовать в процессоре в нескольких экземплярах. Суперскалярность предполагает параллельную работу нескольких скалярных блоков, что возможно при одновременном выполнении нескольких команд.

Выполняемая программа разбивается на 2 потока, осуществленных специальным компилятором. Потоки обрабатываются параллельно, но одним и тем же блоком.

Архитектура процессоров (процессоры CISK)

CISK – полный набор команд.

В данной архитектуре имеется отдельная машинная команда для каждого возможного действия по обработке данных.

Признаки:

-

Большое число различных машинных команд, каждая из которых выполняется за несколько тактов ЦП

-

Устройство управления с программируемой логикой

-

Небольшое количество РОН

-

Различные форматы команд с различной длиной

-

Преобладание 2х адресной адресации

-

Развитый механизм адресации операндов, включающих различные методы косвенной адресации

Некоторые команды стало невозможно выполнять чисто аппаратными средствами. Поэтому добавили блоки, заменяющие более сложные команды последовательностью простых.

Многие команды (сложные) оказались невостребованными. Из-за сложности команд (и их кол-ва) пришлось жертвовать наращиванием тактовой частоты в пользу медленной управляющей памяти.

Архитектура процессоров (процессоры RISK)

Усеченный набор команд.

Основные черты:

-

Построен максимальный эффект конвейера команд, где все команды извлекают из памяти и поступают в виде равномерного потока. При этом не одна из команд не должна «спать»

-

Стандартная длина команд равная ширине шины, соединенной ЦП с памятью

-

Простая система декодирования и управления.

-

В сокращенном списке должны остаться команды, которые используются наиболее часто.

Доступ к памяти и запись операндов занимает время больше чем один такт, поэтому доступ к памяти должен быть осуществлен командами чтения/записи, остальные должны иметь форму регистр-регистр.

RISK-концепция.

-

Выполнение всех или 75% команд за один цикл

-

Стандартная длина слова команд ровна ширине шины

-

Малое число команд

-

Малое число форматов команд

-

Доступ к памяти с помощью команд чтения/записи

-

Остальные используют внутрипроцессорные пересылки «регистр-регистр»

-

Устройство управления аппаратной логикой.

-

РОН > 32

Компилятор старается распределить регистры, чтобы записать в них переменные, использующиеся наиболее часто.

«+»:

-

Сравнительно простая структура устройства управления

-

Унификация набора команд

-

Унификация размера команд

-

Уменьшение времени ожидания в конвейере

-

Упрощена передача данных между процедурами

«-»:

-

Большое число регистров, усложняющих систему декодирования

-

Устройство управления менее гибко, более склонно к возникновению ошибок