2.4 Синтез комбинационных логических устройств

Комбинационным логическим устройством называется логическая схема, имеющая в общем случае n логических входов и m выходов, причем каждой комбинации сигналов на входе соответствует однозначная комбинация выходных сигналов (функций). Под это определение попадает целый ряд устройств, среди которых преобразователи кодов, мультиплексоры, сумматоры и ряд других, законы функционирования и принципы построения рассматриваются ниже.

Основными этапами разработки комбинационного устройства являются следующие:

1. Словесное описание закона функционирования разрабатываемого устройства, то есть объяснение его работы на понятийном уровне

2. На основании словесного описания составляется таблица истинности, в которой каждому набору переменных ставится в соответствие значение выходной функции. Если на некоторых наборах переменных функция оказывается недоопределенной, то ей можно придать любое значение, ориентируясь на оптимальную минимизацию выходной функции.

3. По составленной таблице истинности записывается аналитическое выражение выходной функции в СДНФ и помещается в клетки карты Карно

4. Проводится анализ карты Карно с целью выявления всех возможных склеиваний, и осуществляется запись минимизированной функции

5. Осуществляется схемотехническая реализация выходной функции в базисе выбранной серии элементов. Здесь полезно рассмотреть различные варианты и выбрать оптимальный с точки зрения эффективности и экономичности.

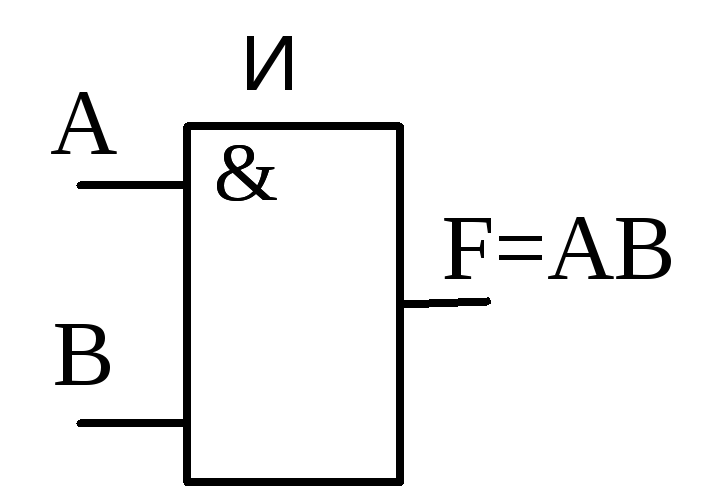

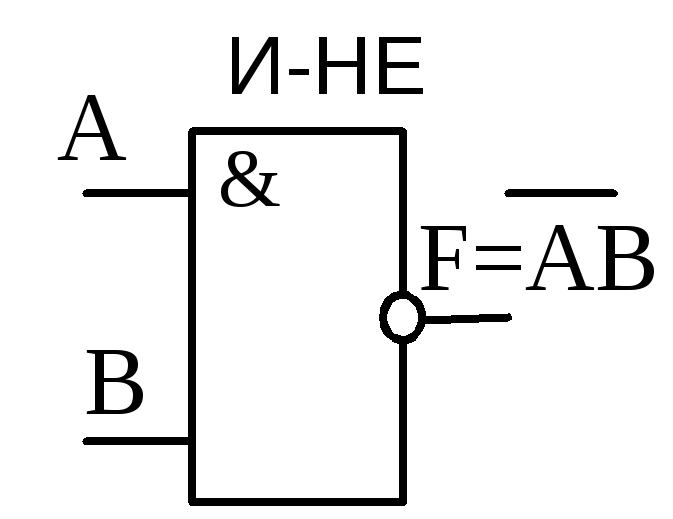

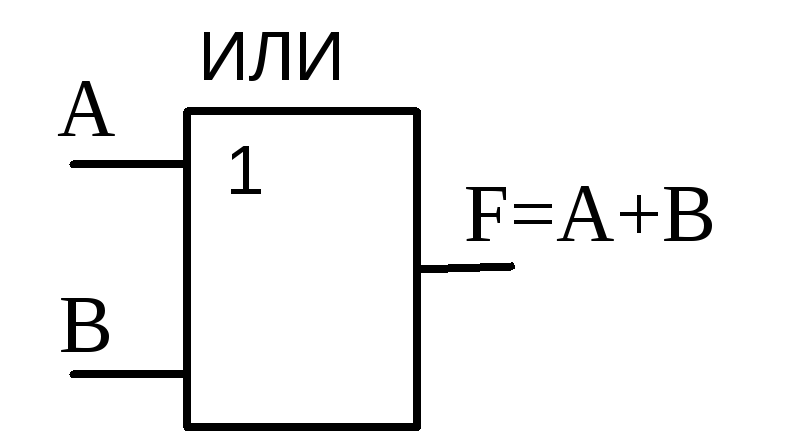

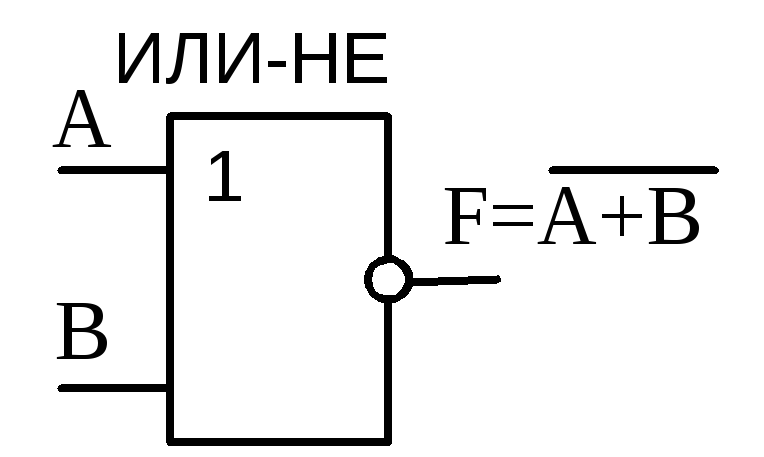

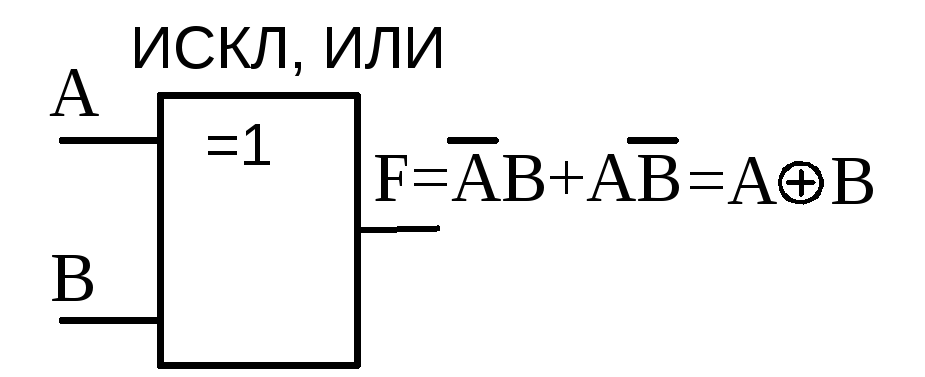

Для изображения логического устройства ознакомим читателя с условными обозначениями ряда типовых элементов, выполняющих простые логические функции (рис.2.8) и входящими в состав различных серий микросхем.

Рис. 2.8

2.4.1 Кодирующие устройства

Кодирующие устройства представляют собой логическую схему, преобразующую много разрядный входной код в выходной код, построенный по иному закону. Нередко алгоритм такого преобразования не поддается простому математическому описанию. Тогда наиболее эффективно использовать таблицу истинности, отражающую связь между входными и выходными сигналами и вытекающую из словесного описания работы устройства.

2.4.1.1 Дешифраторы

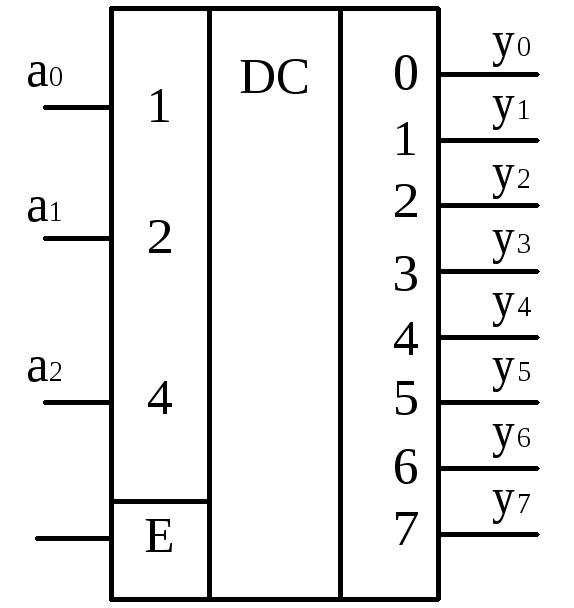

Дешифратором (декодером) называется кодирующее устройство, преобразующее двоичный код в унитарный. В общем случае дешифратор имеет n входов (по числу разрядов двоичной информации) и m выходов, из которых активным (единица или нуль) является только один, номер которого соответствует поданному на вход двоичному числу.

Рассмотрим задачу синтеза дешифратора, на вход которого подано трехразрядный двоичный код. Закон функционирования дешифратора отражен в таблице 2.10, а его условное обозначение показано на рис. 2.9.

Таблица 2.10

|

а0 |

а1 |

а2 |

y0 |

y1 |

y2 |

y3 |

y4 |

y5 |

y6 |

y7 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

З десь

через а0,

а1,

а2

обозначены разряды двоичного числа, а

y0……y7

представляют

выходные функции дешифратора. Каждая

из выходных функций принимает единичное

значение только на одном из наборов

входных переменных. Поэтому можно

записать:

десь

через а0,

а1,

а2

обозначены разряды двоичного числа, а

y0……y7

представляют

выходные функции дешифратора. Каждая

из выходных функций принимает единичное

значение только на одном из наборов

входных переменных. Поэтому можно

записать:

![]()

![]() …..

…..![]()

Таким образом выходные функции дешифратора являются минтермами Булевой функции и могут быть реализованы с помощью логических схем И, имеющих необходимое число входов. При

Рис. 2.9

этом каждая переменная должна представляться в прямой и инверсной форме.

Выходные сигналы дешифратора нередко представляются и в инверсном виде, что в ряде применений дешифратора оказывается весьма полезным при обработке цифровой информации.

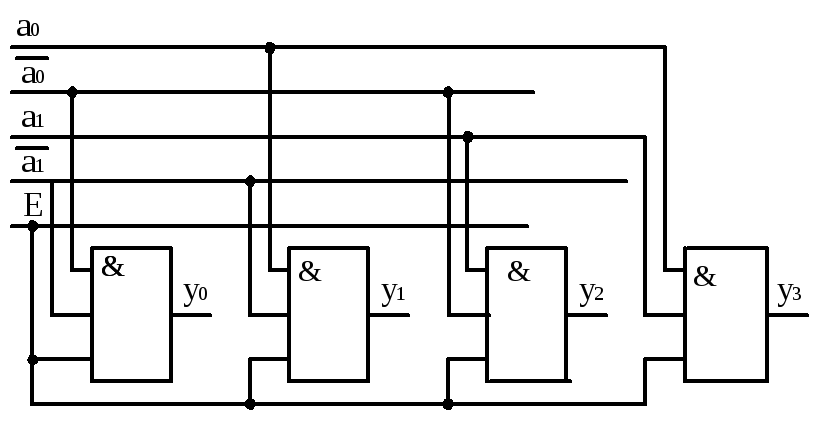

Вход Е дешифратора называется разрешающим. Только при подаче на него логической единицы (или нуля в зависимости от построения схемы разрешения) дешифратор переводится в активное состояние, как это иллюстрируется

Рис. 2.10

схемой рис. 2.10, представляющей преобразователь двухразрядного двоичного кода и состоящий из четырех логических схем И , на входы которых подаются разряды двоичного числа и сигнал разрешения Е.

По понятным причинам “рассыпные” интегральные дешифраторы могут обрабатывать двоичные числа с сравнительно небольшим числом разрядов. Наращивание дешифрирующих способностей достигается путем разделения разрядов двоичного числа на группы и использования каскадного включения дешифраторов меньшей разрядности, позволяющих дешифрировать каждую из групп. Например, пусть требуется создать полный дешифратор пятиразрядного двоичного числа, а в нашем распоряжении имеются только трехразрядные и двухразрядные дешифраторы. Тогда поступаем следующим образом:

1. Создаем две группы разрядов: из двух старших разрядов и трех младших разрядов

2. Проводим дешифрацию старших разрядов, используя один двухразрядный дешифратор. На выходе последнего организуются четыре минтерма , аргументами которых являются два старших разряда

3. На входы четырех трехразрядных дешифраторов подаем младшие разряды

4. Разрешающие входы трехразрядных дешифраторов связываем с выходами дешифратора старших разрядов.

Читателю полезно самостоятельно убедиться, что активное состояние каждого из выходов трехразрядных дешифраторов (в сумме их 32) действительно соответствует значению пятиразрядного двоичного числа.

Дешифраторы могут быть неполными и реализовать число минтермов m<2n. Такие дешифраторы используются, например, для преобразования двоично-десятичного кода в код для управления десятичным индикатором.

Области применения дешифраторов достаточно широки. Здесь прежде всего назовем такие, как создание системы адресов устройств обработки цифровой информации, устройства распределения импульсных последовательностей.

В заключение назовем некоторые микросхемы, выполняющие функции дешифратора. Это микросхема типа типа К155ИД4 (сдвоенный дешифратор двухразрядного двоичного кода), К555ИД10 (дешифратор двоичного кода в двоично-десятичный с инверсными выходами), 564ИД (дешифратор двоичного кода в двоично-десятичный или в восьмеричный).