- •Микропроцессоры мп 8086/8088 фирмы

- •Intel (1979 г.) Особенности структуры, способов адресации, режимы работы.

- •Мп Intel 8086

- •Организация системы шин l, s, m, X в мп 80281

- •Система команд

- •Умножение чисел в машинах:

- •Мп Intel 80286, Intel 80386, Intel 80486, Pentium.

- •Принципы архитектуры мп 80286

- •Принципы архитектуры мп 80386

- •Принципы архитектуры мп 80486

- •Принципы архитектуры мп Pentium (Intel)

Микропроцессоры мп 8086/8088 фирмы

Intel (1979 г.) Особенности структуры, способов адресации, режимы работы.

МП выполняет основные операции по управлению работой системы (интерпретация и формирование команд, форматирование данных, управление обменом с памятью и шиной), а также операции вычисления.

Сопроцессор служит ему помощником при выполнении операций над числами с плавающей запятой.

Процессор может работать без сопроцессора, а сопроцессор без процессора – нет.

Сопроцессор может использоваться только в том случае, когда рабочая программа использует специальные обращения к нему.

(МП – четные → 80286, СП – нечетные → 80287).

Мп Intel 8086

Конструктивной основой этого 16-разрядного МП служит МП 8080, однако, непосредственная совместимость с МП 8080 не обеспечивается.

В МП 8086 существует возможность прямой адресации до 1 Мбайт памяти со страничной организацией. Особенностью этого МП является его способность к предварительной выборке из памяти до 6 байт команд и организации очереди, обеспечивающей ускорение их выполнения.

Семейство 8086 включает в себя два типа 16-разрядных МП: 8086 и 8080. Они различаются по способу взаимодействия с внешней средой.

В процессоре 8086 для этого предусмотрен 8-разрядный тракт передачи внешних данных. В остальном оба процессора идентичны, программы написанные для одного из них, могут без каких-либо изменений выполняться на другом. Поэтому рассмотрим только МП 8086.

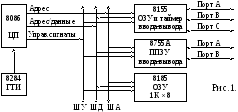

Это МП может быть использован в составе однопроцессорной системы с минимальным объемом памяти (рис. 1.), или входить в многопроцессорную систему, обеспечивающую возможность адресации до 1 Мбайт памяти.

Шина управленияформируется сигналами, поступающими непосредственно от МП, сигналами от шинного контроллера, а также сигналами, идущими от других МК схем и периферийных адаптеров.

Шинный

контроллерформирует управляющие

сигналы, определяющие перенос данных

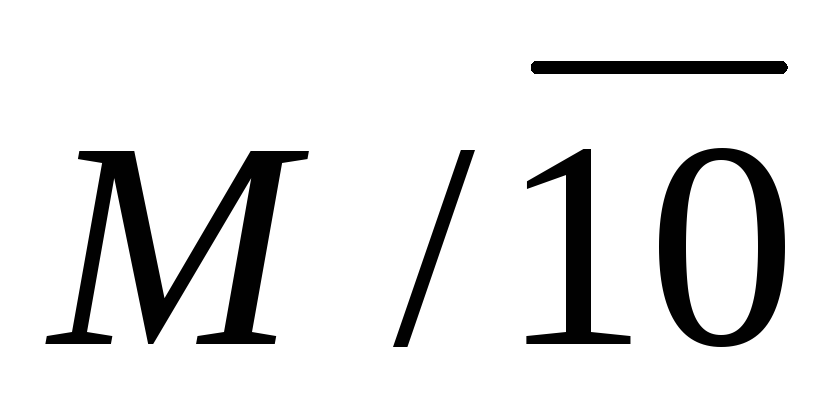

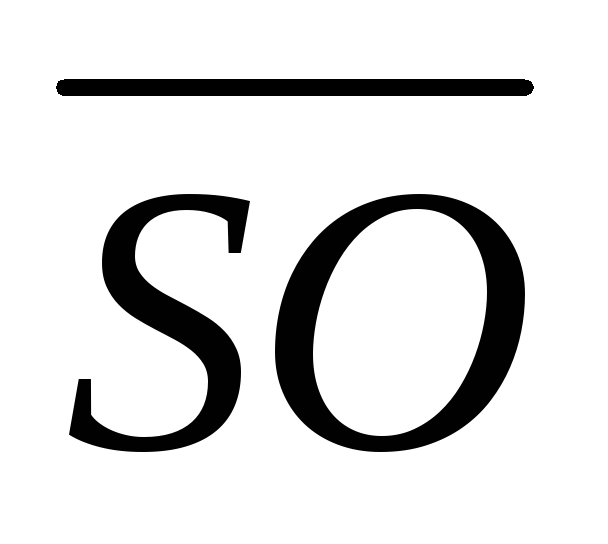

по шине. Он выставляет 3 сигналаSO;SI,M/10, которые

определяют тип цикла шины (подтверждение

прерывания, чтение порта в/в, запись в

порт, останов, чтение памяти, запись в

память).

Шинный

контроллерформирует управляющие

сигналы, определяющие перенос данных

по шине. Он выставляет 3 сигналаSO;SI,M/10, которые

определяют тип цикла шины (подтверждение

прерывания, чтение порта в/в, запись в

порт, останов, чтение памяти, запись в

память).

-

Тип цикла шины

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

Подтверждение прерывания

Чтение из порта в/в

Запись в порт в/в

если А1=1 – останов, иначе выключение

Чтение данных из ОЗУ

Запись данных в ОЗУ

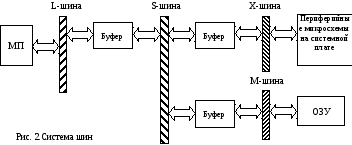

Организация системы шин l, s, m, X в мп 80281

S-шина – системная шина, она связывает компьютер в единое целое. Она основная (здесь осуществляется подключение периферийных адаптеров – дисплея, мыши, дисковода и т.д.).

L-шину образуют линии адреса.

Передача адреса на S-шину производится через буферы-защелки (эти резисторы в случае необходимости разъединяютL-шину иS-шину (при прямом доступе к памяти).

к Х-шине подключаются все микросхемы кроме процессора и СП (сопроцессор), также через буферы.

М-шина служит для отделения S-шины от ОЗУ.

Набор регистров в МП 80286 в сравнении с 8086 расширен на 5 (14+5=18).

Процессор 8086 имеет внутреннюю 16-разрядную шину данных с конвейерной архитектурой. Это позволяет осуществлять предварительную выборку команд в незанятые циклы обращения к шине. В сочетании с более плотным форматом команд. Это обеспечивает возможность предварительной выборки большего их числа в течение заданного времени, увеличивая производительность МП 8086.

МП включает в себя аппаратные средства, предназначенные для организации выполнения программ, написанных на языках высокого уровня ПЛ и Паскаль. Системные программы, для которых важно высокое быстродействие, не обеспечиваемое этими языками, могут писаться в кодах ассемблера, а затем связываться с программой на языке высокого уровня.

ИБ – исполнительный блок;

БИШ – блок интерфейса шины;

РОН – регистры общего назначения;

АЛУ – арифметико-логическое устройство;

В упрощенном виде последовательность события, происходящих в МП при выполнении программы:

Выборка очередной команды из памяти;

Чтение операнда;

Исполнение команды;

Запись результата.

Шаги выполнения распределяются между различными внутренними блоками обработки данных. Исполнение команд возлагается на ИБ, выборка команд чтение и запись результата осуществляет блок интерфейса шины БИШ.

Оба блока работают независимо друг от друга. ИБ исполняет команды, которые уже предварительно выбраны из ЗУ посредством БИШ, поэтому время выборки команд существенно сокращается.

АЛУ – 16-разрядное следит за флажками состояния и управляющими флажками ЦП, манипулирует РОН, выполняет различные действия над операндами команд.

В ИБ восемь 16-разрядных регистров, объединенных в две группы по 4 в каждый.

|

AX |

AH |

AL |

Аккумулятор |

SP |

Указатель стека |

|

BX |

BH |

BL |

Индексный регистр |

BP |

Указатель базы |

|

CX |

CH |

CL |

Счетчик |

SI |

Индекс источника |

|

DX |

DH |

DL |

Регистр данных |

DI |

Индекс приемника |

2х8 разрядных или

1х16 разрядных

Рис. 4. Структура регистров

1-ая группа H и L – регистры данных;

2-ая группа P и I – регистры указателей индексные.

SP – (УС) содержит текущий адрес стека

BP – (УБ) указатель базы используется при обеспечении МП и памяти.

SI и DI – индексные регистры участвуют в операциях индексной адресации.

Все восемь регистров могут использоваться как единый блок – накопительный регистр АК.

БИШ содержит 4х16-разрядных РА сегмента и 1 указатель команд. Все пространство памяти емкостью 1Мбайт разделено на сегменты по 64 Кбайт.

Обеспечивается прямой доступ ЦП сразу четырем таким сегментам

|

IP |

Указатель команды |

|

FLAGS |

Флажки состояния |

|

|

|

|

CS |

Кодовый сегмент |

|

DS |

Информационный сегмент |

|

SS |

Стековой сегмент |

|

ES |

Добавочный сегмент |

Рис. 5. Структура сегментов

Рис. 4 и рис. 5 => архитектура регистров МП 8086.

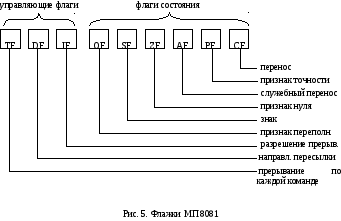

В МП 8086 предусматриваются в однобитовых флагов состояния (рис 6.), которые выставляются или сбрасываются ИБ и сигнализируют об определенных свойствах результатов арифметических и логических операций. Имеются еще 3 дополнительных управляющих флага, выставляя или сбрасывая, которые программы могут изменять ход выполнения операций процессором.

Две области памяти с самыми младшими (00H– 7FH, 128 байт) и самыми старшими адресами (FFFFFO-FFFFFH) предназначены для обработки сигналов (16 байт) прерываний и начального запуска вычислительной системы. Если они заняты, тот система становится несовместима с будущими изделиями фирмыIntel.

Способы адресации:

прямая адресация, регистровая косвенная, относительная, индексная, строковая.