Комп тех и сети / Литература / Шарапов_Микроэлектроника. Цифровая схемотехника

.pdf

131

9 КОМПЬЮТЕРНЫЙ ПРАКТИКУМ ПО ЦИФРОВОЙ СХЕМОТЕХНИКЕ

Лабораторная работа № 1

ИССЛЕДОВАНИЕ ЦИФРОВЫХ УСТРОЙСТВ КОМБИНАЦИОННОГО ТИПА

Цель работы. Цель лабораторной работы — приобретение навыков построения и испытания цифровых устройств комбинационного типа с использованием пакета ASIMEC. Программа моделирует лабораторный стол с наборным полем для макетирования цифровых схем и необходимым комплектом контрольноиспытательной аппаратуры.

Рис. 1 — Цифровые компоненты

Рис. 2 — Средства отображения информации

132

Используемые в данной лабораторной работе цифровые компоненты (логические элементы, полусумматор, полный одноразрядный сумматор) приведены на рис. 1. Генератор прямоугольных импульсов, формирователи уровней логического 0 и 1, пробник, цифровой индикатор и двухлучевой осциллограф для отображения цифровых сигналов представлены на рис. 2.

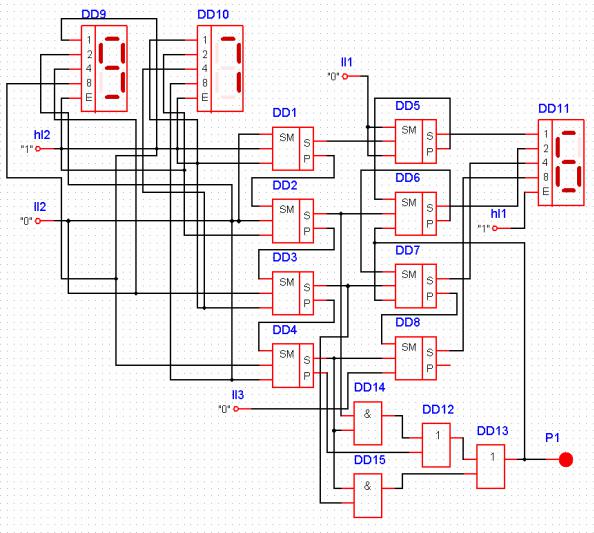

Рис. 3 — Сумматор двоично-десятичных чисел

На рис. 3 приведена схема моделирования на ASIMEC сумматора двоично-десятичных кодов чисел. Для сложения двух двоично-десятичных чисел можно использовать по одному четырехразрядному сумматору на каждую декаду. Однако после суммирования следует производить коррекцию. Если в какой-либо декаде происходит перенос или получается двоичное число, большее 9, необходимо добавлять к ней 6, чтобы компенсировать

133

разницу в весах разрядов. Возникающая при этом единица переноса передается в следующую по старшинству декаду.

В данном примере при сложении кодов чисел 9 и 7 на выходах DD1–DD4 сформировался двоичный код числа 16 (единица переноса в пятом разряде и нули на выходах первых четырех разрядов). Цепь коррекции (DD5–DD8, DD12–DD15) добавила число 6 к двоичной сумме чисел, и мы наблюдаем на индикаторах Р1 и DD11 правильный результат.

Программа работы

1.Исследовать работу цифрового индикатора, подавая различные сочетания уровней цифровых сигналов на его входы. Какой уровень разрешает его работу? В каком диапазоне меняются числа на индикаторе? Что будет, если хотя бы один вход оставить неподключенным?

2.Экспериментально снять таблицу истинности для устройства, выполненного по схеме рис. 4, изменяя уровни сигналов на входах А и В. Записать логическую функцию F и показать возможность упрощения устройства.

Рис. 4 — Устройство на логических элементах

3. Реализовать на логических элементах полный одноразрядный сумматор и убедиться в правильности его функционирования. С использованием полных одноразрядных сумматоров построить сигнальное устройство, формирующее на выходе логиче-

134

скую 1, если на любые N входов из 7 поданы логические 1 (для восьмого варианта N = 0).

4. Спроектировать устройство на логических элементах по заданной таблице истинности и проверить его работу экспериментально. Номер варианта (функцию F1…F8) рассчитывают по обычной для ТМЦ ДО методике.

N |

A |

B |

C |

F1 |

F2 |

F3 |

F4 |

F5 |

F6 |

F7 |

F8 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

2 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

3 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

4 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

5 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

6 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

7 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

Вариант 1 |

|

Вариант 2 |

|

|

Вариант 3 |

|

|

|

Вариант 4 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DMS |

|

|

|

|

|

|

= = |

|

|

|

|

= = |

|

||

|

|

0 |

MS |

|

4 |

|

4 |

|

|||||||

2 |

0 |

|

1 |

|

|

|

A |

|

|

A |

|

||||

|

|

|

/ |

|

A= |

/ |

|

|

|||||||

1 |

1 |

|

2 |

|

|

4 |

|

|

4 |

|

|

A> |

|

||

|

2 |

|

3 |

|

|

/ |

|

B |

|

/ |

|

B |

|

||

E |

3 |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

Вариант 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DС |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

Вариант 6 |

|

|

Вариант 7 |

|

|

|

Вариант 8 |

|||||

4 |

2 |

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

3 |

/ |

DI |

MS |

|

3 |

|

SM |

1 |

|

4 |

|

= = |

|

|

1 |

4 |

|

|

|

|

|

A |

2 |

|

|

A |

||||

|

4 |

|

|

/ |

|

|

/ |

|

|||||||

|

5 |

|

|

|

3 |

|

|

4 |

|

4 |

|

A< |

|||

|

6 |

|

2 |

|

|

/ |

|

B |

8 |

|

/ |

|

B |

||

|

7 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 5 — Варианты цифровых устройств

135

5. На заданной элементной базе построить комбинационное цифровое устройство (рис. 5). Собрать устройство на макетном поле. Разработать программу проведения эксперимента по его испытанию. Провести эксперимент и зафиксировать его результаты.

6.Испытать счетный триггер, реализовав его на D-триггере

сдинамическим тактовым входом (рис. 6). Масштаб времени при моделировании в реальном времени принимается равным 1.

G |

D T |

C |

Рис. 6 — Счетный триггер Т

7. На четырех Т-триггерах построить четырехразрядный асинхронный двоичный счетчик, формирующий сигналы A, B, C, D при счете импульсов задающего генератора G (рис. 7), и проверить его работу с помощью осциллографа. Оценить частоту импульсов на выходах G, A, B, C, D.

|

|

|

CT2 |

1 |

D |

|

|

|

|

|

C |

|

|

||

|

|

|

|

2 |

Комбинационное |

|

|

|

|

|

|

B |

|

||

|

|

|

|

4 |

устройство |

|

|

G |

|

|

|

|

|||

|

|

|

A |

|

|||

|

+1 |

|

8 |

|

|

||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 7 — Функциональная схема проектируемого устройства

8. Спроектировать генератор импульсов по заданной временной диаграмме его сигнала в течение периода на 16 тактах (рис. 8). Выбирается один из 10 вариантов исходных данных. Время одного такта — 1 мс.

|

|

|

|

|

|

|

|

|

|

|

|

136 |

|

|

|

|

|

|

|

|

|

|

|

|

||

D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Т = 16 мс |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

N |

|

|

0 |

1 |

2 |

3 |

4 |

5 |

6 |

|

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

|

||||||

|

|

|

||||||||||||||||||||||||

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

0 |

|

|

|

2 |

|

|

|

5 |

|

|

|

|

|

9 |

|

|

|

|

|

|

14 |

15 |

|

||

|

1 |

|

3 |

4 |

|

6 |

|

7 |

8 |

|

|

10 |

11 |

12 |

13 |

|

|

|||||||||

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

0 |

|

|

|

2 |

|

|

|

5 |

|

|

7 |

8 |

|

|

|

10 |

|

12 |

13 |

14 |

15 |

|

|||

|

1 |

|

3 |

4 |

|

6 |

|

|

9 |

|

11 |

|

||||||||||||||

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

|

|

|

1 |

|

|

|

4 |

|

|

|

|

|

8 |

|

|

|

|

|

13 |

|

|

15 |

|

||

|

|

0 |

|

|

2 |

3 |

|

5 |

6 |

|

7 |

|

9 |

10 |

11 |

12 |

|

14 |

|

|||||||

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 8 — Варианты заданий

Проектируемый генератор (рис. 7) содержит четырехразрядный двоичный счетчик с тактовым генератором G и комбинационное устройство, формирующее заданный сигнал из выходных сигналов счетчика A, B, C, D. Выходной сигнал генератора описывается логической функцией F.

9. По заданной временной диаграмме сигнала на выходе проектируемого генератора заполнить карту Карно и записать минимизированное выражение для булевой функции F, реализуемой комбинационной частью устройства.

137

10. Собрать полную схему генератора и проверить его работу, подключив осциллограф к выходу устройства. Соответствует ли полученная временная диаграмма выходного сигнала генератора заданной? Устранить ошибки в проектировании устройства, если выходной сигнал отличается от заданного.

Контрольные вопросы

•Перечислить основные законы булевой алгебры. Какой закон описывает формула де Моргана?

•С помощью диаграмм Венна доказать логическое тождество

ab +a b = ab +ab .

•Дайте определение дешифратору, мультиплексору, сумматору, демультиплексору, цифровому компаратору.

•С какой целью проводится минимизация логических функций.

•В чем вы видите достоинства представления чисел со знаком в дополнительном коде? Запишите результат сложения дополнительных кодов чисел плюс 80 и минус 33. Каждое число отображается байтом.

•Какие коды может сравнивать цифровой компаратор? Запишите возможные варианты функций сравнения.

•Как построить восьмиразрядный цифровой компаратор из двух микросхем К555СП1?

Содержание отчета

Отчет в формате Word должен содержать схемы исследуемых узлов, основные экспериментальные данные (вставки из ASIMEC), выводы по пунктам программы работы, а также ответы на контрольные вопросы.

138

Лабораторная работа № 2

ИССЛЕДОВАНИЕ ЦИФРОВЫХ УСТРОЙСТВ ПОСЛЕДОВАТЕЛЬНОСТНОГО ТИПА

Цель работы. Цель лабораторной работы — проектирование и экспериментальная проверка работы синхронных счетчиков с заданной последовательностью смены состояний, а также анализ работы счетчиков на регистрах сдвига. Используется моделирующий пакет ASIMEC. Программа моделирует лабораторный стол с наборным полем для макетирования цифровых схем и необходимым комплектом контрольно-испытательной аппаратуры.

Пример синтеза счетчика

Пусть стоит задача спроектировать вычитающий двоичный счетчик с коэффициентом пересчета Ксч = 6. Для фиксации шести состояний счетчика возьмем три тактируемых по положительному фронту D-триггера, объединенные входы синхронизации которых будем использовать как счетный вход счетчика (рис. 1). Будем характеризовать состояние счетчика N трехразрядным двоичным словом Q3Q2Q1 (N должно циклически меняться от 5 до 0).

|

D |

T |

Q1 |

|

D1 |

|

C |

|

Q2 |

Логика |

D2 |

|

D |

T |

|||

|

C |

|

Q3 |

переходов |

D3 |

G |

D |

T |

|

||

|

|

|

|||

C |

|

|

|

|

|

|

|

|

|

|

Рис. 1 — Функциональная схема счетчика

Каждый импульс генератора G переписывает на выходы триггеров Q1, Q2, Q3 информацию с входов D1, D2, D3. Поэтому дальнейший синтез счетчика сводится к построению комбинационной схемы (логики переходов), формирующей из выходных

139

сигналов Q уровни сигналов D на информационных входах триггеров, необходимые для перехода в следующее состояние. Для этого составим таблицу переходов (табл. 1) и запишем логические выражения для сигналов D1, D2, D3 в ДНФ (дизъюнктивной нормальной форме):

D1 = Q3 |

Q2 |

|

|

|

Q1 |

+ |

Q3 |

|

|

Q2 |

Q1 |

+ |

Q3 |

|

Q2 |

|

Q1 |

; |

(1) |

||||||||||

D2 |

= Q3 |

|

|

|

|

+ |

|

|

|

Q2 Q1 ; |

(2) |

||||||||||||||||||

Q2 |

Q1 |

Q3 |

|||||||||||||||||||||||||||

D3 |

= Q3 |

|

Q1 + |

|

|

|

|

|

. |

(3) |

|||||||||||||||||||

Q2 |

Q3 |

Q2 |

Q1 |

||||||||||||||||||||||||||

Для минимизации логических функций можно воспользоваться основными законами булевой алгебры или картами Карно (рис. 2), причем в клетках, соответствующих шестому и седьмому состоянию счетчика, логические функции можно доопределять по собственному усмотрению, так как в схеме проектируемого счетчика они не реализуются.

По картам Карно запишем минимизированные выражения для функций D1 и D2

D1 = |

Q1 |

; |

|

|

(4) |

D2 =Q3 |

|

1 +Q2 Q1 . |

(5) |

||

Q |

|||||

Выражение для D3 получим путем преобразования соотношения (3), так как карта Карно не позволяет провести эффективную минимизацию этой функции

D3 = |

Q2 |

|

Q1 Q3 |

. |

(6) |

С учетом соотношений (4), (5) и (6) построена схема эксперимента по изучению работы счетчика (рис. 3). Счетные импульсы снимаются с выхода тактового генератора G. Индикация состояний счетчика производится с помощью элемента DD9, выполняющего функцию преобразования четырехразрядного дво-

140

ичного числа в его шестнадцатеричный эквивалент на семисегментном индикаторе. Удобно выбрать частоту генератора равной

1 Гц.

Таблица 1

Текущее состояние счетчика N |

Последующее состояние счетчика N+ |

||||||

|

|

|

|

|

|

|

|

N |

Q3 |

Q2 |

Q1 |

N+ |

D3 |

D2 |

D1 |

5 |

1 |

0 |

1 |

4 |

1 |

0 |

0 |

4 |

1 |

0 |

0 |

3 |

0 |

1 |

1 |

3 |

0 |

1 |

1 |

2 |

0 |

1 |

0 |

2 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

5 |

1 |

0 |

1 |

D1 Q3 D2 Q3 D3 Q3

Q1 |

1 |

1 |

X |

1 |

Q1 |

0 |

0 |

X |

1 |

Q1 |

1 |

0 |

X |

0 |

0 |

0 |

X |

0 |

0 |

1 |

X |

0 |

0 |

0 |

X |

1 |

|||

|

|

Q2 |

|

|

|

|

Q2 |

|

|

|

|

Q2 |

|

|

Рис. 2 — Карты Карно для функций D1, D2, D3

Рис. 3 — Синхронный вычитающий счетчик с Ксч = 6