ЦМПУ / Новая папка / Лаб6ЦМПУ

.docxЛабораторная работа №6 «Изучение портов ввода/вывода и их программирование»

Цель работы: Изучение функционирования и организация работы портов ввода/вывода микроконтроллера ATmega128.

Порядок выполнения лабораторной работы на симуляторе

-

Запустить симулятор VMLAB 3.12.

-

Создать новый проект с именем “Project6.prj”.

-

В окно кодов ввести листинг программы №6.

-

В окно файла проекта ввести листинг проектного файла №6.

-

Отладить программу командой Project/Build (F9).

-

Перейти в окно памяти программ через меню View/Program Memory (Alt+Shift+G).

-

Выполнить программу в пошаговом режиме командой Run/Step into (F7).

-

Просмотреть изменение состояния регистров (Alt+Shift+R), портов ввода-вывода, указателя стека (SPL, SPH) и указателя адреса PC (Alt+Shift+I).

-

В окне осциллографа View/Scope (Alt+Shift+S) пронаблюдать изменение сигналов.

-

В ходе выполнения программы, при достижении метки m2, на панели управления нажать кнопку «0» и продолжать выполнение программы в пошаговом режиме командой Run/Step into (F7).

-

В окне осциллографа пронаблюдать изменения сигналов на выводах РВ0, РВ1, РВ2, РВ3.

-

В соответствии с предложенными вариантами (табл. 6.28) выполнить задание. Повторить п.п. 2 – 11.

-

Для сохранения проекта выполнить команду File/Save all.

-

Для выхода из среды разработки VMLAB 3.12 выполнить команды File/Exit (Alt+F4).

Задание Организовать поступление в порт В последовательности сигналов: 25, 17, 32, 16, 11, 4, 42 с коэффициентом деления 3; в порт С подать сигналы: 120, 16.

Листинг программы №6

; BASIC .ASM template file for AVR

; ******************************************************

; Define here the variables

;

.include "C:\VMLAB\include\m128def.inc""; определение библиотеки МК ;ATmega128, при условии расположения программы VMLAB на ;локальном диске С

;Инициализация переменных

.def temp =r16 ; Изменяемое значение

.def delit =r16 ; Коэффициент деления

.def temp1 =r17 ; Изменяемое значение

.def vhod =r17 ; Делимое

.def temp2 =r18 ; Изменяемое значение

.def dcnt =r18 ; Счетчик

.def cnt =r19 ; Счетчик

.def ostat =r19 ; Остаток

.def per =r20 ; Переменная выхода

.def dey =r21 ; Переменная задержки

; Основная программа

.ORG $0 ; Начало таблицы переходов

Reset:

rjmp start ; Переход на начало основной программы

reti ; Addr $01

reti ; Addr $02

reti ; Addr $03 Вектора прерываний МК ATmega128.

reti ; Addr $04 Приведены вектора с адреса $01 по адрес $10.

reti ; Addr $05 Полностью вектора прерываний представлены

reti ; Addr $06 в приложении с назначением прерываний

reti ; Addr $07 (внешних и внутренних).

reti ; Addr $08

reti ; Addr $09

reti ; Addr $0A

reti ; Addr $0B

reti ; Addr $0C

reti ; Addr $0D

reti ; Addr $0E

reti ; Addr $0F

reti ; Addr $10

.ORG $02 ; Вектор от внешнего прерывания INT0

rjmp Prer ; Переход на обработку внешнего прерывания

.ORG $10 ; Начальный адрес основной программы

start:

clr temp1 ; Очистка регистров

clr temp

clr temp2

clr cnt

clr per

ldi temp,$10 ; Инициализация стека

out SPH,temp

ldi temp,$E8 ; Инициализация стека

out SPL,temp

out DDRB,temp2 ; Настройка порта В на вход

cbi DDRD,0 ; Настройка канала порта D PD0 на вход

ldi temp,$39

out EIMSK,temp ; Установка флага разрешения внешнего ;прерывания

ldi temp,$35

out MCUCR,temp ; Условие генерации внешнего прерывания

; (по низкому уровню на выводе INT0)

ldi cnt,8 ; Загрузка количества значений, принимаемых в порт ;В

clr temp1 ; Очистка регистра

sei ; Разрешить все прерывания

; Ожидание внешнего прерывания

m2: tst vhod ; Проверка регистра на нулевое значение

brne Delenie ; Переход, если значение регистра не нуль

rjmp m2

Delenie: ldi delit,3 ; Загрузка значения коэффициента деления

sub ostat,ostat ; Очистить остаток и перенос

ldi dcnt,9 ; Инициализировать счетчик цикла

d8u_1: rol vhod ; Делимое/результат сдвинуть влево

dec dcnt ; Уменьшить на единицу счетчик цикла

brne d8u_2 ; Переход, если не ноль

rjmp m3 ; Выход из подпрограммы

d8u_2: rol ostat ; Остаток сдвинуть влево

sub ostat,delit ; Остаток = остаток - коэффициент деления

brcc d8u_3 ; Если результат < 0,

add ostat,delit ; восстановить остаток

clc ; Сбросить перенос для формирования результата

rjmp d8u_1 ; иначе

d8u_3: sec ; установить перенос для формирования результата

rjmp d8u_1 ; Вернуться назад

m3: ldi temp,$3f ; Настройка порта С на выход

out DDRC,temp

out PORTC,vhod ; Вывод сигнала в порт С

rcall Delay ; Вызов процедуры задержки

inc vhod ; инкремент переменной vhod

out PORTC,vhod ; Вывод сигнала в порт С

ldi per,120

rcall P_peres

ldi per,16

rcall P_peres

rjmp finish

; Процедура обработки внешнего прерывания

Prer:

m1: in temp2,PINB ; Опрос порта В

add temp1,temp2 ; Сложение регистров

dec cnt ; Уменьшение счетчика на один

brne m1 ; Переход, если не нуль

ret ; Возврат из процедуры

; Процедура последовательной пересылки в канал порта С PC0

P_peres: ldi cnt,$8 ; Загрузка счетчика пересылаемых бит

r1: rol per ; Сдвигаем per влево с переносом, чтобы

; определить "0" или "1"

brcs p1 ; Если бит равен "1", то переход на метку p1

cbi PORTC,0 ; Если бит равен "0", то вывод "0" в PC0

sbic PORTC,0 ; Пропуск, если бит равен "0"

p1:sbi PORTC,0 ; Если бит равен "1", то вывод "1" в PC0

r3:dec cnt ; Декремент счетчика

brne r1 ; Если не равно нулю, то переход на r1

ret ; Выход из процедуры

; Процедура задержки

Delay:

ldi dey,$5 ; Временная задержка на 5,5 мкс

d1: dec dey

brne d1

ret ; Выход из процедуры

finish:

.exit

Листинг проектного файла №6

.MICRO "ATmega128" ; Указание типа микроконтроллера (ATmega128)

.PROGRAM "port.asm" ; Ассемблируемый файл

.TARGET "port.hex" ; Файл машинного кода

.TRACE ; Включение трассировки

.POWER VDD=5 VSS=0 ; Power nodes

.CLOCK 4meg ; Micro clock

.STORE 250m ; Trace (micro+signals) storage time

K0 pd0 GND ; Подключение ключа между PD0 и "землей"

P0 NRZ(1.25u) pb0 KEY_0 "11111100" ; Генерация сигнала на вход PB0

P1 NRZ(1.25u) pb1 KEY_0 "10000000" ; Генерация сигнала на вход PB1

P2 NRZ(1.25u) pb2 KEY_0 "00001000" ; Генерация сигнала на вход PB2

P3 NRZ(1.25u) pb3 KEY_0 "00001000" ; Генерация сигнала на вход PB3

P4 NRZ(1.25u) pb4 KEY_0 "11000000" ; Генерация сигнала на вход PB4

P5 NRZ(1.25u) pb5 KEY_0 "00000000" ; Генерация сигнала на вход PB5

P6 NRZ(1.25u) pb6 KEY_0 "00000000" ; Генерация сигнала на вход PB5

P7 NRZ(1.25u) pb7 KEY_0 "00000000" ; Генерация сигнала на вход PB5

.PLOT v(pd2)v(pb0)v(pb1)v(pb2)v(pb3)v(pc5) v(pc4)v(pc3)v(pc2)v(pc1)v(pc0)

; Вывод на осциллограф сигналов с каналов портов PB0, PB1, PB2, PB3, ;PD2, PC5, РС4, РС3, РС2, РС1, РС0

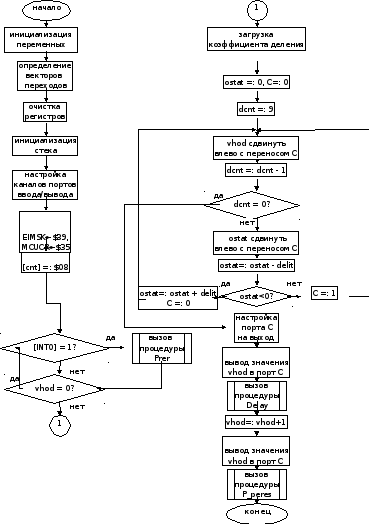

Рис.

6.9 Алгоритм

программы организации работы с портами

ввода/вывода