Лекция 9.

I Комбинационные логические схемы

Комбинационные схемы (преобразователи кодов) предназначены для преобразования n-разрядного параллельного двоичного кода на входе в m-разрядный код на выходе. Связь между входными и выходными сигналами можно задать таблицами истинности или логическими функциями. Рассмотрим наиболее распространенные виды преобразователей кодов.

9.1. Шифратор

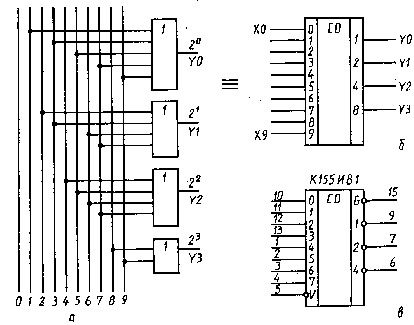

Шифратор (кодер) преобразует единичный сигнал на одном из входов в n-разрядный двоичный код. Наибольшее применение он находит в устройствах ввода информации (пультах управления) для преобразования десятичных чисел в двоичную систему счисления. Предположим, на пульте десять клавиш с гравировкой от 0 до 9. При нажатии любой из них на вход шифратора подается единичный сигнал (Х0, ..., Х9). На выходе шифратора должен появиться двоичный код (Y0, ..., Y3) этого десятичного числа. Как видно из таблицы истинности (табл. 9.1), в этом случае нужен преобразователь с десятью входами и четырьмя выходами.

Таблица

9.1

На выходе Y0 единица должна появиться при нажатии любой нечетной клавиши X1, ХЗ, Х5, Х7, Х9, т. е. Y0=Х1ХЗХ5Х7Х9. Состояние остальных выходов определяется логическими функциями: Y1=Х2ХЗХ6Х7, У2=Х4Х5Х6 Х7, УЗ=Х8УХ9. Следовательно, для реализации шифратора понадобится четыре элемента ИЛИ: пятивходовый, два четырехвходовых и двухвходовый (рис. 9.1,а). Условное обозначение такого шифратора представлено на рис. 9.1,б.

В серии К155 есть один шифратор типа К155ИВ1,

производящий преобразование

единичного кода на одном из восьми

входов в трехзначный двоичный код

(рис.

9.1,в).

Эта микросхема имеет вход стробирования

V.

Стробированием

называется выделение сигнала в

определенный момент времени. В данном

случае это появление выходного сигнала

в моменты, когда на входе стробирования

есть разрешающий уровень V=0.

На выходе G

этой ИМС появляется сигнал (с нулевым

уровнем) при подаче единичного сигнала

на любой из входов

0, ..., 7.

серии К155 есть один шифратор типа К155ИВ1,

производящий преобразование

единичного кода на одном из восьми

входов в трехзначный двоичный код

(рис.

9.1,в).

Эта микросхема имеет вход стробирования

V.

Стробированием

называется выделение сигнала в

определенный момент времени. В данном

случае это появление выходного сигнала

в моменты, когда на входе стробирования

есть разрешающий уровень V=0.

На выходе G

этой ИМС появляется сигнал (с нулевым

уровнем) при подаче единичного сигнала

на любой из входов

0, ..., 7.

В условно-графическом обозначении шифратора применяется символ СD (от англ. соdег—шифратор).

9.2. Дешифратор

Д

Рис. 9.1. Схема и

условные обозначения шифраторов

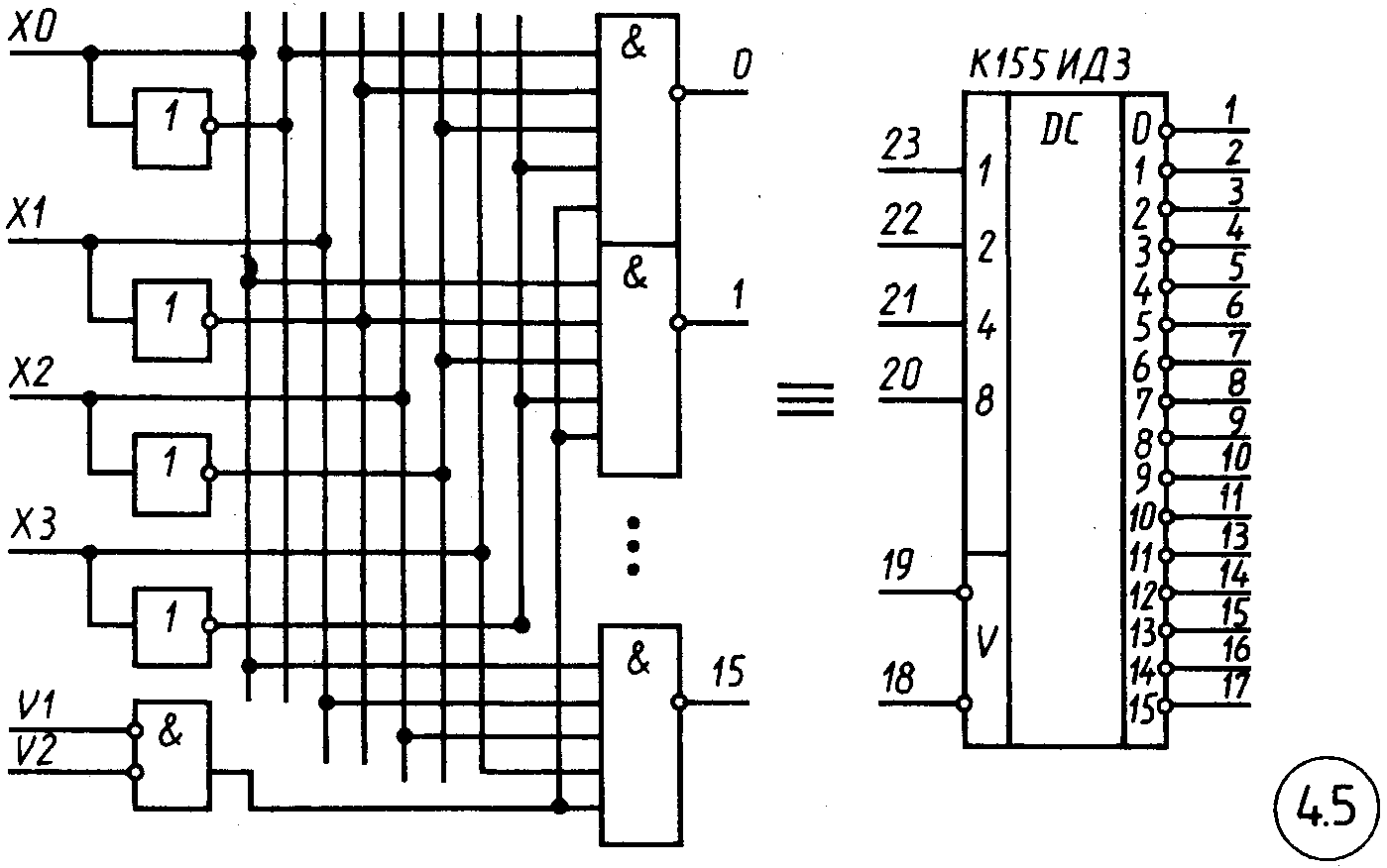

Д Рис. 9.2. Схема и условное

обозначение дешифратора

ешифратор

двоичногоn-разрядного

кода имеет 2n

выходов, так как каждому из

2n

значений входного кода должен

соответствовать единичный сигнал

на одном из выходов дешифратора.

Таблицу истинности для дешифратора

четырехразрядного двоичного кода

десятичных цифр можно получить из

таблицы 9.1,

если считать двоичный код ХЗ,

..., Х0

входным словом, а десятичный

— выходным. Логические

функции, описывающие работу такого

дешифратора, весьма просты:

Y0=ХЗХ2Х1Х0,

Y1=ХЗХ2Х1Х0,

Y2=Х3Х2Х1Х0,

..., Y15=ХЗХ2Х1Х0.

Условно-графическое обозначение такого

дешифратора двоичного кода в код

«1 из

16» типа К155ИДЗ, а также

часть его принципиальной схемы изображены

на рисунке 9.2.

Как видно из схемы, четыре входа каждого

пятивходового элемента И

-НЕ используются для

реализации логической функции

дешифрирования, а пятый вход нужен для

стробирования выходных сигналов.

ешифратор

двоичногоn-разрядного

кода имеет 2n

выходов, так как каждому из

2n

значений входного кода должен

соответствовать единичный сигнал

на одном из выходов дешифратора.

Таблицу истинности для дешифратора

четырехразрядного двоичного кода

десятичных цифр можно получить из

таблицы 9.1,

если считать двоичный код ХЗ,

..., Х0

входным словом, а десятичный

— выходным. Логические

функции, описывающие работу такого

дешифратора, весьма просты:

Y0=ХЗХ2Х1Х0,

Y1=ХЗХ2Х1Х0,

Y2=Х3Х2Х1Х0,

..., Y15=ХЗХ2Х1Х0.

Условно-графическое обозначение такого

дешифратора двоичного кода в код

«1 из

16» типа К155ИДЗ, а также

часть его принципиальной схемы изображены

на рисунке 9.2.

Как видно из схемы, четыре входа каждого

пятивходового элемента И

-НЕ используются для

реализации логической функции

дешифрирования, а пятый вход нужен для

стробирования выходных сигналов.

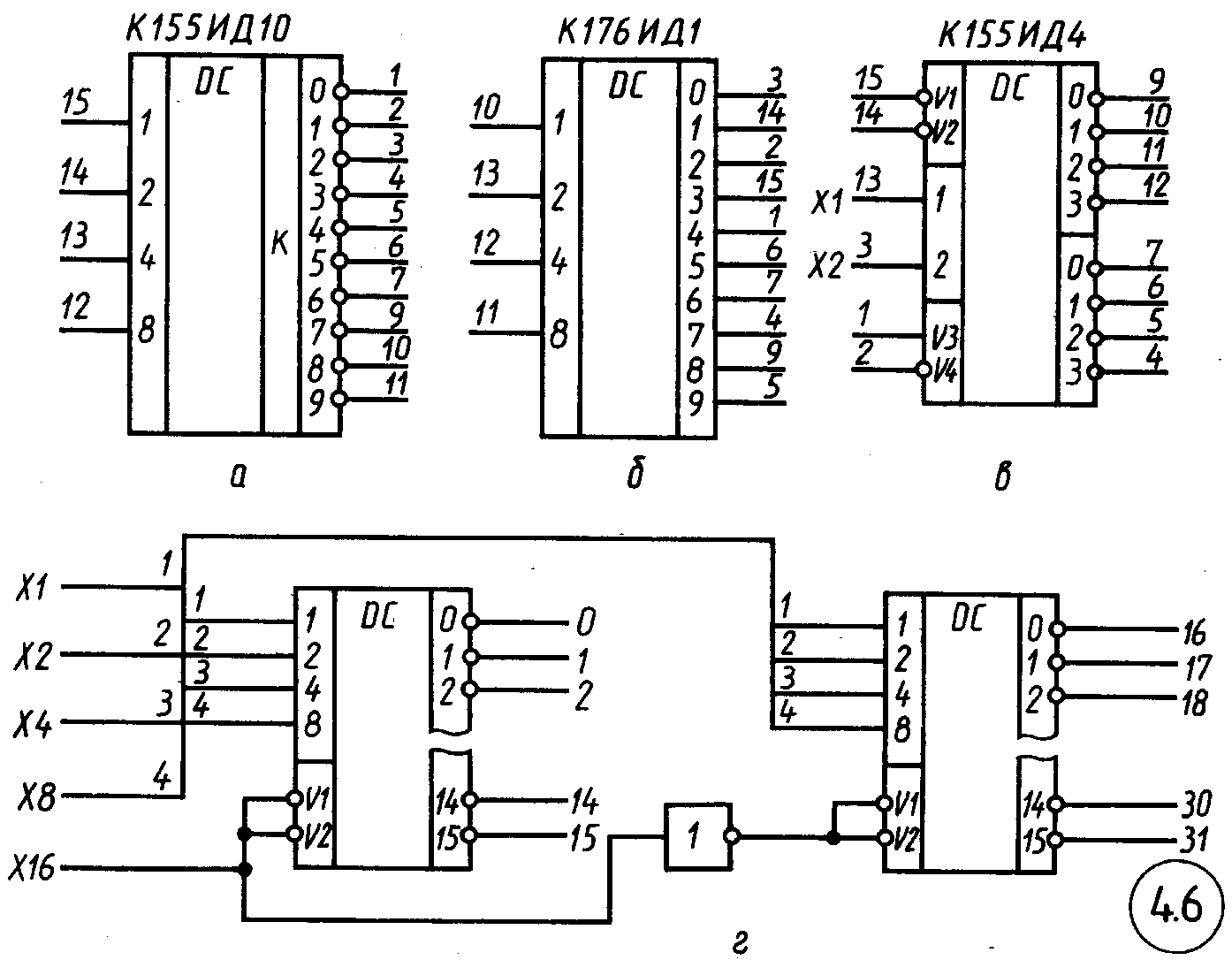

Р азнообразные

дешифраторы есть во всех развитых

сериях микросхем. Например, дешифраторы

К155ИД10 и К176ИД1 преобразуют двоичный

код в код

«1 из

10». Цоколевка

этих микросхем приведена на рисунке

9.3,а,б,в.

азнообразные

дешифраторы есть во всех развитых

сериях микросхем. Например, дешифраторы

К155ИД10 и К176ИД1 преобразуют двоичный

код в код

«1 из

10». Цоколевка

этих микросхем приведена на рисунке

9.3,а,б,в.

Наличие входов стробирования расширяет функциональные возможности дешифраторов. Так, благодаря им на двух ИМС К155ИДЗ можно собрать дешифратор на 32 выхода (рис. 9.3, г), а на четырех — на 64 выхода.

Рис. 9.3. Условные обозначения дешифраторов

К155 серии

9.3. Преобразователь двоично-десятичного кода в код семисегментного индикатора.

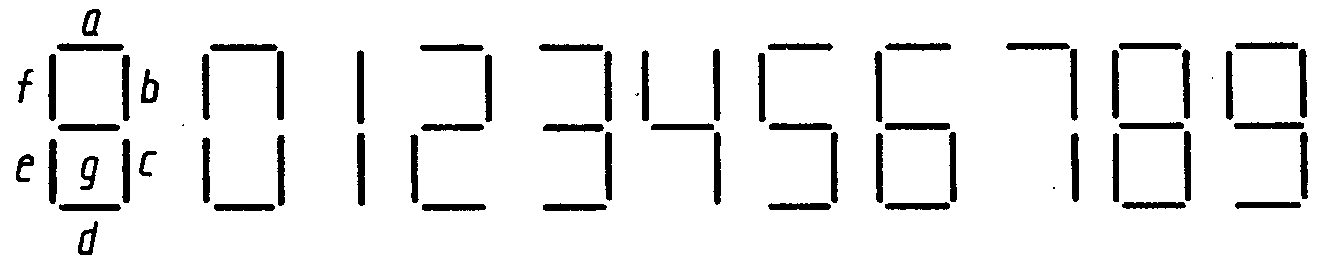

Индикация чисел на табло и пультах производится, как правило, в десятичном виде. Известно, что для этого можно использовать семисегментные светодиодные или жидкокристаллические индикаторы. Подавая управляющее напряжение на отдельные элементы индикатора и вызывая его свечение (светодиодные индикаторы) или изменяя его окраску (жидкокристаллические индикаторы), можно получить изображение десятичных цифр 0, 1, ..., 9.

Для удобства перевода двоичной информации в десятичный вид часто используют двоично-десятичный код (или код 8421), т. е. представление десятичных чисел в виде четырехразрядных двоичных чисел. Например: 75(10)=0111 0101; 910(10)=1001 0001 0000.

З

Рис. 9.4. Преобразователи кодов на К155

серии

акон

функционирования преобразователя

двоично-десятичного кода в код

семисегментного индикатора показан

в таблице 9.2.

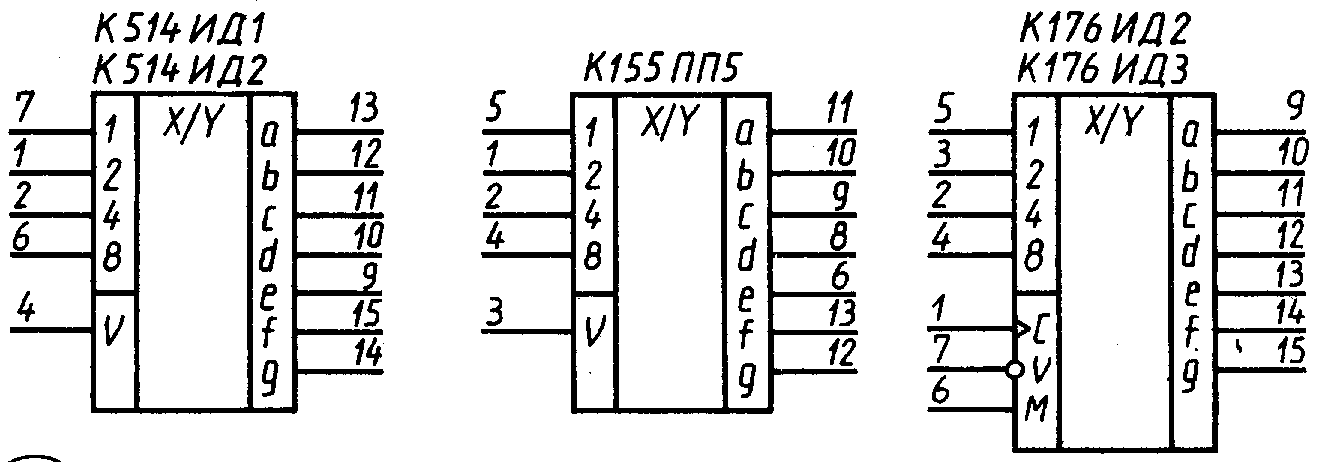

Условно-графические

обозначения некоторых микросхем -

преобразователей кода

8421 в. семисегментный

—показаны

на рисунке 9.4.

акон

функционирования преобразователя

двоично-десятичного кода в код

семисегментного индикатора показан

в таблице 9.2.

Условно-графические

обозначения некоторых микросхем -

преобразователей кода

8421 в. семисегментный

—показаны

на рисунке 9.4.

Таблица 9.2

|

Цифра |

Двоично-десятичный код |

Семисегментный код | ||||||||||

|

8 |

4 |

2 |

1 |

a |

b |

c |

d |

e |

f |

g | ||

|

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 | |

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 | |

|

2 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 | |

|

3 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 | |

|

4 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 | |

|

5 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 | |

|

6 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 | |

|

7 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 | |

|

8 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 | |

|

9 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 | |

На микросхемы серии К.514 поступают входные сигналы уровней ТТЛ. Сигнал V служит для гашения индикации (низкий уровень). При нормальной работе V=1. Преобразователь кода К514ИД1 работает со светодиодными индикаторами, имеющими раздельные аноды, а микросхема К514ИД2— раздельные катоды. К155ПП5 предназначен для индикаторов с раздельными катодами и внешними токоограничительными резисторами.

К176ИД2 и К176ИДЗ являются преобразователями кода с входным регистром памяти. Запись информации в память происходит по фронту тактового сигнала, подаваемого на вход С, при этом V=0. Если V=1, дешифратор блокируется. Управляющий вход М позволяет изменять выходной код дешифратора с прямого (M=0, на рабочие сегменты индикатора подается напряжение высокого уровня) на обратный (М=1, на рабочие сегменты—напряжение низкого уровня). К176ИД2 и К176ИДЗ предназначены для работы с жидкокристаллическими и люминесцентными индикаторами. Однако они могут работать и с экономичными светодиодными индикаторами, ток потребления которых не превышает 2—3 мА.

9.4. Мультиплексор

Мультиплексор — это узел, осуществляющий преобразование параллельных цифровых кодов в последовательные. В устройствах вычислительной техники его применяют для последовательного или адресного опроса заданного числа источников информационных сигналов и передачи этих сигналов на один выход.

У Рис. 9.5. Схема

и условное обозначение мультиплексора

на 4 вх.

словное

обозначение мультиплексора с четырьмя

информационными входами и его

принципиальная схема показаны на

рисунке 9.5.

Мультиплексор имеет два вида входов:

информационные

(D)

и кодовые, или адресные

(A).

Выбор информационной линии производится

кодом, поступающим на адресные входы.

Поэтому на выход Q

такого устройства передается

логический уровень того информационного

входа D,

номер которого

i

соответствует двоичному коду на

адресных входах А1,

А2. Из

принципиальной схемы следует, что

Y=D0•A2•A1VD1•A2•A1VD2•A2•A1VD3•A2•A1.

словное

обозначение мультиплексора с четырьмя

информационными входами и его

принципиальная схема показаны на

рисунке 9.5.

Мультиплексор имеет два вида входов:

информационные

(D)

и кодовые, или адресные

(A).

Выбор информационной линии производится

кодом, поступающим на адресные входы.

Поэтому на выход Q

такого устройства передается

логический уровень того информационного

входа D,

номер которого

i

соответствует двоичному коду на

адресных входах А1,

А2. Из

принципиальной схемы следует, что

Y=D0•A2•A1VD1•A2•A1VD2•A2•A1VD3•A2•A1.

Число информационных входов может быть увеличено, но при этом придется увеличить и разрядность адреса.

В интегральном исполнении выпускаются

мультиплексоры на два входа (четыре

элемента в одном корпусе), на четыре

входа (два в корпусе), на восемь и

шестнадцать входов. Условно-графические

обозначения некоторых из них показаны

на рисунке

9.6. Все они

имеют стробирующий вход

V

(низкий уровень). Вход V

позволяет создавать устройства с большим

числом информационных входов. Так,

на двух ИМС типа К155КП7 можно собрать

мультиплексор на

16 входов.

Студенты могут нарисовать эту схему

самостоятельно, используя пример

подобного решения, приведенный на

рисунке

9.3,г.

интегральном исполнении выпускаются

мультиплексоры на два входа (четыре

элемента в одном корпусе), на четыре

входа (два в корпусе), на восемь и

шестнадцать входов. Условно-графические

обозначения некоторых из них показаны

на рисунке

9.6. Все они

имеют стробирующий вход

V

(низкий уровень). Вход V

позволяет создавать устройства с большим

числом информационных входов. Так,

на двух ИМС типа К155КП7 можно собрать

мультиплексор на

16 входов.

Студенты могут нарисовать эту схему

самостоятельно, используя пример

подобного решения, приведенный на

рисунке

9.3,г.