opevs

.pdf

21

21

Уровни LVCMOS (низковольтовые уровни КМОП-схем; low-voltage CMOS) относятся к случаю использования только КМОП-схем, когда выходы схем слабо нагружены по постоянному току (меньше 100 мкА),

так что напряжения  и

и  отличаются от потенциала земли и от напряжения питания не более, чем на 0,2 В

отличаются от потенциала земли и от напряжения питания не более, чем на 0,2 В

Уровни LVTTL (низковольтовые уровни схем, совместимых с ТТЛ; low-voltage TTL) используются в схемах, где выходы существенно нагружены по постоянному току, и поэтому напряжение

может достигать 0,4 В, а напряжение

может достигать 0,4 В, а напряжение  может опускаться до

может опускаться до

2,4 В

22

22

9. Элементы индикации

Светодиоды изготовляются на основе полупроводниковых материалов (арсенида галлия, фосфида галлия, арсенид-фосфида галлия и др.), пропускание тока через которые вызывает их свечение

Яркость свечения светодиода непосредственно зависит от величины тока. Обычно достаточны токи от единиц до приблизительно двадцати миллиампер при падении напряжения на диоде около 1…2 В

Для задания тока светодиода последовательно с ним включается резистор

Из нескольких светодиодов составляются индикаторы и матрицы, отображающие буквы и цифры

Широко применяются семисегментные индикаторы (ССИ), в которых семь сегментов-диодов расположены так, что при зажигании определенной их комбинации высвечивается тот или иной символ

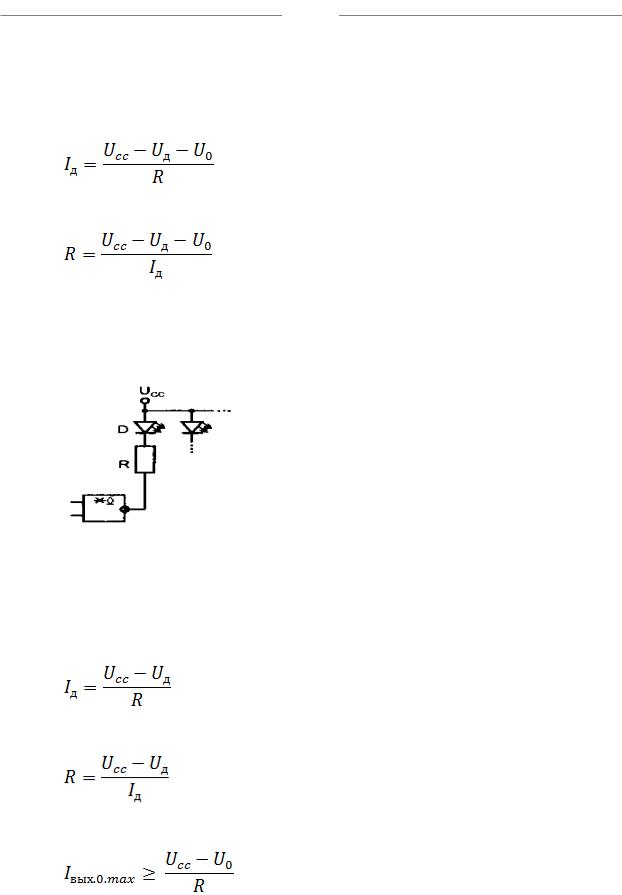

Семисегментные индикаторы бывают

с общим анодом

общим катодом

Для зажигания сегмента в схеме с общим анодом, подключенным к источнику питания Ucc , нужно снизить напряжение на его катоде (зажигание сигналом логического нуля)

Для зажигания сегмента в схеме с общим катодом, подключенным к общей точке схемы, необходимо повысить напряжение на его аноде(зажигание сигналом логической единиц)

Для управления сегментами удобны элементы с выходом типа ОК, поскольку при их использовании имеется внешняя цепочка с резистором, сопротивлением которого можно задать с учетом характеристик применяемых светодиодов

Управление одним из сегментов ССИ с общим анодом

23

23

Светодиод зажигается, когда на выходе управляющего элемента напряжение равно U0

Через светодиод будет протекать ток

Следовательно, для его задания требуется резисто сопротивлением

Значение тока через светодиод  берется из справочных данных. Для такого включения светодиода необходим управляющий элемент с достаточно большим выходным током в нулевом состоянии

берется из справочных данных. Для такого включения светодиода необходим управляющий элемент с достаточно большим выходным током в нулевом состоянии

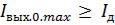

Управление одним из сегментов ССИ с общим катодом

Светодиод зажигается, когда выходной транзистор управляющего элемента запирается

Через диод течет ток

Откуда следует

Выход управляющего элемента должен удовлетворять условию

24

24

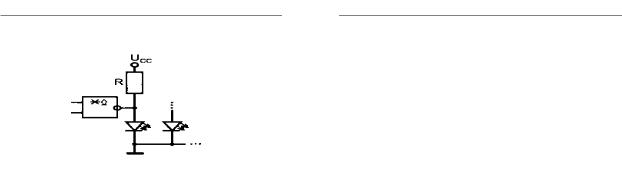

Для изображения символов на основе светодиодов изготовляются как семисегментные индикаторы, так и более сложные, в которых отображение символов осуществляется возбуждением определенных сегментов из поля матрицы

Число строк и столбцов матрицы может быть различным

Принципы формирования изображения при управлении сегментами матрицы те же, что и при управлении ССИ: входные коды специальным дешифратором преобразуются в сигналы возбуждения отдельных сегментов.При реализации индикаторов многозначных символов, содержащих несколько ССИ, удобно использовать мультиплексное управление.Одни и те же управляющие схемы поочередно обслуживают различные ССИ, выбирая их в определенной последовательности. При этом каждый индикатор возбуждается импульсно.Визуально видимость постоянного свечения всех символов создается из-за инерционности человеческого зрения. Если частота возбуждения индикаторов составляет 70…100 Гц, то мерцания изображений неощутимы

25

25

10.Риски в комбинационных схемах

|

Во время переходных процессов на выходах КЦ (КЦ – комбинационная цепь) |

|

появляются временные сигналы, не предусмотренные описанием работы |

|

комбинационного узла, которые называются рисками. Со временем они исчезают, и |

|

выход КЦ приобретает значение, предусмотренное логической формулой, |

|

описывающей работу цепи. Однако риски могут быть восприняты элементами памяти |

|

последовательностных узлов, необратимое изменение состояния которых может |

|

радикально изменить работу ЦУ, несмотря на исчезновение сигналов рисков на |

|

выходе КЦ |

|

Различают риски |

|

статические |

|

динамические |

|

Статические риски – это кратковременные изменения сигнала, который должен был |

|

бы оставаться неизменным. Если сигнал должен был оставаться единичным, то |

|

говорят о 1-риске, если нулевым – то о 0-риске. |

|

Динамический риск – это ситуация, когда вместо однократного перехода согласно |

|

логики работы КЦ, происходят многократные переходы. |

|

При динамических рисках первый и последний переходы всегда совпадают с |

|

алгоритмическими, предусмотренными логикой работы схемы. Статический риск |

|

такого свойства не имеет и считается более неблагоприятным. |

|

Для исключения возможных сбоев в работе ЦУ из-за явлений риска имеются два пути: |

синтез схем, свободных от рисков

запрещение восприятия сигналов КЦ элементами памяти на время переходных процессов

Первый путь требует сложного анализа процессов в схеме и введения избыточных элементов для исключения рисков. Этот путь редко используется на практике.

Второй путь, основной для современной схемотехники. Прием информации с выходов КЦ разрешается только специальным сигналом синхронизации, подаваемым на элементы памяти после окончания переходных процессов в КЦ. Таким образом, исключается воздействие ложных сигналов на элементы памяти. Соответствующие структуры называются синхронными

Для определения временного интервала, на котором проходят переходные процессы, следует оценить задержки на путях распространения сигналов от входов к выходам комбинационного узла

Нужно взять пути с минимальной и максимальной задержками

26

26

Самый короткий путь до выхода обозначит начало интервала переходных процессов, самый длинный – когда переходные процессы завершатся

В общем случае для расчета переходных процессов в ЦУ нужны сведения о минимальных и максимальных значениях задержек элементов. К сожалению,

изготовитель часто указывает только максимальные значения задержек, нередко приводятся максимальные и типовые значения и крайне редко имеются сведения о минимальных. Наиболее полно описывались бы задержки статистическими характеристиками, но они, как правило, неизвестны.

Если даны только максимальные задержки, то теряется возможность сравнивать времена прохождения сигналов в разных цепях, а это затрудняет оценку работоспособности схем и может привести к принятию не лучших схемотехнических решений.

27

27

11.Дешифраторы, преобразователи кодов.

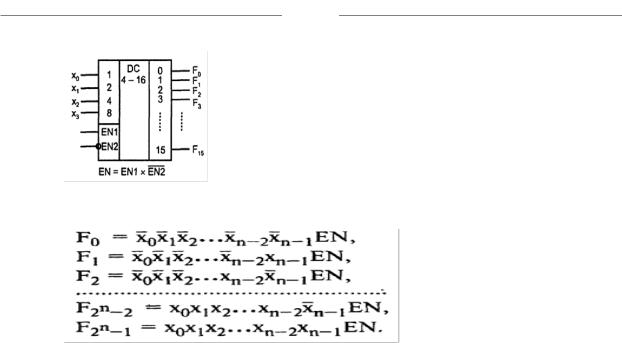

Дешифратор (ДШ) – это комбинационный узел, предназначенный для преобразования параллельного двоичного кода в унитарный (позиционный) код, т. е. код «1 из N». ДШ относятся к преобразователям кодов

При подаче на вход параллельного двоичного кода активный уровень сигнала появится на том выходе, номер которого соответствует десятичному эквиваленту двоичного кода. При этом в любой момент времени выходной сигнал будет иметь активный уровень только на одном выходе ДШ

В ДШ каждой выходной функции соответствует только один минтерм (конституента единицы), а кол-во функций определяется количеством разрядов двоичного числа. Если дешифратор реализует все минтермы входных переменных, то он называется полным дешифратором- дешифратор n x 2n. На вход такого ДШ поступает n-разрядное двоичное кодовое слово, а на выходе возникает слово кода «1 из 2n»

Полный ДШ применяется в том случае, когда необходимо актавизировать точно один из 2n выходов, определяемый n-разрядным двоичным числом на входе.

Если часть входных наборов не используется, то ДШ называют неполным, и у него число выходов меньше 2n

ДШ часто имеют разрешающий (управляющий, стробирующий) вход ЕN (Enable). При ЕN = 1 ДШ работает как обычно, при ЕN = 0 на всех выходах устанавливаются неактивные уровни независимо от поступившего входного кода. Вход ЕN часто выполняют инверсным

Дешифратор, имеющий разрешающий вход, иногда называют дешифратор-

демультиплексор

Если входов разрешения несколько, то сигнал разрешения работы образуется как конъюнкция сигналов отдельных входов

ДШ может иметь инверсные выходы. В этом случае только один выход имеет нулевое значение, а все остальные — единичное. При запрещении работы ДШ на всех его выходах будет присутствовать логическая единица

Условное обозначение двоичного дешифратора

В условном обозначении ДШ проставляются буквы DC (от английского Decoder). Входы ДШ принято обозначать их двоичными весами

28

28

Функционирование дешифратора описывается системой конъюнкций:

Для многих схемотехнических реализаций операция И-НЕ оказывается более удобной, чем операция И. Поэтому в стандартных сериях элементов дешифраторы с инверсными выходами встречаются значительно чаще, чем дешифраторы с прямыми выходами.

Время установления выходного сигнала дешифратора tDC = 2tз.инв + max(tз10, tз01),

где tз.инв — задержка сигнала в инверторе; tз10, tз01 — задержки переключений логического элемента.

Линейный (одноступенчатый) дешифратор имеет наибольшее быстродействие, но его реализация при повышенной разрядности входного кода требует применения логических элементов с большим числом входов, что приводит к увеличению нагрузки на источники входных сигналов и снижению быстродействие логических элементов.

Корпуса ИС с большим числом выводов изготовлять сложно, и они дороги. С этой точки зрения дешифраторы относятся к крайне неудачным схемам, так как у них при простой внутренней структуре и малом числе схемных элементов много внешних выводов. Для размещения в обычном недорогом корпусе годится только дешифратор с 4 информационными входами. Более «размерных» дешифраторов в сериях ИС нет.

Малоразрядность стандартных ДШ ставит вопрос о наращивании их разрядности. Из малоразрядных ДШ можно построить схему, эквивалентную ДШ большей разрядности

Для построения ДШ с большим числом входов используется многоступенчатая схема. Для этого входное слово делится на поля. Разрядность поля младших разрядов соответствует числу входов имеющихся

29

29

дешифраторов. Оставшееся поле старших разрядов служит для получения сигналов разрешения работы одного из дешифраторов, декодирующих поле младших разрядов.

Дешифраторы совместно со схемами ИЛИ можно использовать для реализации произвольных логических функций.

На выходах ДШ вырабатываются все конъюнктивные термы (конституенты единицы), которые только можно составить из данного числа аргументов.

Логическая функция в СНДФ есть дизъюнкция некоторого числа таких термов.

Собирая нужные термы по схеме ИЛИ, можно получить любую функцию данного числа аргументов.

Реализация логической функции сводится к поиску выходов ДШ, соответствующих входящим в совершенную дизъюнктивную нормальную форму исходной функции элементарным конъюнкциям и объединению этих выходов с помощью элемента ИЛИ.

Такое решение может быть целесообразным при необходимости получения нескольких функций одних и тех же аргументов. В этом случае для получения дополнительной функции добавляется только один элемент ИЛИ.

Преобразователи кодов

Преобразователи кодов используются для шифрации и дешифрации цифровой информации – преобразования кода одного типа в другой (например, двоичного кода в код Грея) и имеют n входов и k выходов. Соотношения между числами n и k могут быть любыми: n = k, n > k и n < k. Преобразователи кодов можно разделить на два типа:

с невесовым преобразованием кодов

с весовым преобразованием кодов.

Примером преобразователей первого типа являются преобразователи двоично-десятичного кода в код семисегментного индикатора десятичных цифр. Преобразователи второго типа используются, как правило, для преобразования числовой информации.

30

30

12.Шифраторы

Шифратор – это комбинационный узел, который выполняет функцию, обратную дешифратору. Двоичный шифратор преобразуют код «1 из N» в двоичный. Классический шифратор имеет m входов и n выходов, и при подаче сигнала на один из входов на выходе узла появляется двоичный код номера возбужденного входа. Число входов и выходов

полного шифратора связано соотношением  Шифратор можно использовать, например, для отображения в виде двоичного кода номера нажатой кнопки или положения многопозиционного переключателя. Приоритетные шифраторы (ПШ) выполняют более сложную операцию.

Шифратор можно использовать, например, для отображения в виде двоичного кода номера нажатой кнопки или положения многопозиционного переключателя. Приоритетные шифраторы (ПШ) выполняют более сложную операцию.

При работе ЭВМ и в других ЦУ часто решается задача определения приоритетного претендента на пользование каким-либо ресурсом. Несколько конкурентов выставляют свои запросы на обслуживание, которые не могут быть удовлетворены одновременно. Нужно выбрать того, кому предоставляется право первоочередного обслуживания. Простейший вариант решения указанной задачи – присвоение каждому источнику запросов фиксированного приоритета. Например, группа из

восьми запросов  (R от английского Request) формируется так, что высший приоритет имеет источник номер 7, а далее приоритет уменьшается от номера к номеру. Самый младший приоритет у нулевого источника – он будет обслуживаться только при отсутствии всех других запросов. Если имеются одновременно несколько запросов, обслуживается запрос с наибольшим номером.

(R от английского Request) формируется так, что высший приоритет имеет источник номер 7, а далее приоритет уменьшается от номера к номеру. Самый младший приоритет у нулевого источника – он будет обслуживаться только при отсутствии всех других запросов. Если имеются одновременно несколько запросов, обслуживается запрос с наибольшим номером.

Приоритетный шифратор вырабатывает на выходе двоичный номер старшего запроса. При наличии всего одного возбужденного входа приоритетный шифратор работает так же, как и двоичный. Поэтому в

сериях элементов двоичный шифратор как самостоятельный элемент может отсутствовать. Режим его работы – частный случай работы приоритетного шифратора. В промышленных сериях элементов обычно имеются приоритетные шифраторы для восьмиразрядных слов. Функционирование такого шифратора описывается таблицей.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

X |

|

X |

|

X |

|

X |

|

X |

|

X |

|

X |

|

1 |

|

1 |

|

1 |

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

|

1 |

|

X |

|

X |

|

X |

|

X |

|

X |

|

X |

|

1 |

|

1 |

|

0 |

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|