arx230910

.pdf

выполнить преобразования одних форм представления информации в другие. Эту задачу решают специальные устройства – адаптеры.

Адаптер – это устройство, которое обеспечивает связь между центральной частью ПВЭМ и конкретным внешним устройством.

Конструктивно они оформляются в виде печатных плат, которые с одной стороны имеют стандартный разъём для сопряжения с системной шиной, а с другой специфический разъём для связи соответствующим устройством. Следует отметить, что по мере совершенствования элементной базы ПЭВМ складываются предпосылки уменьшения потребности в адаптерах, так как часть их обязанностей берут на себя электронные схемы управления самих устройств и некоторые микросхемы на системной плате.

Лекция 2. Центральный процессор

2.1.Оперативная память и процессор

Рассмотрим вопросы, как выполняются прикладные программы пользователя и в каком месте происходит их выполнение. Для этого необходимо подробно ознакомится с взаимодействием оперативной памяти и центрально процессора.

Рис. 2.1. Взаимодействие оперативной памяти и процессора.

Программы загружаются в оперативную память с ж/д, загрузку осуществляет операционная система. Загрузка операционной системы осуществляется в ответ на выбор пользователя. Далее операционная система производит настройку программы для выполнения. Операционная система сообщает начальный адрес ячейки, где хранится программа в оперативной памяти, после этого ОС инициирует (вызывает) процесс выполнения программы. Центральный процессор последовательно выполняет данные команды программы, начиная с указанной. Выполнив текущую команду, процессор переходит к следующей, и так дальше до конца программы. Завершив программу, процессор не будет знать, что ему дальше делать, поэтому любая программа должна завершаться командами, передающими управление операционной системе компьютера. Таким образом, выполнив все команд программы, процессор передает управление операционной системе.

Оперативная память компьютера представляет собой электронное устройство, состоящее из большого числа двоичных запоминающих элементов, а также схем управления ими. Минимальный объем информации,

31

к которому имеется доступ в памяти, составляет один байт (8 двоичных разрядов, или битов). Все байты оперативной памяти нумеруются, начиная с нуля. Нужные байты отыскиваются в памяти по их номерам, выполняющим функции адресов.

Рис. 2.2. Байт, слово и двойное слово.

Некоторые данные (например, коды символов) требуют для своего хранения 1 байт; для других данных этого места на хватает, и под них в памяти выделяется 2, 4, 8 или еще большее число байтов. Обычно пары байтов называют словами, а четверки - двойными словами (рис. 2.2), хотя иногда термином "слово" обозначают любую порцию машинной информации.

При обсуждении содержимого многобайтового данного приходится ссылаться на составляющие его байты; эти байты условно нумеруются от нуля и располагаются (при их изображении на бумаге) в порядке возрастания номера справа налево, так что слева оказываются байты с большими номерами, а справа - байты с меньшими номерами. Крайний слева байт принято называть старшим, а крайний справа - младшим. Такой порядок расположения байтов связан с привычной для нас формой записи чисел: в многоразрядном числе слева указываются старшие разряды, а справа - младшие. Следующее число, если его написать за предыдущим, опять начнется со старшего разряда и закончится младшим. Однако в памяти компьютера данные располагаются в более естественном порядке непрерывного возрастания номеров байтов и, таким образом, каждое слово или двойное слово в памяти начинается с его младшего байта и заканчивается старшим (рис. 2.3).

Рис. 2.3. Нумерация байтов в многобайтовых данных.

32

Строго говоря, в памяти компьютера можно хранить только целые двоичные числа, так как память состоит из двоичных запоминающих элементов. Для записи иных данных, например, символов или дробных чисел, для них предусматриваются правила кодирования, т.е. представления в виде последовательности битов той или длины. Так, действительное число одинарной точности занимает в памяти двойное слово (32 бит), в котором 23 бит, отводятся под мантиссу, 8 бит под порядок и еще один бит под знак числа. Программы, работающие с такого рода данными, должны, естественно, знать правила их записи и руководствоваться ими при обработке и представлении этих данных.

Двоичная система счисления, в которой работают все цифровые электронные устройства, неудобна для человека. Для удобства представления двоичного содержимого ячеек памяти или регистров процессора используют иногда восьмеричную, а чаще - шестнадцатеричную системы счисления. Для процессоров Intel используется шестнадцатеричная система.

Каждый разряд шестнадцатеричного числа может принимать 16 значений, из которых первые 10 обозначаются обычными десятичными цифрами, а последние 6 - буквами латинского алфавита от А до F, где А обозначает 10, В - И, С - 12, D - 13, Е - 14, a F - 15. В языке ассемблера шестнадцатеричные числа, чтобы отличать их от десятичных, завершаются буквой h (или Н). Таким образом, 100 - это десятичное число, a l00h - шестнадцатеричное (равное 256). Поскольку одна шестнадцатеричная цифра требует для записи ее в память компьютера четырех двоичных разрядов, то содержимое байта описывается двумя шестнадцатеричными цифрами (от 00h до FFh, или от 0 до 255) , а содержимое слова - четырьмя (от 0000h до FFFFh,

или от 0 до 65535).

Помимо ячеек оперативной памяти, для хранения данных используются еще запоминающие ячейки, расположенные в процессоре и называемые регистрами. Достоинство регистров заключается в их высоком быстродействии, гораздо большем, чем у оперативной памяти, а недостаток в том, что их очень мало - всего около десятка. Поэтому регистры используются лишь для кратковременного хранения данных. В режиме МП 86, который мы здесь обсуждаем, все регистры процессора имеют длину 16 разрядов, или 1 слово (в действительности в современных процессорах их длина составляет 32 разряда, но в МП 86 от каждого регистра используется лишь его половина). За каждым регистром закреплено определенное имя (например, АХ или DS), по которому к нему можно обращаться в программе. Состав и правила использования регистров процессора будут подробно описаны ниже, здесь же мы коснемся только назначения сегментных регистров, с помощью которых осуществляется обращение процессора к ячейкам оперативной памяти.

Казалось бы, для передачи процессору адреса какого-либо байта оперативной памяти, достаточно записать в один из регистров процессора его номер. В действительности поступить таким образом в 16-разрядном

33

процессоре нельзя, так как максимальное число (данное или адрес), которое можно записать в 16-разрядный регистр, составляет всего 216 - 1 = 65535, или 64К-1, и мы получим возможность обращения лишь к первым 64 Кбайт памяти. Для того, чтобы с помощью 16-разрядных чисел адресовать любой байт памяти, в МП 86 предусмотрена сегментная адресация памяти, реализуемая с помощью сегментных регистров процессора.

2.2. Cегментная адресация

Суть сегментной адресации заключается в следующем. Обращение к памяти осуществляется исключительно с помощью сегментов - логических образований, накладываемых на те или иные участки физической памяти. Исполнительный адрес любой ячейки памяти вычисляется процессором путем сложения начального адреса сегмента, в котором располагается эта ячейка, со смещением к ней (в байтах) от начала сегмента (рис. 2.4). Это смещение иногда называют относительным адресом.

Рис. 2.4. Образование физического адреса из сегментного адреса и смещения.

Начальный адрес сегмента без четырех младших битов, т.е. деленный на 16, помещается в один из сегментных регистров и называется сегментным адресом. Сам же начальный адрес хранится в специальном внутреннем регистре процессора, называемом теневым регистром. Для каждого сегментного регистра имеется свой теневой регистр; начальный адрес сегмента загружается в него процессором в тот момент, когда программа заносит в соответствующий сегментный регистр новое значение сегментного адреса.

Процедура умножения сегментного адреса на 16 (или, что то же самое, на 10h) является принципиальной особенностью реального режима, ограничивающей диапазон адресов, доступных в реальном режиме, величиной 1 Мбайт. Действительно, максимальное значение сегментного адреса составляет FFFFh, или 64К-1, из чего следует, что максимальное значение начального адреса сегмента в памяти равно FFFF0h, или 1 Мбайт - 16. Если, однако, учесть, что к начальному адресу сегмента можно добавить любое смещение в диапазоне от 0 до FFFFh, то адрес последнего адресуемого

34

байта окажется равен 10FFEFh, что соответствует величине 1 Мбайт + 64 Кбайт - 17.

Диапазон адресов, формируемых процессором, называют адресным пространством процессора; как мы видим, в реальном режиме он немного превышает 1 Мбайт. Заметим еще, что для описания адреса в пределах 1 Мбайт требуются 20 двоичных разрядов, или 5 шестнадцатеричных. Процессор 8086 имел как раз 20 адресных линий и не мог, следовательно, выйти за пределы 1 Мбайт; современным 32-разрядным процессорам, если они работают в реальном режиме, доступно несколько большее (почти на 64 Кбайт) адресное пространство. Если же процессор работает в защищенном режиме (с использованием 32-разрядных регистров), то его адресное пространство увеличивается до 232 байт = 4 Гбайт.

2.3. Регистры процессора

Помимо ячеек памяти для хранения данных (кратковременного) можно использовать регистры – ячейки, расположенные в центральном процессоре и доступные из машинных программ.

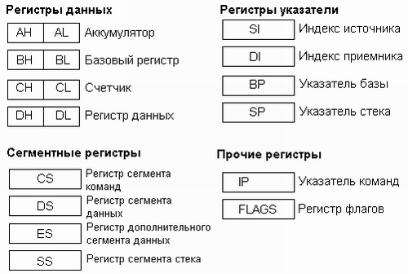

Все регистры имеют размер слова (16 разрядов), за каждым из них закреплено определенной имя (AX, SP и т.т.). Процессор содержит четырнадцать 16-разрядных программно-адресуемых регистров, которые принято объединять в следующие группы:

•регистры общего назначения (AX, BX, CX, DX, SI, DI, BP, SP);

•сегментные регистры (CS, DS, SS, ES);

•указатель команд (IP);

•регистр флагов (Flags).

Вгруппу регистров данных включаются четыре регистра АХ, ВХ, СХ и DX. Программист может использовать их по своему усмотрению для временного хранения любых объектов (данных или адресов) и выполнения над ними требуемых операций. При этом регистры допускают независимое обращение к старшим (АН, ВН, СН и DH) и младшим (AL, BL, CL и DL) половинам. Так, команда

mov BL, АН

пересылает старший байт регистра АХ в младший байт регистра ВХ, не затрагивая при этом вторых байтов этих регистров. Заметьте, что сначала указывается операнд-приемник, а после запятой - .операнд-источник, т.е. команда как бы выполняется справа налево.

35

Рис. 2.5. Регистры процессора.

Во многих случаях регистры данных вполне эквивалентны, однако предпочтительнее пользоваться регистром АХ, поскольку многие команды занимают в памяти меньше места и выполняются быстрее, если их операндом является регистр АХ (или его половина AL). С другой стороны, ряд команд использует определенные регистры неявным образом. Так, все команды циклов используют регистр СХ в качестве счетчика числа повторений; в командах умножения и деления регистры АХ и DX выступают в качестве неявных операндов; операции ввода-вывода можно осуществлять только через регистры АХ или AL и т.д.

Индексные регистры SI и DI так же, как и регистры данных, могут использоваться произвольным образом. Однако их основное назначение - хранить индексы, или смещения относительно некоторой базы (т.е. начала массива) при выборке операндов из памяти. Адрес базы при этом может находиться в базовых регистрах ВХ или ВР. Специально предусмотренные команды работы со строками используют регистры SI и DI в качестве неявных указателей в обрабатываемых строках.

Регистр ВР служит указателем базы при работе с данными в стековых структурах, но может использоваться и произвольным образом в большинстве арифметических и логических операций.

Последний из группы регистров-указателей, указатель стека SP, стоит особняком от других в том отношении, что используется исключительно как указатель вершины стека - специальной структуры, которая будет рассмотрена ниже.

Регистры SI, DI, BP и SP, в отличие от регистров данных, не допускают побайтовую адресацию.

Четыре сегментных регистра CS, DS, ES и SS являются важнейшим элементом архитектуры процессора, обеспечивая, как уже отмечалось выше, адресацию 20-разрядного адресного пространства с помощью 16-разрядных операндов. Подробнее о них будет рассказано в следующем разделе.

36

Указатель команд IP "следит" за ходом выполнения программы, указывая в каждый момент относительный адрес команды, следующей за исполняемой. Регистр IP программно недоступен (IP - это просто его сокращенное название, а не мнемоническое обозначение, используемое в языке программирования); наращивание адреса в нем выполняет микропроцессор, учитывая при этом длину текущей команды. Команды переходов, прерываний, вызова подпрограмм и возврата из них изменяют содержимое IP, осуществляя тем самым переходы в требуемые точки программы. В следующем разделе мы еще вернемся к роли регистра IP в выполнении программы.

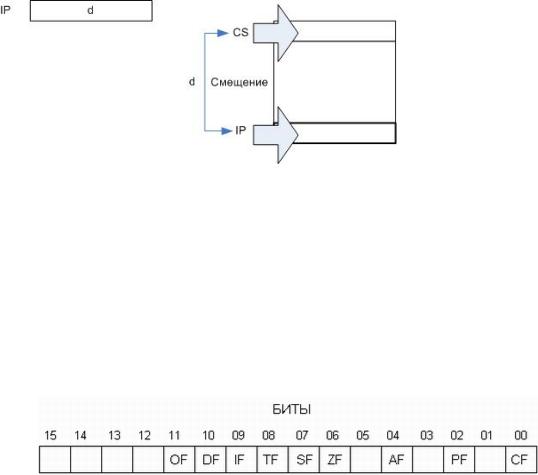

Рис. 2.6. Регистр IP смещение d от начала сегмента. Специальный регистр командного указателя IP указывает на следующую исполняемую машинную команду относительно определенного в CS сегмента.

Регистр флагов (его часто называют FLAGS), эквивалентный регистру состояния процессора других вычислительных систем, содержит информацию о текущем состоянии процессора (рис. 2.6). Он включает 6 флагов состояния и 3 бита управления состоянием процессора, которые, впрочем, тоже называются флагами.

Рис. 2.6. Регистр флагов Флаги состояния заново устанавливаются процессором после

выполнения каждой очередной команды, и по ним можно в какой-то степени судить о результате выполнения этой команды (например, не равен ли ее результат, нулю). Флаги управления позволяют изменять некоторые условия работы процессора, например, разрешать или запрещать аппаратные прерывания. Рассмотрим сначала флаги состояния.

Флаг переноса CF (Carry Flag) индицирует перенос или заем при выполнении арифметических операций. Переносом называется ситуация, когда в результате выполнения правильной, в общем, команды образуется число, содержащее более 16 двоичных разрядов и, следовательно, не помещающееся в регистр или ячейку памяти. Пусть, например, в регистре

37

АХ содержится число 60000, а в регистре ВХ - 40000. При выполнении команды сложения

add AX,BX

в регистре-приемнике результата, которым в данном случае будет служить регистр АХ, должно быть записано число 100000, которое, разумеется, там поместиться не может. В этом случае и устанавливается флаг CF, по состоянию которого можно установить, что произошел перенос и, следовательно, содержимое АХ (которое в данном случае будет равно 100000 - 65536 = 34464) не является правильным результатом.

Необходимо подчеркнуть, что ситуация переноса, как и вообще любая ошибка, возникшая по ходу выполнения программы, не приводит ни к каким последствиям, кроме установки соответствующего флага. Процессор, установив флаг, считает свою миссию выполненной и переходит к выполнению следующей команды. Если перенос в данном случае действительно является индикатором ошибки, программа должна после выполнения команды сложения проанализировать состояние флага CF, и при установленном флаге перейти на фрагмент обработки этой ошибки. Такой анализ выполняется с помощью команд условного перехода, в данном случае с помощью команды jc (jump if carry, переход по переносу).

Флаг паритета PF (Parity Flag) устанавливается в 1, если результат операции содержит четное число двоичных единиц, и сбрасывается в О, если число двоичных единиц нечетно. Этот флаг можно использовать, например, для поиска ошибок при передаче данных и при выполнении диагностических тестов.

Флаг вспомогательного переноса AF (Auxiliary Flag) используется в операциях над двоично-десятичными числами. Он индицирует перенос или заем из старшей тетрады (бита 4). Двоично-десятичный формат подразумевает запись в каждой половинке байта десятичной цифры в виде ее двоичного эквивалента, что позволяет хранить в байте двухразрядное десятичное число в диапазоне от 0 до 99 Двоично-десятичные числа используются, в частности, для обмена данными с измерительными приборами. Для их обработки в процессоре предусмотрен целый ряд специфических команд, при использовании которых приходится анализировать состояние флага вспомогательного переноса.

Флаг нуля ZF (Zero Flag) устанавливается в 1, если результат операции равен 0. Например, флаг ZF установится, если из 5 вычесть 5 или к 10 прибавить -10.

Флаг знака SF (Sign Rag) показывает знак результата операции, устанавливаясь в 1 при отрицательном результате. Как будет показано в следующей главе, процессор различает числа без знака, т.е. существенно положительные, и числа со знаком, которые могут быть как положительными, так и отрицательными. Признаком отрицательности числа служит установленный старший бит этого числа (бит 15 для слов или бит 7 для байтов). Флаг SF устанавливается, если в результате какой-либо

38

операции сформировано число с установленным старшим битом, например, S000h или FFFFh.

Флаг переполнения OF (Overflow Rag) фиксирует переполнение, т.е. выход результата за пределы допустимого диапазона значений для чисел со знаком. В знаковом представлении числа от 0000h до 7FFFh считаются положительными, а числа от S000h до FFFFh, т.е. числа с установленным старшим битом - отрицательными. Флаг OF устанавливается, если, например, при сложении двух положительных чисел получился результат, превышающий 7FFFh (потому что, начиная с S000h, идут уже отрицательные числа), или при вычитании из отрицательного числа получился результат, меньший S000h (потому что такие числа считаются положительными). Позже этот вопрос будет рассмотрен более детально.

Перейдем теперь к управляющим флагам, которых в регистре флагов реального режима всего три.

Управляющий флаг трассировки (ловушки) TF (Trace Rag) используется для осуществления пошагового выполнения программы. Если TF=1, то после выполнения каждой команды процессор реализует процедуру прерывания через вектор с номером 1, расположенный по физическому адресу 04. Этот флаг активно используется в программах отладчиков, которые должны допускать выполнение отлаживаемой программы по шагам или с точками останова.

Управляющий флаг разрешения прерываний IF (Interrupt Rag) разрешает (если равен 1) или запрещает (если равен 0) процессору реагировать на прерывания от внешних устройств. Тем самым создается возможность выполнения особо ответственных фрагментов программ без каких-либо помех.

Управляющий флаг направления DF (Direction Rag) используется командами обработки строк. Если DF=0, строка обрабатывается в прямом направлении, от меньших адресов к большим; если DF=1, обработка строки идет в обратном направлении. Примеры использования этого флага будут приведены при рассмотрении соответствующих команд процессора.

Для установки и сброса управляющих флагов предусмотрены особые команды, например sti (set interrupt, установить прерывания) или cli (clear interrupt, сбросить прерывания).

Флаги условий:

CF |

переноса |

признак устанавливается в 1, если имеет место |

|

(carry flag) |

переноса или заем из старшего бита результата |

OF |

переполнения |

равен 1, если возникает арифметическое |

|

(overflow flag) |

переполнение |

ZF |

нуля |

равен 1, если результат команды равен 0 |

|

(zero flag) |

|

SF |

знака |

равен 1, если старший бит результата равен 0, т.е. |

|

(sign flag) |

SF = 0 - число положительное |

|

|

SF = 0 - число отрицательное |

PF |

четности |

равен 1, если результат имеет четное число единиц |

39

|

(parity flag) |

|

|

AF |

дополнительного |

равен 1, если во время выполнения команд |

|

|

переноса |

десятичного сложения и вычитания осуществлено |

|

|

(auxiliary carry |

выполнение переноса или заема между полубайтами |

|

|

flag) |

|

|

Флаги состояний: |

|

|

|

DF |

направления |

устанавливает направление просмотра строк в |

|

|

(direct flag) |

строковых командах |

|

|

|

DF = 0 от начала к концу |

|

|

|

DF = 1 в обратном направлении |

|

IF |

прерывания |

IF = 0 процессор перестает реагировать на |

|

|

(interrupt flag) |

поступающие к нему прерывания |

|

|

|

IF = блокировка прерываний снимается |

|

TF |

трассировки |

TF = 1 после выполнения каждой команды процессор |

|

|

(trap flag) |

делает прерывание, чем можно воспользоваться при |

|

|

|

отладке программы |

|

|

2.4. Понятие о реальном режиме работы процессора |

||

|

Процессоры Intel для ПЭВМ до выхода intel 286 могли работать только |

||

в однозадачном режиме, который мы будем называть реальным режимом или режимом 80x86. начиная с Intel 286, была введена возможность многозадачного режима работы, основной проблемой которого была защита данных каждой задачи от всех остальных. Такой режим мы будем называть защищенным. Следует отметить что процессор Int. 286 с этой задачей не справился и являлся, по существу, более быстрой версией 80x86. Только на процессорах Int 386 и выше с введением новых регистров и повышением разрядности старых регистров удалось достигнуть уверенной работы в защищенном режиме.

Важно отметить, что реальный режим (80x86) работы сохраняется для всех высших моделей процессоров. В наших лекциях мы, в основном, будем рассматривать вопросы реального режима и лишь наметим основные идеи заложенные в осуществлении защищенного режима.

Режим работы процессора задается наличием основных регистров, разрядностью регистров, способом обращения к ОП. Компьютерные программы которые написаны для реальным режима работы процессора могут работать в защищенном, в так называемом режиме виртуального процессора (80x86). Программы написанные для защищенного режима, как правило в реальном режиме уже работать не будут.

|

|

|

Таблица 1. |

|

Схема адресного пространства процессора 80x86. |

||

|

Реальный режим. |

|

|

Адресная |

Область памяти |

Объем |

Класс памяти |

система |

|

памяти |

|

00000h |

Вектор с прерыванием |

1 Кбайт |

Обычная память 640 кб. |

00400h |

Данные BIOS |

256 байт |

Conventional memory |

00500h |

MS DOS |

~ 80 кбайт |

|

40