arx011010_ch1

.pdfДалее, адрес местоположения первой команды программы посылается по адресной шине к схемам управления памятью, в результате чего считывается содержимое области (ячейки) с указанным адресом. Этим содержимым должна быть команда. Память пересылает эту команду в специальный регистр процессора – регистр команд.

После извлечения команды из памяти, процессор автоматически дает приращение содержимому счетчика команд. Это приращение счетчик как раз в тот момент, когда процессор начинает выполнять команду, только что извлеченную из памяти. Следовательно, начиная с этого момента счетчик команд, указывает, какой будет следующая команда.

Программируя работу процессора, иногда возникает необходимость в использовании текущего содержимого счетчика команд.

Определение. Счетчик команд указывает на адрес следующей команды, которая должна быть выполнена после завершения текущей команды.

3.3.5. Регистр адреса памяти

При каждом обращении к памяти ЭВМ регистр адреса памяти указывает адрес области памяти (ячейки), которая подлежит использованию процессором. Регистр адреса памяти содержит двоичное число – адрес области памяти. Выход этого регистра называется адресной шиной и используется для выбора области памяти или в некоторых случаях для выбора порта ввода-вывода.

Втечение подцикла выборки команды из памяти, регистры адреса памяти и счетчика команд имеют одинаковое содержимое, т.е. регистр адреса памяти указывает местоположение команды, извлекаемой из памяти. После декодирования команды счетчик команд получает приращение. Что же касается регистра адреса то он приращение не получает.

Втечение подцикла выполнения команды содержимое регистра адреса памяти зависит от выполняемой команды. Если в соответствии с командой процессор должен произвести еще одно обращение к памяти, то регистр адреса памяти подлежит вторичному использованию в процессе обработки этой команды. Для некоторых команд (безадресных) адресация не требуется.

Вбольшинстве процессоров регистры адреса памяти и счетчика команд имеют одинаковое число разрядов. Как и счетчик команд, регистр адреса памяти должен располагать количеством разрядов, достаточным для адресации любой области ОП. В нашем 8-разрядном процессоре, количество разрядов регистра адреса памяти – 16. Такой регистр можно разделить на два отдельных регистра, каждый из которых имеет независимое подключение к шине данных процессора. Один из этих регистров называют

регистром старшего байта (СБ), другой – регистром младшего байта (МБ).

Поскольку регистр адреса памяти подключен к внутренней шине данных процессора, он может загружаться от различных источников. Большинство процессоров располагают командами, позволяющими загружать этот регистр содержимым счетчика команд, регистра общего назначения, или содержимым области ОП (ячейки).

Определение. Регистр адреса – содержит адрес ячейки, из которой будет считана команда или операнд. В ней может, содержатся адрес ячейка памяти, в которую требуется записать результат выполнения команды.

3.3.6.Регистр команд

Регистр команд предназначен исключительно для хранения текущей выполняемой команды, причем эта функция реализуется процессором автоматически с началом цикла выборка-выполнение, называемого также машинным циклом. Машинный цикл состоит из двух подциклов – выборки и выполнения. За исключением загрузки команды, период подцикла выборки программист не может по другому использовать регистр команд. Согласно схеме на рис. 3.4, этот регистр соединен с внутренней шиной данных, однако он только принимает данные – посылать данные на шину он не может.

41

Хотя функции регистра команд ограничены, роль его в работе процессора велика, поскольку выход этого регистра является частью дешифратора команд.

Проследим состояния регистра команд в последовательности реализации цикла выборки-исполнения (команды ЭВМ, машинного цикла). Сначала команда извлекается из памяти, затем счетчик команд настраивается на указание следующей команды, подлежащей выполнению. При извлечении команды из соответствующей области памяти копия команды помещается на внутреннюю шину данных и пересылается в регистр команд. После этого начинается подцикл выполнения команды, в течение которого дешифратор команд читает содержимое регистра команд, сообщая процессору, что делать для реализации операций команды. Число разрядов регистра команд учебного 8- разрядного процессора – 8.

3.3.7. Регистр состояния

Наличием регистра состояния подлинная ЭВМ отличается от простого калькулятора. Указанный регистр предназначен для хранения результатов некоторых проверок, осуществляемых в процессе выполнения программы. Разряды регистра состояния принимают то или иное значение при выполнении операций, использующих АЛУ и некоторые регистры.

Запоминание результатов упомянутых проверок позволяет использовать программы, содержащие переходы (нарушения естественной последовательности выполнения команд).

При наличии в программе перехода выполнение программы начинается с некоторой новой области (ячейки) памяти, т.е. счетчик команд, загружается новым числом. В случае условного перехода такое действие имеет место, если результаты определенных проверок совпадают с ожидаемыми значениями. Указанные результаты находятся в регистре состояния. Возможности программирования с передачей управления (переходами) – отличительная характеристика ЭВМ по сравнению с простыми калькуляторами. Регистр состояния предоставляет программисту возможность организовать работу процессора так, чтобы при определенных условиях менялся порядок выполнения команд. Можно сказать, что процессор принимает решение о том или ином продолжении хода вычисления в зависимости от указанных условий. Калькулятор такого решения принимать не может. Количество разрядов учебного процессора 8, назначение и функции которых аналогичны регистру состояния 16-разрядного процессора, рассмотренного выше.

3.3.8. Буферные регистры

На рис. 3.4 показаны два буферных регистра, каждый из которых предназначен для временного хранения одного слова данных. Один из этих регистров (ближайший к аккумулятору) называется буфером аккумулятора АЛУ. Что касается другого буферного регистра, то в него на временное хранение поступают данные с внутренней шины процессора. Необходимость такого регистра вызвана отсутствием в АЛУ своего запоминающего устройства. В состав АЛУ включены только комбинационные схемы, и поэтому при поступлении исходных данных на входе АЛУ немедленно появляются результирующие данные на его выходе как следствие выполнения операций данной программы.

АЛУ должно получать данные с внутренней шины процессора, модифицировать их, а затем помещать обработанные данные в аккумулятор. Но это неосуществимо без регистра временного хранения данных. Отметим особо, что буферные регистры не могут быть использованы программистом.

Если на вход описанного выше буферного регистра могут поступать данные только с внутренней шины данных процессора, то на вход другого буферного регистра (буф. аккумулятора), данные могут поступать, кроме того, и с выхода аккумулятора. Когда в

42

арифметической или логической операции АЛУ участвуют два слова, одно из них поступает из аккумулятора. Результат подобной операции помещается в аккумулятор.

3.3.9. Регистры общего назначения

Регистры предоставляемые в распоряжение пользователя или для временного хранения данных процессора получили название регистров общего назначения. Учебный процессор имеет три таких регистра: B, C, D. Выбор конкретного регистра для выполнения определенного вид работ определяется лишь тем, какой из них доступен и кажется наиболее удобным. Обычно операции, использующие эти регистры влияют на содержимое регистра состояния.

3.3.10.Схемы управления

Роль схем управления в процессоре чрезвычайно важна и заключается в

поддержании требуемой последовательности функционирования всех остальных его звеньев. По ”распоряжению” схем управления очередная команда извлекается из регистра команд, определяется, что необходимо делать с данными, а затем генерируется последовательность действий по выполнению поставленной задачи.

Обычно работа схем управления микропраграммируется. Это свидетельствует о сходстве архитектуры системы управления процессором с архитектурой некоторого процессора специального назначения. Можно сказать, что схемы управления – это маленький процессор внутри основного процессора. Одна из главных функций схемы управления – декодирование команды, находящейся в регистре команд посредством дешифратора команд. В результате дешифратор выдает на выходе сигналы, необходимые для выполнения команды. Если рассмотреть рис. 3.4 более детально, то можно увидеть, что схемы управления тянутся к каждому устройству, регистру процессора, а так же к внешним блокам: памяти и устройства ввода-вывода.

Помимо указанных выше действий, схемы управления выполняют некоторые другие специальные функции, такие как управление, последовательностью включения питания, управления процессами прерываний. Прерывание – это своего рода запрос, поступающий на схемы управления от других устройств. Прерывание связано с использованием внутренней шины данных процессора. Схемы управления принимают решения, когда и в какой последовательности другие устройства могут пользоваться внутренней шинной данных.

3.3.11.Внутренняя шина процессора

Структурная схема процессора на рис. 3.4 показывает, что 8-разрядная внутренняя

шина данных соединяет собой АЛУ и регистры, осуществляя передачу данных внутри процессора. Хотя сигналы управления и играют жизненно важную роль в процессе передачи данных по внутренней шине, тракт их передачи не принадлежит шине данных.

Каждый функциональный блок процессора всегда подключен к внутренней шине данных, однако воспользоваться ею может только после получения соответствующего сигнала от схем управления.

3.4. Схема выполнения команд простого процессора

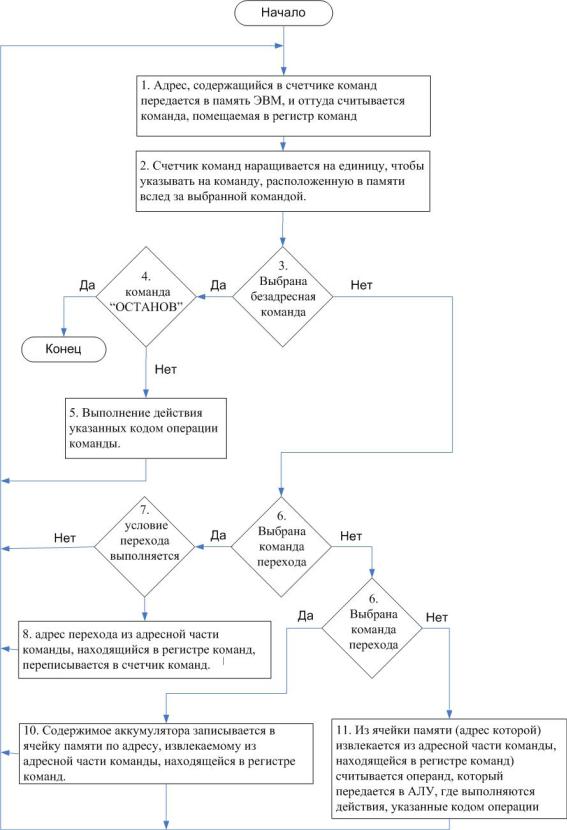

Как видно из рис. 3.5, два первых действия (блоки 1 и 2) выполняется для каждой программы. Эти действия, а также действия по определению типа команды – блоки 3, 6 и 9, обычно называют “Выборкой команды”. Последующие действия алгоритма (“Исполнение команда”) полностью зависят от того, какая это команда.

43

Рис. 3.5. Схема алгоритма выполнения команд простого процессора

3.5. Адресация информации и обработка адресов

Для расширения операционных возможностей и увеличения производительности процессора применяются различные способы адресации информации, отличающиеся

44

порядком использования и обработки адресного поля в команде (ПА), посредством которого организуется доступ к информации, хранящейся в оперативной памяти (ОП) или ПЗУ ЭВМ.

3.5.1.Непосредственная адресация

Вкоде команды (в коде одного или нескольких адресов) размещается непосредственный операнд, если число значащих цифр операнда не превышает длины адресной части команды. Такая адресация используется для хранения различного рода констант и находит широкое применении в универсальных ЭВМ в целях экономии ячеек ОП и уменьшения времени выполнения команды.

3.5.2.Прямая адресация

Исполнительный адрес – адрес ячейки ОП, в которой храниться адресуемое слово, совпадает с адресной частью команды. Этот метод используется в ЭВМ в комбинации с другими методами адресации.

3.5.3. Модификация адресов

Рассмотренные методы адресации обеспечивают адресацию переменных и констант. При решении ряда задач на ЭВМ необходимо выполнять некоторые участки программ многократно (случай циклических процессов) над различными операндами, расположенных упорядоченно в массивах ОП. Поскольку операнды, обрабатываемые при повторениях цикла, имеют разные адреса, то каждый цикл в программе можно представить в виде последовательности команд, отличающихся адресными частями. Однако при таком подходе программа решения задачи оказывается слишком длинной и ее составление чрезвычайно трудоемким.

Программирование вычислительных циклов существенно упрощается, если после каждого цикла обеспечить автоматическое изменение в соответствующих командах их адресных частей. Процедура изменения адреса в командах называется модификацией адреса. Модификация адресов команд основана на возможности выполнения над кодами команд или их частями арифметических и логических операций. В качестве операндов в командах вычислительного цикла могут фигурировать элементы массивов называемые переменными с индексами. Элемент массива представляется базовым адресом Аб и индексом i, который указывает, на сколько единиц должен быть изменен адрес команды перед ее выполнением.

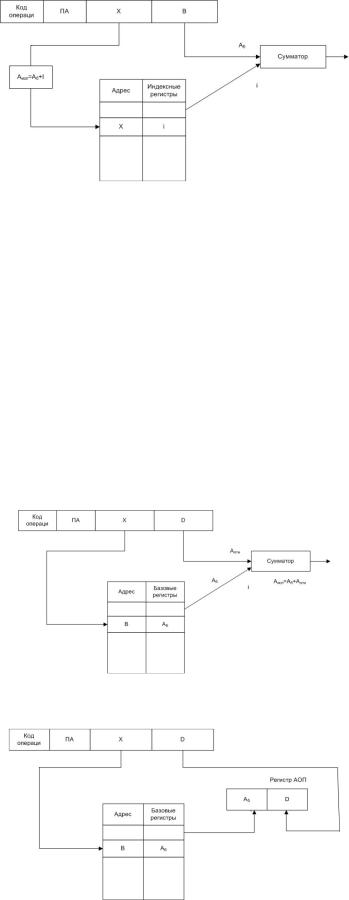

Программный способ модификации адресов в команде значительно замедляет процесс обработки переменных с индексом и требует для этих целей большой емкости оперативной памяти. В связи с этим в современных ЭВМ для модификации адресов используют аппаратные средства. В этом случае адрес в команде представляется двумя полями (Рис. 4).

В поле В указывается базовый адрес массива Аб оперативной памяти. Поле X называется индексом. Если X=0, то адрес Аб не модифицируется, т.е. является исполнительным Аисп. Значение X <> 0 определяет адрес ячейки памяти индексов, в которой храниться индекс i. Модификация адреса сводится к вычислению исполнительного адреса Аисп=Аб + (X), где (X) – содержимое ячейки X индексной памяти.

45

Рис. 4. Индексная адресация с использованием регистров. (ПА-поле адреса).

В качестве индексной памяти используют в процессоре так называемые индексные регистры СОЗУ. Суммирование производится или в АЛУ процессора или в специальном сумматоре обработке адресов.

3.5.4. Относительная адресация

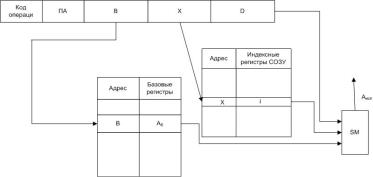

При динамическом распределении памяти базовые адреса массивов изменяются в процессе выполнения программы, в результате адреса не могут быть зафиксированы в программе. Для обеспечения динамического распределения памяти используют способ относительной адресации. Относительный адрес (рис.5) состоит из двух полей: B, указывающего базовый адрес Аб массива D. Поле D представляющего собой относительный адрес Aотн. Поле D принято называть смещением D операнда относительно начала массива. Исполнительный адрес вычисляется по формуле Аисп=(B)+D. Для хранения базовых адресов в целях повышения быстродействия ЭВМ используют так называемые базовые регистры СОЗУ.

Рис. 5.

Рис. 6.

46

При формировании Аисп на суммирование в сумматоре затрачивается некоторое время. В целях уменьшения этого времени используют так называемый метод совмещения. В этом случае в базовом регистре B (рис.6) содержаться старшие разряды, а в поле D записывают младшие разряды исполнительного адреса Аисп, которые выдаются непосредственно в регистр адреса оперативной памяти (РОАП). При совмещении, очевидно, базовый адрес Аб не может принимать значение адреса любой ячейки ОП, а только тех адресов, которые содержат в младших разрядах нули, соответствующие количеству разрядов поля D.

В универсальных ЭВМ используют совместно относительную адресацию и модификацию адресов (рис. 7). В этом случае Аисп вычисляется по формуле Аисп=(В)+(X) +D, где (B) – базовый адрес Аб (содержимое ячейки (В), (X) - индекс i (содержимое ячейки X); D- смещение операнда (относительный адрес).

Рис. 7. Формирование исполнительного адреса при относительной и индексной адресации. SMсуммирование адресов, получение относительного адреса Аотн.

3.6. Организация виртуальной памяти

Обычно при решении задач на ЭВМ только часть информации размещается во внутренней памяти, а остальная храниться во внешней памяти. Таким образом, программист имеет дело с многоуровневой памятью и, планируя процесс решения задачи, включает в программу операции, вызывающие обмен информацией между различными ЗУ. Даже при наличии систем автоматизации программирования и хорошо организованных систем управления данными, программирование задач для ЭВМ с многоуровневой памятью отличается сложностью и требует от исполнителей высокой квалификации. Особенно сложны процедуры обмена информацией между уровнями памяти, необходимые для организации мультипрограммной работы ЭВМ в режиме разделения времени. В связи с этим, в современных ЭВМ осуществляется автоматическое (не предусмотренное программой) планирование передач информации в многоуровневой памяти, основанное на построении виртуальной (воображаемой, кажущейся, фиктивной) одноуровневой памяти.

Под виртуальной памятью понимается совокупность ячеек всех ОЗУ и ВЗУ, имеющих сквозную нумерацию 0, 1, 2, 3, … (Q-1). Программирование процессов решения задач производится в терминах математических (виртуальных) адресов 0, 1, 2, 3, … (Q-1). При этом команды ссылаются на математические адреса в предположении, что слово, идентифицированное любым математическим адресом, является доступным для процессора. Таким образом, для программиста создается одноуровневая память емкостью

-Q слов. В физическом отношении виртуальная память – это совокупность оперативных

ивнешних ЗУ, охваченных средствами преобразования математических адресов в физические (действительные) адреса ячеек и автоматизации перемещения информации между устройствами памяти.

Виртуальная память - память, доступная программисту при выполнении его программы, ее размер - виртуальное пространство памяти, определяется, обычно, максимальной разрядностью исполнительного адреса команд программы. Длина адреса,

47

его разрядность, определяет пространство памяти, которое может быть доступно ("видимо") в программе. Виртуальное пространство - математическая множество адресов памяти программы может не совпадать с реальным, физическим пространством памяти ЭВМ.

3.6.1. Страничная адресация памяти

Механизмы виртуальной страничной памяти реализуются путем разбиения памяти

ивиртуальной и физической на одинаковые страницы, размером 2-4 Кбайта. Адрес разделяется на две части в соответствии с принятой длиной страницы: номер страницы (P)

иадрес внутри страницы - сдвиг, смещение (A).

Аппаратно трансляция адресов производится при помощи таблицы страниц, хранящейся в отдельной памяти. Каждой странице виртуальной памяти соответствует строка в таблице страниц, объем которой соответствует числу страниц виртуальной памяти. В i строке таблицы хранится: N страницы (блока) физической памяти, которая соответствует данной виртуальной, статус доступа (чтение, запись), признак записи. Трансляция адресов: реальный, физический адрес получается добавлением к старшей части физического адреса, полученного из таблице страниц, адреса внутри страницы (смещения).

Процессы преобразования адресов и перемещения информации наиболее просто реализуется при страничной адресации памяти. Метод страничной адресации состоит в том, что виртуальная память (как множество адресов) разделяется на страницы емкостью 2К (обычно 220-240 байт = 2-4 Кб) соседних адресов. Так, к странице с адресом 0 относятся адреса: 0, 1, 2, …, (2К-1), к странице с адресом 2К относят следующие адреса: 2К, 2К+1, 2К+2, … 2К+1-1 и так далее. В результате адрес виртуального слова будет состоять из двух полей: P- Указывающих адрес страницы, и А – адрес слова в странице Р (рис. 8).

a) виртуальный адрес, б) физический адрес Рис. 8. Адреса при страничной адресации.

Если физическую память разделить, а сегменты, состоящие из 2K соседних ячеек, то физические адреса в пределах одной виртуальной страницы по структуре будут полностью совпадать с математическими адресами (рис. 8 б), где S – адрес сегмента, а А – адрес слова (ячейки) в сегменте S. Размер страниц составляет 512-10024 слова, но в некоторых случаях возникает необходимость в использовании страниц размером 32-128 слов.

В процессе решения задачи страницы перемещаются между ОЗУ и ВЗУ. Если вычислительный процесс распределяется на страницу P, то она вызывается в ОЗУ. Когда надобность в информации, размещенной на странице P, отпадает, то она удаляется из ОЗУ в виртуальную память, освобождая место для других страниц. В результате перемещения граница P может быть помещена на любом сегменте S ОП.

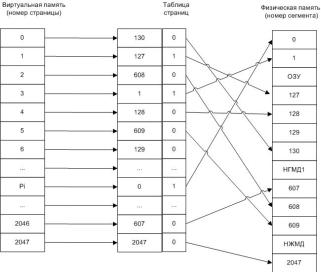

Текущее состояние памяти ЭВМ характеризуется таблицей страниц (рис. 9). Отдельной странице виртуальной памяти Pi (i=1, 2, … Q-1) соответствует одна строка таблицы, в которой указываются параметры страницы Pi: Si – адрес сегмента ОЗУ, в котором размещается страница Pi, иначе говоря, физический адрес станицы Pi; di-признак доступности страницы: di=1 страница Pi, храниться в ОЗУ и недоступна для центрального процессора.

48

Рис. 9. Пример одного из возможных порядков используемых в таблице страниц.

В таблице страниц также указываются параметры, определяющие страницу, которую надо удалить из ОЗУ (на рис. 9 эти параметры не показаны) вследствие относительно низкой вероятности ее использования. Таблица страниц размещается в ОЗУ и в любое время доступна ЦП. Как видно из рис. 9, 2048 страниц виртуальной памяти могут размещаться в 128 сегментах ОЗУ и на магнитных дисках НГМД1 и НГМД2 емкостью 960 страниц каждый.

Алгоритмы и аппаратные схемы замещения страниц Стратегии подкачек страниц (сегментов) в оперативную память.

•предписанные приоритеты (системные и внутризадачные);

•случайный выбор;

•стратегия FIFO (first-in-first-out) "первым пришел - первым ушел";

•стратегия вытеснения LRU (least recently used) по давности использования; Для реализации, иногда используются регистры старения: для каждого блока

заводится n разрядный регистр, в который при каждом обращении к страницы в старший разряд заносится 1, а через t единиц времени регистр сдвигается на 1 разряд вправо. Тогда, кандидатом на вытеснение является страница с минимальным значением регистра старения, рассматриваемого как положительное целое число.

Механизм виртуальной памяти позволяет:

•снять ограничения, связанные с объемом памяти, при разработке алгоритмов;

•предоставлять программисту область памяти в виде логически непрерывного пространства;

•способствовать более эффективному управлению физической памятью. Адреса виртуального пространства памяти - виртуальные адреса, а адреса

физического пространства - физические адреса.

Процесс преобразование виртуальных адресов в физические при выполнении программы называется трансляцией адресов, наиболее распространенный механизм для этого - сегментирование памяти и страничная организация памяти.

Страничная организация памяти используется операционной системой (ОС) для организации файла подкачки SWAP –файла (область на диске куда откачиваются не актуальные на данный момент страницы). ОС часто использует виртуальную память (страничную организацию) в процессе управления внешними устройствами, сбрасывая в SWAP, буферы и прочие области служебную информацию и данные. При написании крупных программных комплексов, программисты так же использую станичную организацию памяти для написания оптимальных, и эффективных программ.

49

3.6.2. Сегментация памяти

Другой подход к организации памяти опирается на тот факт, что программы обычно разделяются на отдельные области-сегменты. Каждый сегмент представляет собой отдельную логическую единицу информации, содержащую совокупность данных или программ и расположенную в адресном пространстве пользователя. Сегменты создаются пользователями, которые могут обращаться к ним по символическому имени. В каждом сегменте устанавливается своя собственная нумерация слов, начиная с нуля.

Обычно в подобных системах обмен информацией между пользователями строится на базе сегментов. Поэтому сегменты являются отдельными логическими единицами информации, которые необходимо защищать, и именно на этом уровне вводятся различные режимы доступа к сегментам. Можно выделить два основных типа сегментов: программные сегменты и сегменты данных (сегменты стека являются частным случаем сегментов данных). Поскольку общие программы должны обладать свойством повторной входимости, то из программных сегментов допускается только выборка команд и чтение констант. Запись в программные сегменты может рассматриваться как незаконная и запрещаться системой. Выборка команд из сегментов данных также может считаться незаконной, и любой сегмент данных может быть защищен от обращений по записи или по чтению.

Для реализации сегментации было предложено несколько схем, которые отличаются деталями реализации, но основаны на одних и тех же принципах.

В системах с сегментацией памяти каждое слово в адресном пространстве пользователя определяется виртуальным адресом, состоящим из двух частей: старшие разряды адреса рассматриваются как номер сегмента, а младшие – как номер слова внутри сегмента. Наряду с сегментацией может также использоваться страничная организация памяти. В этом случае виртуальный адрес слова состоит из трех частей: старшие разряды адреса определяют номер сегмента, средние – номер страницы внутри сегмента, а младшие – номер слова внутри страницы.

Как и в случае страничной организации, необходимо обеспечить преобразование виртуального адреса в реальный физический адрес основной памяти. С этой целью для каждого пользователя операционная система должна сформировать таблицу сегментов. Каждый элемент таблицы сегментов содержит описатель (дескриптор) сегмента (поля базы, границы и индикаторов режима доступа). При отсутствии страничной организации поле базы определяет адрес начала сегмента в основной памяти, а граница длину сегмента. При наличии страничной организации поле базы определяет адрес начала таблицы страниц данного сегмента, а граница – число страниц в сегменте. Поле индикаторов режима доступа представляет собой некоторую комбинацию признаков блокировки чтения, записи и выполнения.

Таблицы сегментов различных пользователей операционная система хранит в основной памяти. Для определения расположения таблицы сегментов выполняющейся программы используется специальный регистр защиты, который загружается ОС перед началом ее выполнения. Этот регистр содержит адрес начала таблицы сегментов выполняющейся программы, а граница – длину этой таблицы сегментов. Разряды номера сегмента виртуального адреса используются в качестве индекса в таблице сегментов. Таким образом, наличие базово-граничных пар в дескрипторе таблицы сегментов и элементов таблицы сегментов предотвращает возможность обращения программы пользователя к таблицам сегментов и страниц, с которыми она не связана. Наличие в элементах таблицы сегментов индикаторов режима доступа позволяет осуществить необходимый режим доступа к сегменту со стороны данной программы. Для повышения эффективности схемы используется ассоциативная кэш-память.

Отметим, что в описанной схеме сегментации таблица сегментов с индикаторами доступа представляет всем программам, являющимся частями некоторой задачи, одинаковые возможности доступа, т.е. она определяет единственную область (домен)

50