МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

Федеральное государственное бюджетное образовательное учреждение

высшего профессионального образования

«Московский государственный технический университет

имени Н.Э. Баумана»

(МГТУ им. Н.Э. Баумана)

Факультет «Робототехника и комплексная автоматизация» (РК)

Кафедра «Системы автоматизированного проектирования» (РК6)

Отчет

по домашним лабораторным работам

по дисциплине

«Организация ЭВМ и систем»

Вариант №6

Выполнил: Куликов П.А.

группа РК6-93

Москва 2012

Разработка VHDL-описания последовательных схем

с регулярной структурой

Тип синтезируемого устройства: Регистр сдвига на синхронных двухступенчатых D-триггерах с разнополярным управлением

-

Структурное описание

Компонент И-НЕ с двумя входами

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity and2 is

port (

X1: in STD_LOGIC;

X2: in STD_LOGIC;

Y: out STD_LOGIC

);

end and2;

architecture and2 of and2 is

begin

Y <= not (X1 and X2);

end and2;

Компонент И-НЕ с тремя входами

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity and3 is

port (

X1: in STD_LOGIC;

X2: in STD_LOGIC;

X3: in STD_LOGIC;

Y: out STD_LOGIC

);

end and3;

architecture and3 of and3 is

begin

Y <= not (X1 and X2 and X3);

end and3;

Компонент ИЛИ-НЕ с двумя входами

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity or2 is

port (

X1: in STD_LOGIC;

X2: in STD_LOGIC;

Y: out STD_LOGIC

);

end or2;

architecture or2 of or2 is

begin

Y <= not (X1 or X2);

end or2;

Компонент ИЛИ-НЕ с тремя входами

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity or3 is

port (

X1: in STD_LOGIC;

X2: in STD_LOGIC;

X3: in STD_LOGIC;

Y: out STD_LOGIC

);

end or3;

architecture or3 of or3 is

begin

Y <= not (X1 or X2 or X3);

end or3;

Компонент НЕ

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity inv is

port (

X: in STD_LOGIC;

Y: out STD_LOGIC

);

end inv;

architecture inv of inv is

begin

Y <= not (X);

end inv;

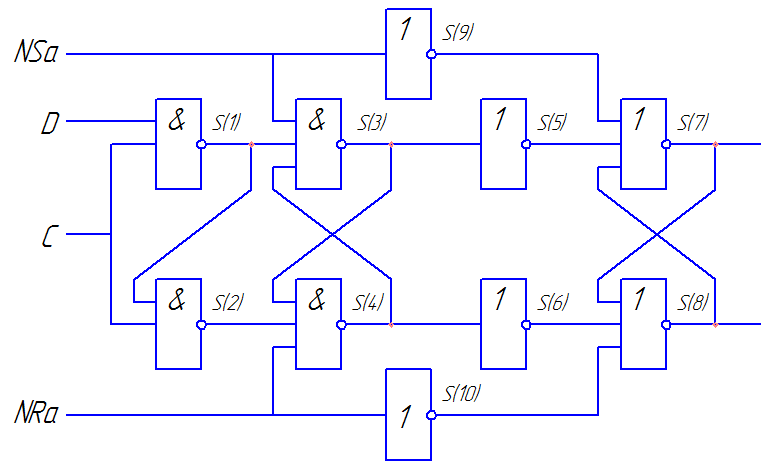

Синхронный двухступенчатый D-триггер с разнополярным управлением

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity trig is

port (

NSa: in STD_LOGIC;

D: in STD_LOGIC;

C: in STD_LOGIC;

NRa: in STD_LOGIC;

Q: out STD_LOGIC;

NQ: out STD_LOGIC

);

end trig;

architecture trig of trig is

component inv is

port (

X: in STD_LOGIC;

Y: out STD_LOGIC

);

end component;

component and2 is

port (

X1: in STD_LOGIC;

X2: in STD_LOGIC;

Y: out STD_LOGIC

);

end component;

component and3 is

port (

X1: in STD_LOGIC;

X2: in STD_LOGIC;

X3: in STD_LOGIC;

Y: out STD_LOGIC

);

end component;

component or2 is

port (

X1: in STD_LOGIC;

X2: in STD_LOGIC;

Y: out STD_LOGIC

);

end component;

component or3 is

port (

X1: in STD_LOGIC;

X2: in STD_LOGIC;

X3: in STD_LOGIC;

Y: out STD_LOGIC

);

end component;

signal S: STD_LOGIC_VECTOR(1 to 10);

begin

S1: and2 port map (D, C, S(1));

S2: and2 port map (S(1), C, S(2));

S3: and3 port map (NSa, S(1), S(4), S(3));

S4: and3 port map (NRa, S(2), S(3), S(4));

S9: inv port map (NSa, S(9));

S10: inv port map (NRa, S(10));

S5: or2 port map (S(3), C, S(5));

S6: or2 port map (S(4), C, S(6));

S7: or3 port map (S(9), S(5), S(8), S(7));

S8: or3 port map (S(10), S(6), S(7), S(8));

Q <= S(7);

NQ <= S(8);

end trig;

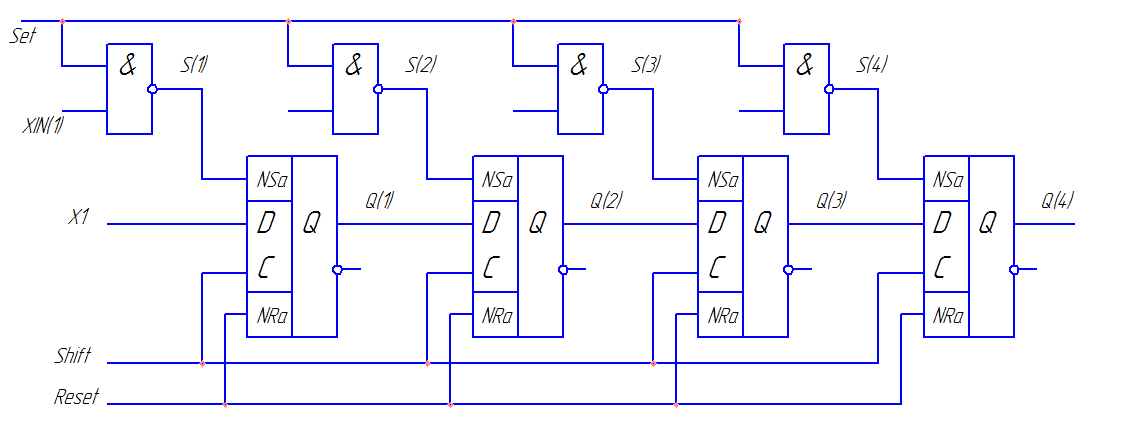

Регистр сдвига

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity reg is

generic (

N: integer := 4

);

port (

XIN: in STD_LOGIC_VECTOR(N downto 1);

X1: in STD_LOGIC;

Set: in STD_LOGIC;

Reset: in STD_LOGIC;

Shift: in STD_LOGIC;

QOUT: out STD_LOGIC_VECTOR(N downto 1)

);

end reg;

architecture reg of reg is

component trig

port (

NSa: in STD_LOGIC;

D: in STD_LOGIC;

C: in STD_LOGIC;

NRa: in STD_LOGIC;

Q: out STD_LOGIC;

NQ: out STD_LOGIC

);

end component;

component and2 is

port (

X1: in STD_LOGIC;

X2: in STD_LOGIC;

Y: out STD_LOGIC

);

end component;

signal S,Q,NQ: STD_LOGIC_VECTOR(N downto 1);

begin

INPUT: for i in 1 to N generate

NUMi: and2 port map (Set, XIN(i), S(i));

end generate;

TRIG_1: trig port map (S(1), X1, Shift, Reset, Q(1), NQ(1));

TRIG_N: for i in 2 to N generate

TRIGi: trig port map (S(i), Q(i-1), Shift, Reset, Q(i), NQ(i));

end generate;

QOUT <= Q;

end reg;

Временные диаграммы

Поведенческое описание

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity reg2 is

generic (

N: integer := 4

);

port (

XIN: in STD_LOGIC_VECTOR(N downto 1);

X1: in STD_LOGIC;

Set: in STD_LOGIC;

Reset: in STD_LOGIC;

Shift: in STD_LOGIC;

QOUT: out STD_LOGIC_VECTOR(N downto 1)

);

end reg2;

architecture reg2 of reg2 is

signal state : STD_LOGIC_VECTOR(N downto 1);

begin

process(Set, Shift, Reset)

begin

if (Reset = '0') then

for i in 1 to N loop state(i) <= '0';

end loop;

elsif (Set = '1') then

state <= XIN;

elsif(Shift = '0') and (Shift'last_value = '1') then

for i in N downto 2 loop

state(i) <= state(i-1);

end loop;

state(1) <= X1;

end if;

end process;

QOUT <= state;

end reg2;

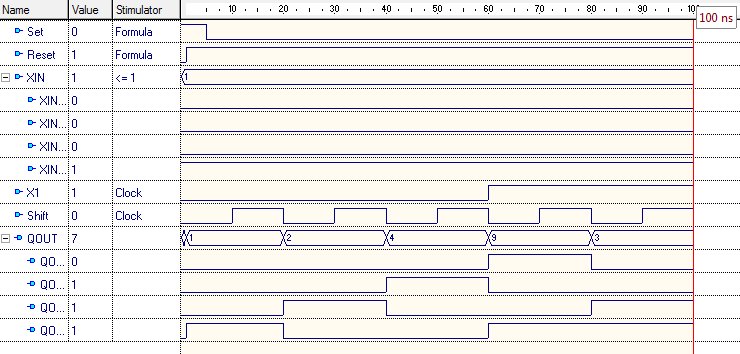

Временные диаграммы

Управляющие автоматы

Таблица задания функционирования конечного автомата:

|

Входные сигналы |

Состояния |

|||

|

a1 |

a2 |

a3 |

a4 |

|

|

z1 |

a3 / w4 |

a2 / w1 |

a1 / w2 |

a1 / w4 |

|

z2 |

a4 / w4 |

a2 / w3 |

a4 / w3 |

a2 / w3 |

|

z3 |

a3 / w5 |

a1 / w4 |

a1 / w4 |

a3 / w1 |

Поведенческое описание

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity avtomat is

port(

clock: in STD_LOGIC;

reset: in STD_LOGIC;

DIN: in STD_LOGIC_VECTOR(0 to 1);

DOUT: out STD_LOGIC_VECTOR(0 to 2)

);

end avtomat;

architecture avtomat of avtomat is

type state_values is (a1,a2,a3,a4);

signal state, next_state: state_values;

begin

s1: process(clock, reset)

begin

if (reset = '0') then state <= a1;

elsif (clock'event and clock = '1') then state <= next_state;

end if;

end process s1;

s2: process(state, DIN)

begin

case state is

when a1 =>

case DIN is

when "01" => DOUT <= "100";

next_state <= a3;

when "10" => DOUT <= "100";

next_state <= a4;

when "11" => DOUT <= "101";

next_state <= a3;

when others => DOUT <= "000";

next_state <= a1;

end case;

when a2 =>

case DIN is

when "01" => DOUT <= "001";

next_state <= a2;

when "10" => DOUT <= "011";

next_state <= a2;

when "11" => DOUT <= "100";

next_state <= a1;

when others => DOUT <= "000";

next_state <= a1;

end case;

when a3 =>

case DIN is

when "01" => DOUT <= "010";

next_state <= a1;

when "10" => DOUT <= "011";

next_state <= a4;

when "11" => DOUT <= "101";

next_state <= a1;

when others => DOUT <= "000";

next_state <= a1;

end case;

when a4 =>

case DIN is

when "01" => DOUT <= "100";

next_state <= a1;

when "10" => DOUT <= "011";

next_state <= a2;

when "11" => DOUT <= "001";

next_state <= a3;

when others => DOUT <= "000";

next_state <= a1;

end case;

when others => DOUT <= "000";

next_state <= a1;

end case;

end process s2;

end avtomat;

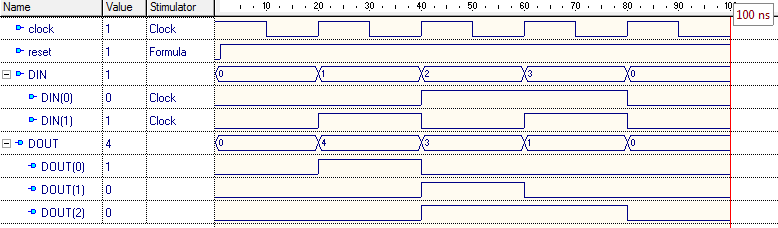

Временные диаграммы