- •Пояснительная записка к курсовому проекту по дисциплине “оэвм” Содержание

- •Задание

- •Общая структура эвм

- •Организация команд и данных в памяти.

- •Блок основной памяти.

- •Контроллер прерываний.

- •Кэш команд и данных.

- •Клавиатура и монитор.

- •Ввод/вывод.

- •Таймер.

- •Блок синхронизации

- •Центральный процессор

- •Операционный блок.

- •Микропрограммное устройство управления.

- •Разрабатываемый блок: Арифметический сопроцессор.

- •Алгоритм операции умножения.

- •Алгоритм операции деления.

- •Выводы.

- •Список используемой литературы

Пояснительная записка к курсовому проекту по дисциплине “оэвм” Содержание

ЗАДАНИЕ 2

Общая структура ЭВМ 3

Организация команд и данных в памяти. 4

Блок основной памяти. 4

Контроллер прерываний. 5

Кэш команд и данных. 6

Клавиатура и монитор. 6

Ввод/вывод. 6

Таймер. 7

Блок синхронизации 7

Центральный процессор 7

Разрабатываемый блок: Арифметический сопроцессор. 11

Алгоритм операции умножения. 11

Алгоритм операции деления. 11

Выводы. 13

Список используемой литературы 13

Задание

Разработать ЭВМ в следующем составе :

- центральный процессор

- память

- блок синхронизации

- система прерываний

- таймер

- система ввода - вывода

- монитор

- клавиатура.

Разрабатываемая ЭВМ должна быть двухадресной, иметь переменную длину команды. Разрядность ЭВМ - не менее 16. Емкость ОП - не менее 128 Кбайт.

Магистраль: двухшинная

Система прерываний: последовательная, макроуровень

КЭШ: команд и данных

Ввод - вывод: программный

Разрабатываемый блок:

- арифметический сопроцессор (операции умножения и деления).

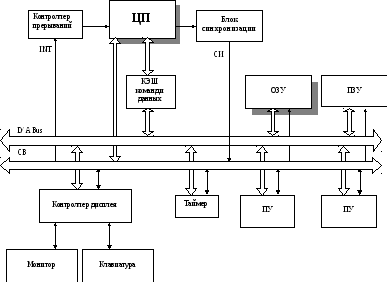

Общая структура эвм

Общая структура разрабатываемой ЭВМ приведена на рисунке 1. Организация ЭВМ – двухшинная: имеется шина Данных/Адреса (D/A Bus) и шина управления (СВ). При этом 16-ти разрядная шина D/A используется для передачи как данных, так и адреса за счет мультиплексирования во времени.

рис. 1

Общая структура разрабатываемой ЭВМ приведена на рисунке 1. Организация ЭВМ – двухшинная: имеется шина Данных/Адреса (D/A Bus) и шина управления (СВ). При этом 16-ти разрядная шина D/A используется для передачи как данных, так и адреса за счет мультиплексирования во времени.

Разрядность ЭВМ - 16, объем ОЗУ 640 Кслов с возможностью расширения.

В состав ЦП входят операционный блок, микропрограммное устройство управления, арифметический сопроцессор.

Контроллер прерываний может последовательно обрабатывать прерывания на макроуровне. Управление контроллером осуществляет ЦП.

Дисплей, состоящий из клавиатуры и монитора, служит для ввода и отображения информации. Взаимодействие ЦП с дисплеем осуществляется через системную шину.

Организация команд и данных в памяти.

Блок памяти состоит из ОЗУ и ПЗУ. Организация ОЗУ- 640К 16, организация ПЗУ- 64 К 16.

Разрядность команды - переменная. Определяется типом команды. Например, для команды типа регистр-регистр размер составляет 16 бит, а для остальных - 32 бита. Команда читается из памяти в два приема: сначала первые 16 разрядов, затем вторые 16 разрядов (т.к. шина данных 16-разрядная) и управление чтением команды из памяти осуществляется микропрограммно.

Разрядность данных - 16 бит, данные читаются и записываются в память 16-разрядными словами.

Блок основной памяти.

Блок основной памяти состоит из ПЗУ объемом 64 Кслов и ОЗУ объемом 640 Кслов. Из-за малой разрядности шины D/A выбран вариант базовой адресации основной памяти.

Адресное пространство разбито на банки памяти объемом по 64 Кслова. Базовый адрес, т.е. номер банка памяти расположен в базовом регистре. Под эти цели выделен специальный регистр в регистровом файле микропроцессорной секции. При обращении к памяти вначале в базовый регистр памяти RG BASE заносится база (или номер банка памяти). Далее этот адрес дешифрируется и с помощью сигнала CS выбирается банк памяти. По шине адреса/данных передается смещение в выбранном банке и производится операция чтения/записи в память.

Первый банк памяти занимает ПЗУ, следующие 10 - ОЗУ.

Управление регистром RG BASE и дешифратором DC BASE осуществляется с помощью сигналов управления по шине управления из ЦП.

Операция (либо чтение, либо запись) выбирается с помощью сигнала управления “W/R” из ЦП. Этот сигнал подается на все входы ОЗУ и ПЗУ. При попытке записи данных в ПЗУ оно сигналом “W/R” устанавливает свои выходы в третье состояние и таким образом запись невозможна.

При данной организации ОП существует возможность наращивания объема ОП путем добавления новых банков. В разрабатываемой структуре используется 11 банков памяти, т.е. 4 разряда базового регистра. Используя 16 разрядов базового регистра можно адресовать до 4 Гслов памяти.