- •Цель работы

- •Задание

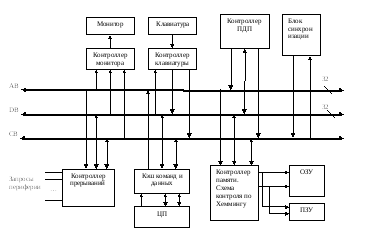

- •Разработка и описание структурной схемы

- •Центральный процессор

- •Первое слово команды

- •Второе слово команды

- •Оперативная память

- •Контроль памяти по Хеммингу

- •Система прерываний

- •Блок синхронизации и таймер

- •Прямой доступ к памяти (пдп)

- •Основные устройства ввода/вывода Клавиатура

- •Монитор

- •Жесткий диск

- •Разработка функциональной схемы кэш памяти команд и данных

- •Принцип работы схемы кэш памяти

- •Приложение

|

Министерство образования и науки Российской Федерации Федеральное агентство по образованию ГОУ ВПО Новосибирский государственный технический университет | |

|

Курсовой проект по дисциплине «Организация ЭВМ» «Разработка ЭВМ»

| |

|

Группа: АМ-610 Выполнил: Абалов Н. В. |

Преподаватель: Гребенников В.Ф. |

|

Новосибирск 2009 | |

Оглавление

1. Цель работы 3

2. Задание 3

3. Разработка и описание структурной схемы 4

4. Центральный процессор 4

5. Оперативная память 6

6. Контроль памяти по Хеммингу 7

7. Система прерываний 8

8. Блок синхронизации и таймер 10

9. Прямой доступ к памяти (ПДП) 10

10. Основные устройства ввода/вывода 12

Клавиатура 12

Монитор 13

Жесткий диск 13

11. Разработка функциональной схемы КЭШ памяти команд и данных 13

Принцип работы схемы КЭШ памяти 15

12. Приложение 17

Цель работы

Целью курсового проектирования является углубление и закрепление теоретических знаний студентов, приобретение навыков разработки узлов ЭВМ на структурном, функциональном и алгоритмическом уровнях.

Задание

Курсовой проект посвящен разработке структурной схемы гипотетической ЭВМ, функциональной схемы и алгоритма работы конкретного блока, входящего в состав этой ЭВМ.

В состав ЭВМ входят следующие блоки:

операционный блок (ОБ);

микропрограммное устройство управления (МУУ);

оперативная память (ОП);

блок синхронизации (БС);

система прерывания программ (СПП);

таймер;

система ввода-вывода (СВВ);

монитор, клавиатура, мышь;

жесткий диск.

Основные параметры ЭВМ:

- адресность ЭВМ - двухадресная;

- длина команды – переменная;

- разрядность - не менее 16;

Индивидуальные исходные данные на выполнение курсового проекта:

Структура: трех шинная;

Сопроцессор: нет;

Система прерываний: радиальная, макроуровень;

Кэш: объединенный кэш команд и данных;

Оперативная память: многоблочная;

Ввод/вывод: ПДП;

Контроль ОП: по коду Хемминга;

Блок для разработки: Кэш;

Разработка и описание структурной схемы

Совокупность шин, объединяющих между собой основные устройства ЭВМ, образует структуру взаимосвязей ЭВМ. В соответствии с заданием структура трехшинная:

DB(шина данных) – обеспечивает обмен данными между всеми основными блоками ЭВМ (разрядность шины: 32);

АВ (шина адреса) – используется для задания адреса памяти. Причем адреса ОЗУ, ПЗУ, и адрес видеопамяти контроллера монитора задаются одинаково, отличить их можно по диапазонам (разрядность шины: 32);

СВ (шина управления) – обеспечивает передача сигналов управления между различными блоками ЭВМ.

Такой подход обеспечивает три типа передачи данных:

Передача между центральным процессором и памятью;

Передача между центральным процессором и модулями ввода/вывода;

Передача между памятью и модулями ввода/вывода;

Рисунок 1 – Структурная схема ЭВМ

Центральный процессор

Процессор является основным блоком ЭВМ и представляет собою объединение операционного блока (ОБ) и микропрограммного устройства управления (МУУ).

Каждый из блоков выполняет свою функцию. Операционный блок отвечает за арифметические, логические и сдвиговые операции. Операционный блок можно разбить на несколько блоков: АЛУ (арифметико-логическое устройство), файл регистров общего назначения, блок логики сдвигов, статусный регистр для хранения слова состояния процессора. Для взаимодействия с шинами AB и DB используются буферные регистры (регистр входных данных, регистр выходных данных, адресный регистр).

МУУ отвечает за управление ОБ, памяти и всей ЭВМ в целом. МУУ преобразует входные команды в набор микрокоманд, которые последовательно передает управляемым блокам. Обработку команды можно разбить на следующие этапы:

Команда поступает в МУУ, из команды извлекается код операции (КОП)

КОП поступает на преобразователь начального адреса (ПНА)

Полученный адрес передается в секвенсор

Секвенсор передает адрес в микропрограммную память (МПП), полученная микрокоманда записывается регистр

Секвенсор формирует адрес следующей микрокоманды.

В качестве элементной базы выберем серию Am293xx (АЛУ Am29332 (имеет встроенный сдвигатель), регистрового файла Am29334, секвенсора микрокоманд Am29331).

Структура микро ЭВМ обеспечивает выполнение следующих типов операций:

регистр - регистр

регистр - память

память – регистр

Условные обозначения:

КОП– код операции. Кодирует код выполняемой операции. При длине поля в 9 бит можно закодировать 512 различных операций

RG1– регистр источник/приемник,RG2– регистр источник

P– Направление и величина сдвига для сдвиговых операций, или позиция для операндов представляющих собой битовые поля переменной ширины

W– Ширина байтового поля для операндов представляющих собой битовые поля переменной ширины

Команда типа регистр – регистр:

|

КОП |

RG1 |

RG2 |

P |

W | |||||

|

31 |

23 |

22 |

17 |

16 |

11 |

10 |

5 |

4 |

0 |

Оба операнда находятся во внутренних регистрах регистрового файла, адреса которых определены двумя 6-разрядными полями микрокоманды. Это позволяет адресовать все 64 регистра регистрового файла Am29334.

Поле КОП задает код операции, которая будет выполняться АЛУ над операндами.

Команда типа ОЗУ – регистр (регистр - ОЗУ):

|

КОП |

RG1 |

RG2 |

P |

W | |||||

|

31 |

23 |

22 |

17 |

16 |

11 |

10 |

5 |

4 |

0 |