фоэ,1ч

.pdf

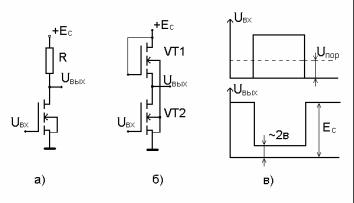

вый и коллекторный токи нарастают. Потенциал точки “а” ϕа увеличивается,

а точки “к” ϕк уменьшается. Когда ϕа станет больше ϕк, диод откроется, и благодаря ООС произойдет фиксация напряжения на переходе коллекторбаза, не позволяя коллекторному переходу открыться, а транзистору войти в режим насыщения. В активном режиме накопления носителей в базе не происходит и, следовательно, время на их рассасывание при выключении ключа (tз) будет равно нулю.

Рис. 5.7

При отсутствии компенсирующего резистора R', падение напряжения на котором действует встречно с прямым напряжением диода, при открытом диоде коллекторный переход транзистора все равно был бы открыт и транзистор находился бы в режиме насыщения, т.к.

Uбк = Uпр д > Uпор .

При разработке цифровых интегральных микросхем широко используют ключи с нелинейной обратной связью, образованной с помощью диода Шоттки, имеющего прямое падение напряжения Uпр Ш ≈ 0,3 В - меньшее, чем падение напряжения на кремниевом переходе Uкр ≈ 0,7 В, (рис. 5.7, в). Тогда необходимость в компенсирующем резисторе R' отпадает. Прямое падение напряжения на диоде Шоттки приложено в прямом направлении и к коллекторному переходу, но т.к. оно меньше порогового для кремниевого перехода (Uкр = 0,6 В), то, когда диод Шоттки открыт, коллекторный переход транзистора остается обратно смещенным, и транзистор в режим насыщения не входит.

50

Остаточное выходное напряжение замкнутого ключа с диодом Шоттки равно Uост = Uбэ – Uдш = 0,7 – 0,3 = 0,4 В, т.е. несколько выше, чем у на-

сыщенного ключа, где Uост ≈ 0,2 В.

Комбинация кремниевого транзистора и диода Шоттки в цепи обратной связи, выполненная в едином технологическом цикле, называется транзистором Шоттки, условное обозначение которого приведено на рис. 5.7, в.

5.6. Ключевой режим работы МДПтранзистора

Простейшая схема электронного ключа на МДП-транзисторе с индуцированным п-каналом изображена на рис. 5.8, а. Следует заметить, что при производстве интегральных микросхем все пассивные элементы схем (резисторы, конденсаторы) изготавливают в едином технологическом цикле на базе соответствующих биполярных или полевых транзисторных структур. Широко распространенный вариант построения резистора на базе МДПструктуры VT1 изображен на рис. 5.8, б. При соединении затвора со стоком

МДП-структура выполняет роль резистора при условии, что Uc > Uпор. Схема такого электронного ключа изображена на рис. 5.8, б, а диаграмма его работы - на рис. 5.8, в. Если подаваемое на затвор ключевого транзистора VT2 напряжение меньше порогового, то транзистор VT2 закрыт, а нагрузочный транзистор VT1 - всегда открыт, поэтому напряжение на выходе близко к на-

пряжению источника питания Ес. При подаче на вход ключа напряжения, больше порогового, транзистор VT2 открывается, в стоковой выходной цепи потечет ток и напряжение на выходе будет зависеть от соотношения между сопротивлениями каналов открытых транзисторов VT1 и VT2. Открытый МДП-транзистор имеет довольно большое сопротивление, и в этом случае выполнить условие минимального падения напряжения на ключе непросто.

Рис 5.8

Для получения возможно меньшего напряжения на выходе необходимо, чтобы сопротивление ключевого транзистора VT2 было гораздо меньше сопротивления нагрузочного транзистора VT1. Для этого при изготовлении

51

микросхемы области стока и истока у нагрузочного транзистора располагают на большем расстоянии. Длина канала, а значит и сопротивление, у такого транзистора получается больше, чем у ключевого.

Однако и эта мера не позволяет получить большое различие в величине сопротивлений открытых однотипных транзисторов, поэтому напряжение на выходе рассматриваемой ключевой схемы в состоянии «включено» довольно велико и составляет примерно 2 В.

Указанный недостаток устранен в электронном ключе на комплементарных МДП-парах (КМДП или КМОП). КМОП-пара представляет собой два МОПтранзистора с изолированными затворами и индуцированными p- и n- каналами. Нагрузочным элементом ключа является МОП-транзистор с противоположным типом канала. Входной сигнал управляет не только ключевым, но и нагрузочным транзистором, т.к. их затворы объединены, рис. 5.9.

в) г)

Рис. 5.9

В данной схеме n-канальный транзистор VT2 выполняет роль ключа, а р-канальный VT1 -роль нагрузки. При подаче на вход высокого уровня напряжения, большего порогового уровня, n-канальный транзистор VT2 открыт. При этом потенциал затвора р-канального транзистора VT1 близок к потенциалу его истока (Uзи р-канального транзистора VT1 меньше порогового уровня) и нагрузочный транзистор VT1 закрыт. Это статическое состояние можно представить рисунком 5.9, в. Напряжение на выходе такой схемы близко к нулю. При подаче на вход схемы напряжения, близкого к нулю, ключевой транзистор VT2 закроется, нагрузочный VT1 откроется. Это статическое состояние можно представить рисунком 5.9, г. Напряжение на выходе

такой схемы близко к напряжению источника питания Ес. Таким образом, в ключе на КМОП-паре требования, предъявляемые к ключевой схеме, выполнены максимально. Из анализа работы схемы видно, что в КМОП-паре, когда один транзистор открыт, другой - закрыт и наоборот. Это значит, что в обоих статических состояниях цепь источника питания всегда разомкнута и поэто-

52

му от источника питания в статическом режиме схема практически не потребляет ток.

5.7. Порядок выполнения работы

Для выполнения лабораторной работы используются базовый блок, лабораторный макет, 9 проводников, транзисторы низкочастотный и высокочастотный, резисторы 1,6 кОм – 2 шт., 4,3 кОм –2 шт, конденсаторы 1000 пФ

и390 или 510 пФ, двухлучевой осциллограф.

5.7.1.Исследование статических состояния ключа

а) соберите схему транзисторного ключа, рис. 5.10: на лабораторном макете к гнездам 1 и 2 подключите генератор импульсов ГПИ2, к гнездам 6 и 8 подключите резистор 4,3 кОм, к гнездам 9 и 10 подключите резистор 20 кОм, к гнездам 11 (+) и 12 (–) подключите источник ИН1, к гнездам 24 и 25 подключите резистор 1,6 кОм, к гнездам 28 (–) и 29 (+) подключите источник напряжения ИН2, соедините гнезда 13 и 14, 19 и 23, 17 и 18, к гнездам 3 и 4 подключите вход осциллографа Y1, а к 26 и 27 вход Y2. Включите в схему низкочастотный транзистор;

Рис. 5.10

б) на базовом блоке на приборе 2 нажмите клавишу «Частота» – «20». Выведите ручки регулировки частоты «Грубо» и «Точно» и ручку «Уровень» вправо до конца, тумблер перевести в положение "  " Ручку регулировки источника напряжения ИН1 выведите вправо до конца, а ИН2 – влево;

" Ручку регулировки источника напряжения ИН1 выведите вправо до конца, а ИН2 – влево;

в) на осциллографе ручки усиления установите в положение примерно 5 В/дел. для обоих лучей, а ручку развертки – примерно 5 μs/дел. Включите осциллограф и базовый блок;

53

г) подайте напряжение на коллектор ручкой «Грубо» источника ИН2 10 вольт (два деления на осциллографе);

д) зарисуйте осциллограммы напряжений на входе и выходе ключа, строго совместив их во времени;

е) измерьте и обозначьте на рисунке длительность отрицательного входного импульса, напряжения на коллекторе в режиме насыщения и отсечки транзистора, амплитуду выходного импульса, время включения, время задержки и время выключения ключа.

5.7.2. Исследование влияния элементов схемы на быстродействие ключа

а) подключите в схеме к гнездам 5 и 7 ускоряющий конденсатор 390 пФ. Измерьте и запишите время включения, задержки и выключения. Сравните эти значения с аналогичными в п. 5.7.1. е). Осциллограмму выходного напряжения совместите во времени с входной;

б) выключите базовый блок, уберите ускоряющий конденсатор и включите в схему высокочастотный транзистор. Измерьте и запишите время включения, задержки и выключения. Сравните эти значения с аналогичными значениями в п. 5.7.1. е). Осциллограмму выходного напряжения совместите во времени с входной;

в) подключите снова в схеме к гнездам 5 и 7 ускоряющий конденсатор 390 пФ и зарисуйте форму выходного напряжения в схеме с высокочастотным транзистором и ускоряющим конденсатором. Осциллограмму выходного напряжения совместите во времени с входной. Измерьте и запишите время включения, задержки и выключения. Сравните эти значения с аналогичными значениями в п. 5.7.1. е).

5.7.3. Исследование влияния нагрузки на работу ключа

а) в схему, собранную в п.5.7.2. в), подключите к выходу резистор 1,6 кОм. Зарисуйте форму напряжения на выходе и измерьте амплитуду выходных импульсов;

б) подключите к выходу резистор 4,3 кОм. Зарисуйте форму напряжения на выходе и измерьте амплитуду выходных импульсов;

в) подключите к выходу ключа конденсатор емкостью 1000 пФ. Зарисуйте форму напряжения на выходе и измерьте длительности фронтов выходных импульсов.

5.8. Выполнение работы с использованием программы моделирования электронных устройств “Electronics Workbench”

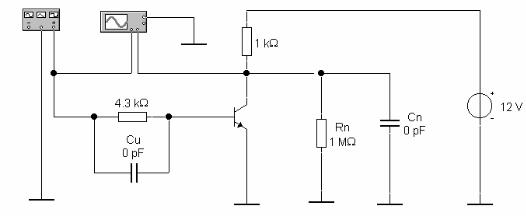

5.8.1. Соберите схему для исследования транзисторного электронного ключа, приведенную на рис. 5.11. Тип транзистора указывает преподаватель.

54

Здесь Cu – ускоряющий конденсатор, а Rn и Cn – сопротивление и емкость нагрузки. При указанных на схеме первоначальных параметрах эти элементы на работу устройства не влияют.

5.8.2. Установите форму выходного напряжения функционального генератора – прямоугольный импульс, частоту колебаний 100 кГц, амплитуду 2 В. Активизируйте схему и зарисуйте осциллограммы напряжений на входе и выходе ключа, строго совместив их по времени.

Рис. 5.11

5.8.3.Определите длительность входного импульса, напряжения на коллекторе в режиме насыщения и отсечки транзистора, амплитуду выходного импульса, время включения, время задержки и время выключения ключа.

5.8.4.Для исследования влияния элементов схемы на быстродействие ключа установите емкость ускоряющего конденсатора Cu 100 пФ. Измерьте и запишите время включения, задержки и выключения ключа. Сравните полученные значения с соответствующими, полученными в п. 5.8.3. Сделайте выводы.

5.8.5.Для исследования влияния на работу ключа нагрузки установите сопротивление нагрузки Rn 1 кОм. Зарисуйте форму напряжения на выходе устройства и определите амплитуду выходных импульсов. Сделайте выводы.

5.8.6.Установите емкость конденсатора нагрузки Cn 1000 пФ. Зарисуйте форму напряжения на выходе устройства и определите длительность фронтов выходных импульсов. Сделайте выводы.

5.9.Содержание отчета

Вотчете приведите схему ключа с указанием номинальных значений элементов, осциллограммы выходных напряжений, снятых в пунктах 5.7.1, д), е), 5.7.2, в), 5.7.3, а), б), в), совместив их во времени с входным сигналом (все осциллограммы разместите на одной странице). Результаты опытов

55

5.7.3, а), б), в), подтвердите расчетами. Сделайте выводы с краткими теоретическими пояснениями по следующей схеме:

–опишите исходные осциллограммы напряжений;

–отразите, какие параметры вы изменили в исследуемой схеме;

–опишите, как изменилась осциллограмма выходного напряжения со ссылкой на рисунок;

–ответьте на вопрос, почему произошли отмеченные изменения в осциллограмме (приведите формулы, дайте краткие теоретические объяснения, подтвердите расчетом и пр.)

ЛАБОРАТОРНАЯ РАБОТА № 6

ИССЛЕДОВАНИЕ ИНТЕГРАЛЬНЫХ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ

Цель работы: определение порогов срабатывания логического элемента ТТЛ, исследование работы логических элементов в статическом и динамическом режимах.

Краткие теоретические сведения

6.1. Основные логические операции

В разделе 5 (рис. 5.1 и 5.2) описана работа ключа на биполярном транзисторе. При подаче на вход схемы низкого уровня напряжения, транзистор закрыт, не выходе схемы появляется высокий уровень напряжения. Это соответствует разомкнутому состоянию ключа (рис. 6.1)

При подаче на вход схемы высокого уровня напряжения транзистор открывается и входит в насыщение. При этом напряжение между коллектором и эмиттером транзистора, являющееся выходным напряжением ключевой схемы, оказывается близким к нулю. Это соответствует замкнутому состоянию ключа.

Приняв условно высокий уровень напряжения U1 за "1", а низкий U0 – за "0" и обозначив через X и Y информационные значения соответственно входного и выходного сигналов, можно сказать, что рассмотренная ключевая схема реализует функцию Y= f(X), в которой X и Y принимают значения только "1" или "0". Такие функции называют логическими и часто зада-

ют в виде таблицы информационных значений сигналов X и Y - таблицы истинности.

Рассмотренная ключевая схема (рис. 6.1) реализует простейшую логическую функцию, которая называется инверсией или логическим отрицанием,

или функцией НЕ и записывается как Y = X . На рис. 6.2 приведена таблица

56

истинности и условное обозначение рассмотренной схемы как логического элемента.

|

X |

У |

|

0 |

1 |

|

1 |

0 |

Рис. 6.1 |

Рис. 6.2 |

|

В общем случае ключевая схема может иметь несколько входов mвх и реализовывать различные логические функции. Рассмотрим основные.

Логический элемент с несколькими входами Xm (m>1) и одним выходом Y называют конъюнктором или схемой умножения или логическим элементом И, если он реализует следующую логическую функцию: сигнал "1" на выходе Y имеет место тогда и только тогда, когда поданы сигналы "1" на все m входов одновременно; еcли хотя бы на один из входов подан сигнал "0", то на выходе тоже появитcя "0". Такая функция называется конъюнкцией или логическим умножением и записывается как Y = X1 X 2 Xm .

На рис. 6.3 приведена таблица истинности и условное обозначение элемента И с двумя входами.

X1 |

X2 |

Y |

|

|

|

XI |

Х2 |

|

У |

|

|

|

|

|

|

|

|

|

|||||||

0 |

0 |

0 |

|

|

|

0 |

0 |

|

0 |

|

|

|

0 |

1 |

0 |

|

|

|

0 |

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

|

|

1 |

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

|

|

|

1 |

1 |

|

1 |

|

|

|

|

|

Рис. 6.3 |

|

|

|

|

|

|

Рис. 6.4 |

|||

Логический элемент с несколькими входами Xm (m>1) и одним выхо-

дом Y называется дизъюнктором или схемой логического сложения или ло-

гическим элементом ИЛИ, если он реализует следующую логическую функцию: сигнал "1" на выходе Y имеет место, если хотя бы на одном из входов дейcтвует cигнал "1"; сигнал "0" на выходе будет только в том случае, если на все входы поданы "0". Такая функция называется дизъюнкцией или логическим сложением и записывается как Y = X1+ X 2 +... + Xm , На рис. 6.4

57

приведена таблица истинности и условное изображение элемента ИЛИ с двумя входами.

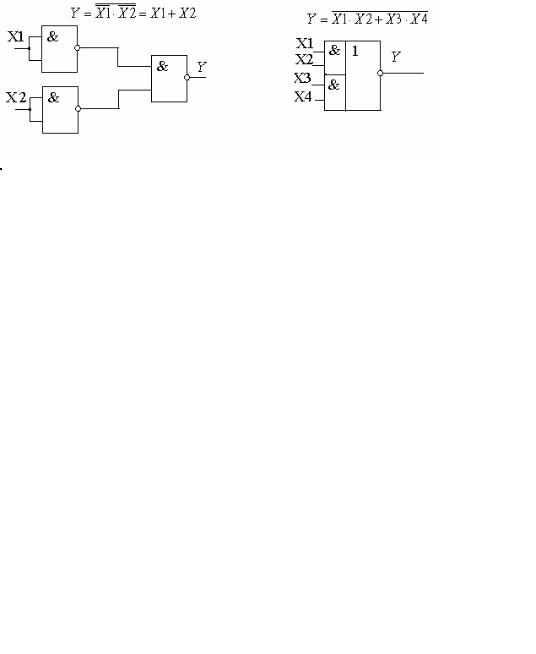

Объединяя рассмотренные логические элементы, можно получить составные логические элементы, например, И-НЕ (элемент Шеффера), ИЛИНЕ (элемент Пирса). Эти элементы реализуют соответственно логические

функции Y = X1 X 2 и Y = X1+ X 2 . Таблицы истинности и условные обозначения этих элементов приведены на рис. 6.5, б.

Логические элементы И-НЕ и ИЛИ-НЕ обладают функциональной полнотой, т.е. используя их, можно реализовать сколь угодно сложные логические функции, а также основные логические функции И, ИЛИ и НЕ.

X1 |

X2 |

Y |

|

|

0 |

0 |

1 |

|

|

0 |

1 |

1 |

|

|

1 |

0 |

1 |

|

|

1 |

1 |

0 |

|

|

|

|

|

|

|

X1 |

X2 |

Y |

|

|

|

|

|

||||

0 |

0 |

1 |

|

|

|

0 |

1 |

0 |

|

|

|

1 |

0 |

0 |

|

|

|

1 |

1 |

0 |

|

|

|

Рис. 6.5

Так, на основе элемента И-НЕ можно получить инвертор путем объединения входов этого элемента, как показано на рис. 6.6, а. Элемент И с двумя входами получается каскадным соединением элемента И-НЕ и инвертора согласно рис. 6.6, б.

|

|

|

|

б) |

|||

а) |

Рис. 6.6

|

|

Рис. 6.7 |

Рис. 6.8 |

58

Элемент ИЛИ на элементах Шеффера можно получить, используя преобразование де Моргана, согласно которому операцию ИЛИ можно заменить операцией И над инверсными значениями переменных XI и Х2, а потом проинвертировать полученную функцию (рис. 6.7).

Широко применяется также и универсальный логический элемент И- ИЛИ-НЕ, показанный на рис. 6.8. Этот элемент реализует, например для че-

тырех переменных XI, Х2, ХЗ, Х4 функцию вида Y = X1 X 2 + X 3 X 4 . Логические элементы можно реализовать на контактах реле, на дис-

кретных диодах и транзисторах и в интегральном исполнении. Интегральный логический элемент выполняется на одной подложке и конструктивно представляет собой единый модуль в герметизированном корпусе.

6.2. Передаточная характеристика логического элемента

Зависимость выходного напряжения логического элемента НЕ от входного называется передаточной характеристикой рис. 6.9.

U вых

U 1

U 0 |

U вх |

U пор0,1 |

U 1,0пор |

Рис. 6.9

На характеристике показаны уровни переключения логического элемента из состояния "1" в состояние "0" U 1пор.0 и наоборот, из состояния "0" в

состояние "1" U пор0,1 . Уровни переключения логических элементов ТТЛ различаются на сотые доли вольта, поэтому в расчетах принимают U 1.0пор =U пор0,1 =1,5 В. Для логических элементов КМОП пороговое напряже-

ние переключения принимается равным половине напряжения источника питания.

6.3. Основные параметры интегральных логических элементов

К основным параметрам интегральных логических элементов относят-

ся:

59